Дифференциальный операционный усилитель с малым напряжением смещения нуля

Иллюстрации

Показать всеИзобретение относится к области радиотехники и связи и может быть использовано в качестве устройства усиления аналоговых сигналов, в структуре аналоговых микросхем различного функционального назначения (например, в компараторах и решающих усилителях с малыми значениями эдс смещения нуля). Технический результат: уменьшение абсолютного значения Uсм, а также его температурного и радиационного дрейфа при использовании в схеме токовых зеркал, имеющих коэффициент передачи по току Ki≠1. Дифференциальный операционный усилитель с малым напряжением смещения нуля содержит первый (1) входной дифференциальный каскад (ДК) с первым (2) и вторым (3) токовыми выходами, первое (4) токовое зеркало (ТЗ), вход которого связан с первым (2) токовым выходом первого ДК (1), а выход соединен со входом буферного усилителя (5) и источником опорного тока (6), эмиттерный выход первого ТЗ (4) связан с шиной источника питания (7). В схему введен второй (8) входной ДК, первый (9) токовый выход которого соединен со входом второго ТЗ (10), а второй (11) токовый выход связан со входом первого ТЗ (4) и соединен с выходом второго ТЗ (10) и базой дополнительного транзистора (12), эмиттер которого подключен ко второму (3) токовому выходу первого ДК (1), а коллектор соединен с шиной источника питания (7). 6 ил.

Реферат

Изобретение относится к области радиотехники и связи и может быть использовано в качестве устройства усиления аналоговых сигналов, в структуре аналоговых микросхем различного функционального назначения (например, в компараторах и решающих усилителях с малыми значениями эдс смещения нуля).

В современной радиоэлектронной аппаратуре находят применение дифференциальные операционные усилители (ОУ) с существенными различными параметрами.

Особое место занимают дифференциальные операционные усилители (ОУ) с несимметричным включением активной нагрузки (токового зеркала), обеспечивающей непосредственное управление двухтактным буферным усилителем (БУ). Такие ОУ обладают важным качеством - они имеют так называемый rail-to-rail выход («от шины питания до шины питания») и предельно простую структуру. Однако ОУ данного класса [1-11] до сих пор находили применение только в устройствах с низкими требованиями к стабильности нулевого уровня, так как их напряжение смещения нуля изменяется единицами-десятками милливольт.

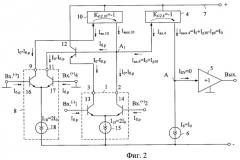

Наиболее близким по сущности к заявляемому техническому решению является классическая схема ОУ фиг.1, представленная в патенте США №4.415.868, fig. 3, которая также присутствует в большом числе других патентов и монографий, например [1-11], имеющих в качестве цепи нагрузки входных транзисторов токовые зеркала с несимметричным включением (по отношению к входному каскаду).

Существенный недостаток известного ОУ фиг.1 состоит в том, что он имеет повышенное значение систематической составляющей напряжения смещения нуля (Uсм), зависящей от погрешности передачи по току (Ki) применяемого токового зеркала. Особенно существенной эта погрешность получается при использовании в качестве токового зеркала простейших, но наиболее высокочастотных схемотехнических решений, для которых Ki≠1.

Основная задача предлагаемого изобретения состоит в уменьшении абсолютного значения Uсм, а также его температурного и радиационного дрейфа при использовании в схеме токовых зеркал, имеющих коэффициент передачи по току, не равный единице Ki≠1. Такое значение Ki характерно для многих классических токовых зеркал.

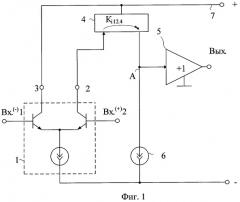

Поставленная задача достигается тем, что в дифференциальном операционном усилителе, содержащем первый 1 входной дифференциальный каскад с первым 2 и вторым 3 токовыми выходами, первое 4 токовое зеркало, вход которого связан с первым 2 токовым выходом первого 1 входного дифференциального каскада, а выход соединен со входом буферного усилителя 5 и источником опорного тока 6, эмиттерный выход первого 4 токового зеркала связан с шиной источника питания 7, предусмотрены новые элементы и связи - в схему введен второй 8 входной дифференциальный каскад, первый 9 токовый выход которого соединен со входом второго 10 токового зеркала, а второй 11 токовый выход связан со входом первого 4 токового зеркала и соединен с выходом второго 10 токового зеркала и базой дополнительного транзистора 12, эмиттер которого подключен ко второму 3 токовому выходу первого 1 входного дифференциального каскада, а коллектор соединен с шиной источника питания 7.

Схема усилителя-прототипа показана на фиг.1. На фиг.2 представлена схема заявляемого устройства, соответствующая формуле изобретения.

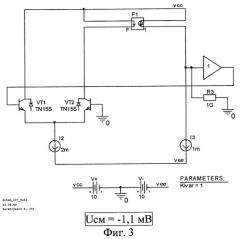

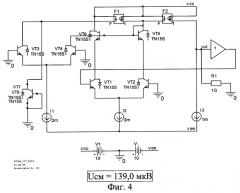

На фиг.3 и фиг.4 показаны схемы ОУ-прототипа (фиг.3) и заявляемого ОУ (фиг.4) в среде компьютерного моделирования PSpice на моделях интегральных транзисторов ФГУП НПП «Пульсар».

На фиг.5 показаны зависимости напряжения смещения прототипа и заявляемой схемы от коэффициента передачи по току Ki токовых зеркал 4 и 10 Ki=Ki12.4=Ki12.10.

На фиг.6 приведена температурная зависимость модуля напряжения смещения нуля схемы фиг.4.

Заявляемый дифференциальный операционный усилитель содержит первый 1 входной дифференциальный каскад с первым 2 и вторым 3 токовыми выходами, первое 4 токовое зеркало, вход которого связан с первым 2 токовым выходом первого 1 входного дифференциального каскада, а выход соединен со входом буферного усилителя 5 и источником опорного тока 6, эмиттерный выход первого 4 токового зеркала связан с шиной источника питания 7. В схему введен второй 8 входной дифференциальный каскад, первый 9 токовый выход которого соединен со входом второго 10 токового зеркала, а второй 11 токовый выход связан со входом первого 4 токового зеркала и соединен с выходом второго 10 токового зеркала и базой дополнительного транзистора 12, эмиттер которого подключен ко второму 3 токовому выходу первого 1 входного дифференциального каскада, а коллектор соединен с шиной источника питания 7.

Первый 1 и второй 8 входные дифференциальные каскады в схеме фиг.2 реализованы соответственно на транзисторах 13, 14, двухполюснике 15, а также на транзисторах 16, 17 и двухполюснике 18.

Рассмотрим факторы, определяющие систематическую составляющую напряжения смещения нуля (Uсм) в схеме фиг.2, т.е. зависящие от схемотехники ОУ.

Если величины токов двухполюсников 15 и 18 первого 1 и второго 8 входных дифференциальных каскадов равны 2I0, а ток источника опорного тока 6 - величине I0, то токи коллекторов транзисторов 13, 14, 16, 17 первого 1 и второго 8 входных дифференциальных каскадов определяются соотношениями:

где Iб.р=I0/βi - ток базы i-го n-p-n транзистора схемы при токе эмиттера Iэ=I0,

βi - коэффициент усиления по току базы i-го транзистора.

Выходной ток второго 10 токового зеркала определяется как

где Ip10 - разность токов на выходе и входе второго 10 токового зеркала, зависящая от его схемотехники.

Поэтому на основании закона Кирхгофа в узле A1 выполняется следующее токовое соотношение

Как следствие, токи на входе и выходе первого 4 токового зеркала определяются по формулам:

где Ip4 - разность токов на входе и выходе первого 4 токового зеркала, зависящая от его схемотехники.

Так как токовые зеркала 4 и 10 выполнены с использованием идентичных схемотехнических решений, то разность их токов ошибки Iр равна нулю. Поэтому разностный ток I∑ в узле «А» при его коротком замыкании на эквипотенциальную общую шину при IБУ≈0 будет равен нулю:

Таким образом, в заявляемом устройстве при выполнении условия (6) уменьшается систематическая составляющая Uсм, обусловленная конечной величиной β транзисторов и его радиационной (или температурной) зависимостью. Как следствие, это уменьшает Uсм, так как разностный ток I∑ в узле «А» создает Uсм, зависящее от крутизны S преобразования входного дифференциального напряжения uвх в разностный ток узла «А»:

где rэ13=rэ14 - сопротивления эмиттерных переходов входных транзисторов 13 и 14 первого 1 входного дифференциального каскада.

Поэтому для схемы фиг.2 напряжение смещения нуля

где φт=26 мВ - температурный потенциал.

В ОУ-прототипе I∑≠0. Поэтому здесь систематическая составляющая Uсм получается как минимум на порядок больше, чем в заявляемой схеме.

Компьютерное моделирование схем фиг.3, фиг.4 подтверждает (фиг.5, фиг.6) данные теоретические выводы.

Несмотря на существенное уменьшение β транзисторов вследствие радиационных и тепловых воздействий предлагаемый ОУ и в этих условиях имеет меньшее напряжение смещения нуля, чем ОУ-прототип.

В ряде случаев в заявляемом ОУ могут использоваться входы второго 8 входного дифференциального каскада (Вх.(-)3, Вх.(+)4), что позволяет реализовать на его основе так называемые мультидифференциальные ОУ, имеющие большие перспективы применения в микросхемотехнике.

Таким образом, заявляемое устройство обладает существенными преимуществами в сравнении с прототипом по величине статической ошибки усиления сигналов постоянного тока и может использоваться в качестве IP-модулей современных систем на кристалле.

БИБЛИОГРАФИЧЕСКИЙ СПИСОК

1. Патент США №4.415.868, fig.3.

2. Патент ФРГ №2928841, fig.3.

3. Патент Японии JP 54-34589, кл. 98(5) А014.

4. Патент Японии JP 154-10221, кл. H03F 3/45.

5. Патент Японии JP 54-102949, кл. 98(5) А21.

6. Патент США №4.366.442, fig.2.

7. Патент США №6.426.678.

8. Патентная заявка США 2007/0152753, fig.5c.

9. Патент США №6.531.920, fig.4.

10. Патент США №4.262.261.

11. Ежков Ю.А. Справочник по схемотехнике усилителей. - 2-е изд., перераб. - М.: ИП РадиоСофт, 2002. - 272 с. - Рис.9.3 (стр.235).

Дифференциальный операционный усилитель с малым напряжением смещения нуля, содержащий первый (1) входной дифференциальный каскад с первым (2) и вторым (3) токовыми выходами, первое (4) токовое зеркало, вход которого связан с первым (2) токовым выходом первого (1) входного дифференциального каскада, а выход соединен со входом буферного усилителя (5) и источником опорного тока (6), эмиттерный выход первого (4) токового зеркала связан с шиной источника питания (7), отличающийся тем, что в схему введен второй (8) входной дифференциальный каскад, первый (9) токовый выход которого соединен со входом второго (10) токового зеркала, а второй (11) токовый выход связан со входом первого (4) токового зеркала и соединен с выходом второго (10) токового зеркала и базой дополнительного транзистора (12), эмиттер которого подключен ко второму (3) токовому выходу первого (1) входного дифференциального каскада, а коллектор соединен с шиной источника питания (7).