Цифровой синтезатор частот

Иллюстрации

Показать всеИзобретение относится к радиотехнике и может использоваться в приемопередающей и контрольно-измерительной аппаратуре. Техническим результатом является повышение разрешающей способности и расширение диапазона при формировании мелкой сетки частот внутри заданной сетки с сохранением высокого быстродействия и чистоты спектра выходного сигнала. Цифровой синтезатор частот содержит опорный генератор, два делителя с фиксированным коэффициентом деления, инвертирующий сумматор, инвертор, два делителя с переменным коэффициентом деления, три фильтра нижних частот, два управляемых генератора, два частотно-фазовых детектора и микроконтроллер, а также дополнительно введенные цифровой потенциометр (31), повторитель напряжения (32), индикатор синхронизма (33), ключ (34), первый (35) и второй (36) компараторы напряжений. 4 ил.

Реферат

Изобретение относится к радиотехнике и может быть использовано в приемопередающей и контрольно-измерительной аппаратуре.

Широко известен цифровой синтезатор частот (ЦСЧ), построенный на основе кольца импульсно-фазовой автоподстройки частоты (ИФАПЧ) с делителем частоты с переменным коэффициентом деления (ДПКД) в цепи обратной связи (см., например, Губернаторов О.И. и Соколов Ю.Н. Цифровые синтезаторы частот радиотехнических систем. М.: «Энергия», 1973).

Недостаток таких схем синтезаторов состоит в том, что в однокольцевом ЦСЧ с целочисленным ДПКД невозможно выбрать частоту сравнения Fcp вышезаданного шага сетки частот Fш, что значительно ограничивает быстродействие синтезатора при переключении частот, особенно при мелком шаге.

Известен также цифровой синтезатор частот (см. авторское свидетельство СССР №1510080 от 23.09.1989 г.), построенный на основе двух параллельно включенных колец ИФАПЧ с общим управляемым генератором (УГ).

В этом ЦСЧ параллельно основному (узкополосному) кольцу автоподстройки включено дополнительное (широкополосное) кольцо автоподстройки. Дополнительное кольцо на основе фазового детектора (ФД) типа «выборка-запоминание» работает на частоте сравнения FCP в n раз больше заданного шага сетки частот FШ, а в основном кольце с использованием цифрового частотно-фазового детектора (ЧФД) частота сравнения FCP не более заданного шага сетки частот FШ. Управляющие сигналы с выходов ФД и ЧФД после фильтрации поступают на соответствующие входы сумматора со взвешенным суммированием, с выхода которого сформированный таким образом сигнал приходит на управляющий вход УГ.

Недостаток этого ЦСЧ состоит в том, что в нем быстродействие ограничено из-за использования разных детекторов: ЧФД и ФД типа «выборка-запоминание».

Наиболее близким по технической сущности к предлагаемому является двухкольцевой ЦСЧ с частотной модуляцией по патенту 85769, принятый за прототип.

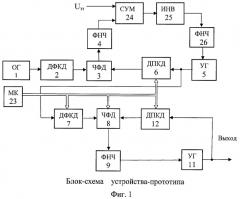

Блок-схема устройства-прототипа приведена на фиг.1, где введены следующие обозначения:

1 - опорный генератор (ОГ);

2 и 7 - первый и второй делители частоты с фиксированным коэффициентом деления (ДФКД);

3 и 8 - первый и второй частотно-фазовые детекторы (ЧФД);

4, 9 и 26 - первый, второй и третий фильтры нижних частот (ФНЧ);

5 и 11 - первый и второй управляемые генераторы (УТ);

6 и 12 - первый и второй делители частоты с переменным коэффициентом деления (ДПКД);

23 - микроконтроллер (МК);

24 - инвертирующий сумматор (СУМ);

25 - инвертор (ИНВ).

Устройство-прототип содержит последовательно соединенные опорный генератор ОГ 1, первый ДФКД 2, первый ЧФД 3, первый ФНЧ 4, инвертирующий сумматор СУМ 24, инвертор ИНВ 25, третий ФНЧ 26, первый управляемый генератор УГ 5 и первый ДПКД 6, выход которого соединен со вторым входом первого ЧФД 3; последовательно соединенные второй ДФКД 7, второй ЧФД 8, второй ФНЧ 9, второй УГ 11 и второй ДПКД 12, выход которого соединен со вторым входом второго ЧФД 8; кроме того, выход второго УГ 11 является выходом устройства, при этом выход первого УГ 5 соединен с входом второго ДФКД 7, а также микроконтроллер МК 23, управляющая шина которого соединена с управляющими входами второго ДФКД 7, второго ЧФД 8, первого ДПКД 6 и второго ДПКД 12.

Инвертирующий сумматор 24 (см. фиг.2) представляет собой усилитель-сумматор, который содержит операционный усилитель 27, первый 28, второй 29 и третий 30 резисторы.

Устройство-прототип работает следующим образом.

В ЦСЧ функционируют два последовательно соединенных кольца ИФАПЧ. На выходе первого кольца формируется одна частота, которая является опорной для второго кольца. Во втором кольце синтезируются выходные частоты ЦСЧ в заданном диапазоне и с заданным шагом сетки частот.

В первом кольце ИФАПЧ на первый вход СУМ 24 поступает хорошо отфильтрованное эталонное напряжение UЭТ, равное или немного меньше половины максимального управляющего напряжения на управляющем входе УГ 5, т.е. UЭТ≤0,5 UУПР. На второй вход СУМ 24 с выхода первого ЧФД 3 через первый ФНЧ 4 поступает соответствующее управляющее напряжение U2, которое формируется в процессе вхождения в синхронизм в первом кольце ИФАПЧ.

При этом суммарное управляющее напряжение с выхода СУМ 24 через ИНВ 25 и третий ФНЧ 26 поступает на управляющий вход УГ 5 и равно взвешенной сумме управляющих напряжений с выходов первого ФНЧ 4 и источника эталонного напряжения UЭТ

Весовой коэффициент n выбирается из следующих соображений.

Коэффициент усиления многовходового усилителя-сумматора (построенного на основе операционного усилителя 27 с заземленным неинвертирующим входом, см. фиг.2) определяется по каждому j-входу как

где Roc - сопротивление обратной связи операционного усилителя,

Rj - сопротивление соответствующего резистора.

С помощью резисторов, включенных во входную цепь усилителя-сумматора, можно реализовать весовые коэффициенты для каждого из слагаемых напряжений, если принять, что первый резистор 28 равен третьему резистору 30 (в обратной связи), а второй резистор 29 равен R2=n R1,

где R2 - сопротивление второго резистора 29,

R1 - сопротивление первого резистора 28.

Каждому значению суммарного управляющего напряжения UΣ на управляющем входе УГ 5 соответствует определенная частота на его выходе.

Если выбрать частоту опорных импульсов (т.е. частоту сравнения Fcp) в первом кольце в n раз больше заданного шага мелкой сетки частот, то при переключении коэффициента деления первого ДПКД 6 на единицу напряжение на выходе ЧФД 3 будет в n раз больше, чем в том случае, если бы частота сравнения была равна шагу мелкой сетки частот. Тогда после первого же периода регулирования в первом кольце управляющее напряжение на выходе ЧФД 3 изменится на величину ΔU2=nΔU1, где ΔU1 - изменение управляющего напряжения, которое было бы на выходе ЧФД 3, если бы частота сравнения была бы равна мелкому шагу сетки частот. Тогда после первого же периода регулирования суммарное управляющее напряжение УГ 5 станет равно

т.е. изменится на величину ΔU1, как и требовалось для заданного мелкого приращения частоты Δf (шага мелкой сетки частот).

Иначе говоря, во сколько раз увеличили частоту сравнения Fcp в первом кольце (т.е. в n раз), во столько раз увеличилось управляющее напряжение U2 после первого ФНЧ 4 при переключении коэффициента деления первого ДПКД 6 на единицу. При этом во столько же раз уменьшилось это напряжение после инвертирующего сумматора СУМ 24 в составе суммарного управляющего напряжения, которое через ИНВ 25 и четвертый ФНЧ 26 поступает на управляющий вход УГ 5. Третий ФНЧ 26 необходим для дополнительной фильтрации суммарного управляющего напряжения.

Здесь фиксированное напряжение UЭТ играет роль «подставки», относительно которой происходит изменение управляющего напряжения с мелким шагом, что приводит к более тонкой подстройке номинального значения выходной частоты УГ 5.

Таким образом, в первом кольце ИФАПЧ получается выигрыш по быстродействию из-за того, что подстройка управляющего напряжения осуществляется в n раз чаще, чем если бы частота сравнения Fcp была равна частоте мелкого шага. В то же время подстройка выходной частоты первого кольца происходит с мелким шагом в окрестности ее номинального значения. Кроме того, поскольку на выходе инвертирующего сумматора СУМ 24 управляющее напряжение уменьшается в n раз, также в n раз уменьшается уровень помехи с частотой сравнения с выхода ЧФД 4. Это дает возможность уменьшить фильтрацию на выходе первого ФНЧ 4 и тем самым дополнительно повысить быстродействие.

С выхода УГ 5 опорная частота поступает на вход второго ДФКД 7 для формирования опорной частоты сравнения во втором кольце ЦСЧ. В результате на выходе второго УГ 11 формируются выходные частоты ЦСЧ в заданном диапазоне и с заданным шагом сетки частот с возможностью минимального частотного сдвига внутри заданной сетки.

Недостатки устройства-прототипа следующие.

В синтезаторе-прототипе из-за необходимости иметь мелкий шаг перестройки по частоте в первом кольце получается малый диапазон перекрытия по управляющему напряжению на входе УГ 5. Например, если принять весовой коэффициент n=20, а максимальный перепад управляющего напряжения на выходе ЧФД 3 ΔUЧФД≤10 В, то максимальный диапазон перекрытия по управляющему напряжению на входе УГ будет ΔUУУГ=10В:20=0,5 В или вместе с постоянным напряжением UЭТ суммарное управляющее напряжение на управляющем входе УГ 5 будет ΔUУГ=UЭТ+0,5 В. При этом минимальный шаг перестройки на выходе первого кольца при частоте сравнения FCP=12,5 кГц и n=20 будет FШ=12,5 кГц:20=0,625 кГц, а при n=100 минимальный шаг составит FШ=12,5 кГц:100=0,125 кГц. Из этих сравнений видно, что чем больше n, тем больше разрешающая способность по частоте (т.е. более мелкий шаг) и тем меньше диапазон перекрытия по управляющему напряжению на входе УГ 5. При очень малом диапазоне перекрытия и неблагоприятных условиях работы ЦСЧ кольцо ИФАПЧ может выйти из синхронизма. Чтобы этого не произошло, нужно увеличивать диапазон перекрытия по управляющему напряжению на входе УГ 5. Но в этом случае разрешающая способность по частоте станет недостаточной, т.е. получить необходимый мелкий шаг будет затруднительно.

Задачей, на которую направлено заявляемое устройство, является создание устройства с повышенной разрешающей способностью по частоте, при этом с одновременным увеличением диапазона перекрытия по частоте.

Для решения поставленной задачи в цифровой синтезатор частот, содержащий последовательно соединенные опорный генератор, первый делитель частоты с фиксированным коэффициентом деления, первый частотно-фазовый детектор, первый фильтр нижних частот, инвертирующий сумматор, инвертор, третий фильтр нижних частот, первый управляемый генератор и первый делитель частоты с переменным коэффициентом деления, выход которого соединен со вторым входом первого частотно-фазового детектора; последовательно соединенные второй делитель частоты с фиксированным коэффициентом деления, второй частотно-фазовый детектор, второй фильтр нижних частот, второй управляемый генератор и второй делитель частоты с переменным коэффициентом деления, выход которого соединен со вторым входом второго частотно-фазового детектора, при этом выход второго управляемого генератора является выходом устройства, выход первого управляемого генератора соединен с входом второго делителя частоты с фиксированным коэффициентом деления, а также микроконтроллер, выход которого управляющей шиной соединен с управляющими входами второго делителя частоты с фиксированным коэффициентом деления, второго частотно-фазового детектора, первого и второго делителей частоты с переменным коэффициентом деления, согласно изобретению введены последовательно соединенные цифровой потенциометр и повторитель напряжения, выход которого соединен со вторым входом инвертирующего сумматора, а также последовательно соединенные индикатор синхронизма и ключ, выход которого соединен с входами первого и второго компараторов, выходы которых соединены с соответствующими входами микроконтроллера, выход которого управляющей шиной соединен с управляющим входом цифрового потенциометра, сигнальный вход которого является входом эталонного напряжения, кроме того, вход индикатора синхронизма соединен со вторым выходом первого частотно-фазового детектора, сигнальный вход ключа соединен с выходом первого фильтра нижних частот.

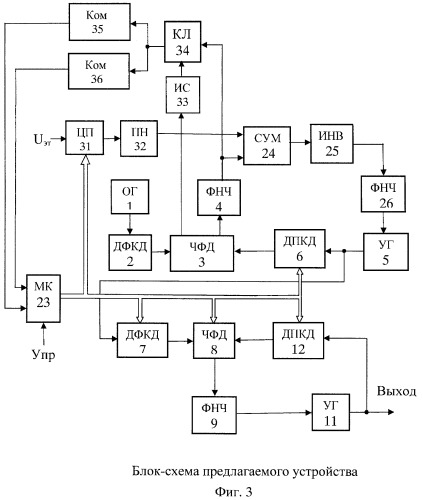

Блок-схема предлагаемого устройства приведена на фиг.3, где введены следующие обозначения:

1 - опорный генератор (ОГ);

2 и 7 - первый и второй делители частоты с фиксированным коэффициентом деления (ДФКД);

3 и 8 - первый и второй частотно-фазовые детекторы (ЧФД);

4, 9 и 26 - первый, второй и третий фильтры нижних частот (ФНЧ);

5 и 11 - первый и второй управляемые генераторы (УГ);

6 и 12 - первый и второй делители частоты с переменным коэффициентом деления (ДПКД);

23 - микроконтроллер (МК);

24 - инвертирующий сумматор (СУМ);

25 - инвертор (ИНВ);

31 - цифровой потенциометр (ЦП);

32 - повторитель напряжения (ПН);

33 - индикатор синхронизма (ИС);

34 - ключ (КЛ);

35 - первый компаратор (Ком);

36 - второй компаратор (Ком).

Предлагаемое устройство содержит первое кольцо ИФАПЧ на основе последовательно соединенных: ОГ 1, первого ДФКД 2, первого ЧФД 3, первого ФНЧ 4, СУМ 24, ИНВ 25, третьего ФНЧ 26, первого УГ 5 и первого ДПКД 6, выход которого соединен со вторым входом первого ЧФД 3; второе кольцо ИФАПЧ на основе последовательно соединенных: второго ДФКД 7, второго ЧФД 8, второго ФНЧ 9, второго УГ 11 и второго ДПКД 12, выход которого соединен со вторым входом второго ЧФД 8, а также последовательно соединенные ЦП 31 и ПН 32, выход которого соединен со вторым входом СУМ 24, последовательно соединенные индикатор синхронизма ИС 33 и КЛ 34, выход которого соединен с входами первого Ком 35, второго Ком 36, выходы которых соединены с соответствующими входами микроконтроллера МК 23, выход которого управляющей шиной соединен с управляющими входами второго ДФКД 7, второго ЧФД 8, первого ДПКД 6, второго ДПКД 12 и ЦП 31. При этом выход первого УГ 5 соединен с входом второго ДФКД 7, а выход второго УГ 11 является выходом устройства. Вход ЦП 31 является входом эталонного напряжения UЭТ. Вход ИС 33 соединен со вторым выходом первого ЧФД 3. Сигнальный вход КЛ 34 соединен со вторым выходом первого ФНЧ.

Управляющая шина с выхода МК 23 представляет собой стандартный трехпроводный интерфейс, где по трем проводам поступают в последовательном коде импульсные сигналы: 1) тактовые импульсы (ТИ); 2) информационный сигнал (ИНФ); 3) импульс разрешения записи (ИЗ) передаваемой информации в каждый из блоков: ДПКД 12, ДПКД 6, ЧФД 8, ДФКД 7, ЦП 31. Причем для всех блоков общими проводами являются ТИ и ИНФ, а импульс разрешения прохождения информации поступает по каждому отдельному проводу в каждый управляемый блок.

Инвертирующий сумматор СУМ 24 (см. фиг.2) идентичен СУМ 24 в прототипе и содержит операционный усилитель 27, первый 28, второй 29 и третий 30 резисторы.

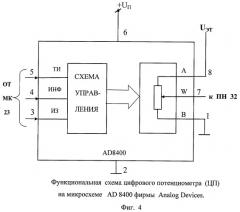

Цифровой потенциометр ЦП 31 на одноканальной микросхеме AD8400 фирмы Analog Devices представляет собой (см. фиг.4) устройство для декодирования входных величин, выраженных в двоичном коде, в соответствующие им значения сопротивлений на выходе. Цифровой потенциометр на микросхеме AD8400 может выполнять в аппаратуре разные функции, в том числе и функцию обычного переменного сопротивления и потенциометра, с выхода которого можно получать 256 дискретных значений напряжений от одного эталонного источника UЭТ. Номинальные значения сопротивлений микросхем AD8400 могут быть 1 кОм, 10 кОм, 50 кОм и 100 кОм. На выходе ЦП 31 могут устанавливаться 256 программируемых дискретных значений номинального сопротивления. Это выходное переменное сопротивление RЦП цифрового потенциометра может являться в данном случае частью входного сопротивления операционного усилителя (фиг.2), на основе которого выполнен сумматор со взвешенным суммированием. Потому коэффициент усиления операционного усилителя (ОУ) можно представить следующим образом

где R1 - сопротивление на первом входе сумматора,

RЦП - переменное сопротивление цифрового потенциометра.

Из (4) видно, что при изменении RЦП на выходе ЦП изменяется коэффициент усиления ОУ и нарушается в данном случае правильная работа сумматора со взвешенным суммированием. Чтобы этого не произошло, после ЦП 31 включен повторитель напряжения ПН 32 с очень высоким входным импедансом и очень низким стабильным выходным сопротивлением RПН<<R1. В связи с этим RПН можно не учитывать и коэффициент усиления ОУ можно представить, как и прежде, выражением

Повторитель напряжения ПН 32 может быть выполнен на основе эмиттерного повторителя или на основе операционного усилителя.

Предлагаемое устройство работает следующим образом.

В предлагаемом ЦСЧ функционируют два последовательно соединенных кольца ИФАПЧ. На выходе первого кольца формируется одна частота, которая является опорной для второго кольца. Причем эта частота, при необходимости, может иметь фиксированные отстройки в окрестности номинального значения. Во втором кольце синтезируются выходные частоты ЦСЧ в заданном диапазоне и с заданным шагом сетки частот, а внутри заданного шага можно получать отстройки от номинального значения частоты с мелким шагом.

Для этого в первом кольце ИФАПЧ на первый вход инвертирующего сумматора СУМ 24 через последовательно соединенные ЦП 31 и ПН 32 поступают 256 переключаемых дискретных равных и стабильных градаций эталонного напряжения, т.е. переменное эталонное напряжение может изменяться от UПЕР ЭТ 1=UЭТ/256 до UПЕР ЭТ 256=UЭТ с шагом (градацией) m. На второй вход СУМ 24 с выхода первого ФНЧ 4 поступает соответствующее управляющее напряжение U2, которое формируется в процессе вхождения в синхронизм в первом кольце ИФАПЧ.

При этом суммарное управляющее напряжение UΣ с выхода СУМ 24 через ИНВ 25 и третий ФНЧ 26 поступает на управляющий вход УГ 5 и равно взвешенной сумме управляющих напряжений с выходов первого ФНЧ 4 и переменного эталонного напряжения с выхода ПН 32

Весовой коэффициент n в инвертирующем сумматоре СУМ 24, где осуществляется взвешенное суммирование двух входных сигналов, выбирается так же, как это описано в прототипе.

Здесь переменное напряжение UЭТ/m играет роль «подставки», относительно которой происходит изменение управляющего напряжения в первом кольце ИФАПЧ с мелким шагом, что приводит к более тонкой подстройке номинального значения выходной частоты УГ 5.

В начале по сигналу управления от МК 23 устанавливается напряжение «подставки» в середине UЭТ и равно UЭТ/128, а на управляющий вход первого УГ 5 после третьего ФНЧ 26 поступает суммарное управляющее напряжение

В этом случае формируется номинальное значение частоты на выходе УГ 5. Одновременно на выходе ИС 33 появляется сигнал наличия синхронизма в первом кольце ИФАПЧ с уровнем «Лог.1», который поступает на управляющий вход КЛ 34 и разрешает в режиме синхронизма прохождение через КЛ 34 сигнала с выхода первого ФНЧ 4 на входы первого Ком 35 и второго Ком 36. На оба компаратора поступает один и тот же сигнал. Первый Ком 35 сравнивает входной сигнал с опорным напряжением UОП ВЕРХ таким образом, что на выходе его будет «Лог.1», когда входной сигнал превышает UОП ВЕРХ. Второй Ком 36, включенный инверсно, сравнивает тот же входной сигнал с опорным напряжением UОП НИЖН таким образом, что на выходе его будет «Лог.1», когда входной сигнал меньше, чем UОП НИЖН. Иначе говоря, схема с двумя компараторами способна чувствовать момент, когда входной сигнал выходит из заданной допустимой области (рабочего окна). Когда входной сигнал находится в допустимой области, на выходах первого Ком 35 и второго Ком 36 имеются сигналы «Лог.0». Сигнал «Лог.0» с выхода первого Ком 35 поступает на первый вход МК 23, а сигнал «Лог.0» с выхода первого Ком 36 поступает на второй вход МК 23. Когда на оба входа МК 23 поступают сигналы с уровнем «Лог.0», это означает, что управляющее напряжение U2 с выхода первого ФНЧ 4 находится в допустимой области и до верхнего предела UОП ВЕРХ и нижнего предела UОП НИЖН управляющих напряжений после первого ФНЧ 4 есть еще установленный запас.

Если при этом есть необходимость отстроиться от номинального значения частоты в первом кольце на некоторую дискретную величину путем соответствующего изменения коэффициента деления в первом ДПКД 6, то управляющее напряжение на выходе первого ФНЧ 4 изменится соответственно от номинального значения при сохранении прежнего значения напряжения подставки UЭТ/128. Если при дальнейшей отстройке частоты УГ 5 напряжение с первого входа ФНЧ 4 будет больше UОП ВЕРХ или меньше UОП НИЖН, на выходе соответствующего компаратора появится сигнал «Лог.1» и поступит на соответствующий вход МК 23. В результате с выхода МК 23 по управляющей шине поступит сигнал в двоичном коде на управляющий вход ЦП 31, от которого в ЦП 31 произойдет переключение на одну ступеньку напряжения (градацию) вверх или вниз от номинального значения. Уже с этой новой «подставки» кольцо ИФАПЧ быстро подстроится и будет находиться в состоянии синхронизма на новой частоте, отстроенной от номинальной.

Следовательно, с помощью этих автоматически переключаемых «подставок» можно и дальше отстраиваться по частоте от номинального значения вверх или вниз, т.е. диапазон перестройки частот с мелкой сеткой в первом кольце значительно расширяется.

При этом одна дискретная градация «подставки» по величине должна быть меньше максимального перекрытия по управляющему напряжению U2/n на входе УГ 5 от первого кольца ИФАПЧ.

От суммарного управляющего напряжения UΣ формируется на выходе первого УГ 5 частота, которая в качестве опорной поступает во второе кольцо на вход второго ДФКД 7. Во втором кольце по сигналам, поступающим от МК 23 по управляющей шине на управляющие входы второго ДФКД 7, второго ЧФД 8 и второго ДПКД 12, на выходе УГ 11 формируются выходные частоты синтезатора в заданном диапазоне с заданным шагом с возможностью мелкой отстройки внутри заданного шага в широких пределах. В переходном режиме ток на выходе второго ЧФД 8 резко увеличивается по сигналам управления от МК 23, чтобы повысить быстродействие при переключении частот. В режиме синхронизма ток ЧФД 8 опять уменьшается до минимального для улучшения подавления побочных составляющих в выходном сигнале ЦСЧ.

Возможность осуществления предлагаемого устройства определяется тем, что вводимые блоки типовые и могут быть выполнены на широко известных микросхемах. Цифровая часть синтезаторов выполняется на микросхемах ЦСЧ с ИФАПЧ разных фирм. При этом в одной микросхеме могут быть один или два независимых ЦСЧ с целочисленным ДПКД (Integer-N) или с дробным (Fractional-N). Например, микросхемы LMX2364, LMX 2470 фирмы National Semiconductor представляют собой двойной синтезатор с двумя раздельными контурами регулирования: один с дробным ДПКД (ДДПКД), другой - с обычным. Аналогично этому микросхемы ADF4252, ADF4001 фирмы Analog Devices и другие. Индикаторы синхронизма ИС обычно входят в состав этих микросхем, а выходной сигнал ИС формируется от информации, поступающей со второго выхода ЧФД. Эти ИС бывают двух типов: цифровой и аналоговый. Цифровой ИС работает так, что если в трех (или пяти) последовательных циклах измерения фазовое рассогласование между импульсами двух потоков импульсов на входах ЧФД меньше 15 нсек, то имеется синхронизм в кольце ФАПЧ и на выходе цифрового ИС формируется уровень Лог.1. Если фазовая ошибка больше 25 нсек в одном цикле измерения, то синхронизма нет, и на выходе цифрового ИС формируется уровень Лог.0. В качестве инвертирующего сумматора и инвертора могут использоваться малошумящие операционные усилители, например, типа ОР 27 фирмы Analog Devices. Цифровой потенциометр может быть выполнен на микросхеме AD8400 фирмы Analog Devices. Повторитель напряжения может быть выполнен на основе малошумящего эмиттерного повторителя или на основе повторителя напряжения на операционном усилителе типа ОР 27 фирмы Analog Devices. Компараторы напряжений могут быть выполнены, например, на отечественной микросхеме 521 СА3. Ключевые устройства могут быть выполнены на микросхеме МС14053 В фирмы Motorolla. В качестве микроконтроллера МК 23 может использоваться микросхема C8051F220 фирмы Silicon Laboratories (CYGNAL).

Таким образом, в предлагаемом ЦСЧ диапазон перестройки частот с мелкой сеткой в первом кольце значительно расширяется из-за того, что множество напряжений «подставок» автоматически переключается в широких пределах, что также повышает надежность синхронизации.

Кроме того, из-за высокой частоты сравнения в первом кольце, которая формируется без использования дробного ДПКД с известными «помехами дробности», имеется возможность получить более высокую чистоту спектра выходного сигнала при сохранении высокого быстродействия.

Цифровой синтезатор частот, содержащий последовательно соединенные опорный генератор, первый делитель частоты с фиксированным коэффициентом деления, первый частотно-фазовый детектор, первый фильтр нижних частот, инвертирующий сумматор, инвертор, третий фильтр нижних частот, первый управляемый генератор и первый делитель частоты с переменным коэффициентом деления, выход которого соединен со вторым входом первого частотно-фазового детектора; последовательно соединенные второй делитель частоты с фиксированным коэффициентом деления, второй частотно-фазовый детектор, второй фильтр нижних частот, второй управляемый генератор и второй делитель частоты с переменным коэффициентом деления, выход которого соединен со вторым входом второго частотно-фазового детектора, при этом выход второго управляемого генератора является выходом устройства, выход первого управляемого генератора соединен с входом второго делителя частоты с фиксированным коэффициентом деления, а также микроконтроллер, выход которого управляющей шиной соединен с управляющими входами второго делителя частоты с фиксированным коэффициентом деления, второго частотно-фазового детектора, первого и второго делителей частоты с переменным коэффициентом деления, отличающийся тем, что введены последовательно соединенные цифровой потенциометр и повторитель напряжения, выход которого соединен со вторым входом инвертирующего сумматора, а также последовательно соединенные индикатор синхронизма и ключ, выход которого соединен с входами первого и второго компараторов, выходы которых соединены с соответствующими входами микроконтроллера, выход которого управляющей шиной соединен с управляющим входом цифрового потенциометра, сигнальный вход которого является входом эталонного напряжения, кроме того, вход индикатора синхронизма соединен со вторым выходом первого частотно-фазового детектора, сигнальный вход ключа соединен с выходом первого фильтра нижних частот.