Адресный идентификатор

Иллюстрации

Показать всеАдресный идентификатор предназначен для определения адреса наименьшего или наибольшего из n аналоговых сигналов и может быть использован в аналоговых вычислительных машинах, процессорах, средствах автоматического регулирования и управления. Техническим результатом является сокращение аппаратурного состава устройства и упрощение его настройки. Устройство содержит n компараторов, n элементов ИСКЛЮЧАЮЩЕЕ ИЛИ, регистр, n размыкающих ключей, элемент И. 1 ил.

Реферат

Изобретение относится к автоматике и аналоговой вычислительной технике и может быть использовано для построения функциональных узлов аналоговых вычислительных машин, средств автоматического регулирования и управления, аналоговых процессоров и др.

Известны адресные идентификаторы (см., например, патент РФ 2143740, кл. G06G 7/25, 1999 г.), которые выполняют адресную идентификацию наименьшего или наибольшего из трех аналоговых сигналов.

К причине, препятствующей достижению указанного ниже технического результата при использовании известных адресных идентификаторов, относятся ограниченные функциональные возможности, обусловленные тем, что не допускается обработка n аналоговых сигналов.

Наиболее близким устройством того же назначения к заявленному изобретению по совокупности признаков является принятый за прототип адресный идентификатор (патент РФ 2204163, кл. G06G 7/25, 2003 г.), который содержит элемент И, n компараторов, n элементов ИСКЛЮЧАЮЩЕЕ ИЛИ, n размыкающих ключей, регистр и выполняет адресную идентификацию наименьшего или наибольшего из n аналоговых сигналов.

К причине, препятствующей достижению указанного ниже технического результата при использовании прототипа, относится сложная настройка, обусловленная тем, что для ее реализации требуются два управляющих сигнала.

Техническим результатом изобретения является упрощение настройки за счет обеспечения выполнения адресной идентификации наименьшего или наибольшего из n аналоговых сигналов с помощью одного управляющего сигнала.

Указанный технический результат при осуществлении изобретения достигается тем, что в адресном идентификаторе, содержащем элемент И, n компараторов, n элементов ИСКЛЮЧАЮЩЕЕ ИЛИ, n размыкающих ключей и регистр, инвертирующие входы всех компараторов объединены, а неинвертирующий вход и выход i-го компаратора соединены соответственно с i-м информационным входом адресного идентификатора и первым входом i-го элемента ИСКЛЮЧАЮЩЕЕ ИЛИ, подсоединенного выходом к i-му входу регистра, i-й выход которого соединен с управляющим входом i-го размыкающего ключа, подсоединенного входом и выходом соответственно к i-му идентифицирующему входу и i-му выходу адресного идентификатора, настроечный вход которого образован объединенными вторыми входами всех элементов ИСКЛЮЧАЮЩЕЕ ИЛИ, особенность заключается в том, что i-й вход и выход элемента И соединены соответственно с i-м входом и входом разрешения записи регистра.

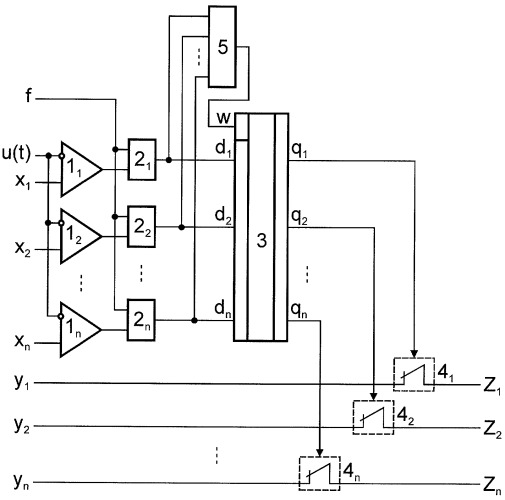

На чертеже представлена схема предлагаемого адресного идентификатора.

Адресный идентификатор содержит компараторы 11-1n, элементы ИСКЛЮЧАЮЩЕЕ ИЛИ 21-2n, регистр 3, размыкающие ключи 41-4n, элемент И 5, причем инвертирующие входы компараторов 11-1n объединены, а неинвертирующий вход и выход компаратора 11 соединены соответственно с i-м информационным входом адресного идентификатора и первым входом элемента 2i подсоединенного выходом к i-му входу элемента 5 и i-му входу регистра 3, вход разрешения записи и i-й выход которого соединены соответственно с выходом элемента 5 и управляющим входом ключа 4i, подсоединенного входом и выходом соответственно к i-му идентифицирующему входу и i-му выходу адресного идентификатора, настроечный вход которого образован объединенными вторыми входами элементов 21-2n.

Работа предлагаемого адресного идентификатора осуществляется следующим образом. Регистр 3 воспроизводит операцию

где ; qi, di ∈{0,1} и w есть сигналы соответственно на i-м выходе, i-м входе и входе разрешения записи регистра 3; есть сигнал на i-м выходе регистра 3 в момент переключения сигнала w с высокого уровня на низкий (из «1» в «0»). Указанный регистр может быть аппаратно реализован с помощью, например, микросхем К155ТМ5 или К555ИР22. На первый - n-й информационные и первый - n-й идентифицирующие входы предлагаемого адресного идентификатора подаются соответственно подлежащие обработке аналоговые сигналы (напряжения) x1-xn∈(xmin, хmax) с произвольным отношением порядка и аналоговые сигналы (напряжения) y1-yn (y1≠…≠yn); на его настроечный вход и объединенные инвертирующие входы всех компараторов подаются соответственно управляющий сигнал f∈{0,1} и линейно возрастающее либо линейно убывающее напряжение u(t)∈[xmin, xmax]. Цикл работы адресного идентификатора состоит из предварительной установки в исходное состояние и последующей обработки данных. В исходное состояние адресный идентификатор устанавливается при u(t)=xmin, f=0 (u(t)=xmax, f=1). В этом случае на всех входах регистра 3 и, следовательно, на управляющих входах ключей 41-4n присутствует логическая «1», ключи 41-4n разомкнуты и Z1=…=Zn=0. Обработка данных реализуется при линейном возрастании (линейном убывании) сигнала u(t), т.е. при , и f=0 (f=1). Здесь первым изменится с «1» на «0» (с «0» на «1») сигнал на выходе того компаратора 1i, на неинвертирующем входе которого действует наименьший (наибольший) из сигналов x1-xn. В этом случае на управляющий вход соответствующего ключа 4i и вход разрешения записи регистра 3 поступает логический «0», вызывая замыкание указанного ключа и «защелкивание» указанного регистра. С этого момента и до начала следующего цикла состояние первого - n-го выходов регистра 3 не зависит от сигналов, действующих на его первом - n-м входах. Таким образом, операция, воспроизводимая предлагаемым адресным идентификатором, определяется выражением

где ext=min при и f=0; ext=max при и f=1. Согласно (1) номер i∈{1,…,n} возбужденного выхода Zi≠0 соответствует адресу экстремального сигнала в кортеже (x1,…,xn).

Вышеизложенные сведения позволяют сделать вывод, что предлагаемый адресный идентификатор имеет более простую по сравнению с прототипом настройку, так как обеспечивает выполнение адресной идентификации наименьшего или наибольшего из n аналоговых сигналов с помощью одного управляющего сигнала.

Дополнительным достоинством предлагаемого адресного идентификатора являются меньшие по сравнению с прототипом аппаратурные затраты.

Адресный идентификатор, содержащий элемент И, n компараторов, n элементов ИСКЛЮЧАЮЩЕЕ ИЛИ, n размыкающих ключей и регистр, причем инвертирующие входы всех компараторов объединены, а неинвертирующий вход и выход i-го компаратора соединены соответственно с i-м информационным входом адресного идентификатора и первым входом i-го элемента ИСКЛЮЧАЮЩЕЕ ИЛИ, подсоединенного выходом к i-му входу регистра, i-й выход которого соединен с управляющим входом i-го размыкающего ключа, подсоединенного входом и выходом соответственно к i-му идентифицирующему входу и i-му выходу адресного идентификатора, настроечный вход которого образован объединенными вторыми входами всех элементов ИСКЛЮЧАЮЩЕЕ ИЛИ, отличающийся тем, что i-й вход и выход элемента И соединены соответственно с i-м входом и входом разрешения записи регистра.