Способ и устройство для записи высокоскоростных входных данных в матрицу запоминающих устройств

Иллюстрации

Показать всеИзобретение относится к средствам записи в запоминающие устройства. Техническим результатом является обеспечение адаптации режимов записи в зависимости от выявленных дефектов записи. Для хранения потоковых HD видеоданных используют системы на основе флэш-памяти. Физический доступ к устройствам флэш-памяти осуществляют в странично-ориентированном режиме. При этом входные данные записывают в режиме мультиплексирования в матрицу множественных флэш-устройств. Осуществляют обработку списка, и дефектные страницы блоков флэш-памяти единичных флэш-устройств адресуют в архитектуре матрицы. При записи в последовательном режиме, содержание данных для текущей страницы флэш-устройства всех флэш-устройств матрицы копируют в соответствующую область памяти в дополнительном буфере памяти. После того как текущая серия страниц записана без ошибок во флэш-устройства, соответствующую область памяти в дополнительном буфере памяти перезаписывают данными следующей страницы. В случае возникновения ошибки в текущей странице в одном или нескольких флэш-устройствах, содержание этих текущих страниц сохраняют в дополнительном буфере памяти. 2 н. и 12 з.п. ф-лы, 7 ил.

Реферат

Область техники, к которой относится изобретение

Изобретение относится к способу и устройству для записи высокоскоростных входных данных в матрицу запоминающих устройств.

Уровень техники

Для записи или воспроизведения в реальном времени широкополосных цифровых видеосигналов, например сигналов HDTV, HD progressive или HD film capture, требуются высокоскоростные запоминающие устройства. Для хранения потоковых HD видеоданных можно использовать системы на основе NAND флэш-памяти. Физический доступ к устройствам флэш-памяти осуществляется в странично-ориентированном режиме, благодаря чему одна 'страница' включает в себя, например, 1024 слов данных и соответствующий код коррекции ошибки (ecc). Операции стирания в конкретной флэш-памяти можно осуществлять только на блоках данных определенного размера. Эти блоки данных обозначаются ниже термином 'блок флэш-памяти'. Блок флэш-памяти состоит, например, из 64 страниц. Устройства флэш-памяти NAND имеют два основных недостатка:

- слишком медленный доступ для записи;

- имеют незамаскированные дефекты производства и получают еще больше дефектов в ходе эксплуатации. Необходимая обработка ошибок возлагается на пользователя. Это также справедливо для эквивалентных типов памяти.

Поскольку выявление дефектов в устройствах флэш-памяти (например, устройствах NAND) происходит, например, при выполнении операции стирания, дефект в странице делает непригодным весь блок флэш-памяти. Файловая система не должна использовать такие дефектные блоки флэш-памяти. Обработка таких дефектов полностью находится в ведении пользователя.

Известно, что для такой обработки ошибок используются избыточные коды, например код Рида-Соломона, но этот подход также страдает недостатками, например высоким динамическим расходом времени, что препятствует работе в режиме реального времени. Например, на рынке присутствуют следующие устройства флэш-памяти NAND: Samsung K9K2G16U0M-YCB000 (ориентированное на 2Гбит, 16бит), K9W4G08U0M-YCB000 (4Гбит, ориентированное на 8бит), Toshiba TH58NVG2S3BFT00 (4Гбит, ориентированное на 8бит), MICRON MT29G08AAxxx (2Гбит, ориентированное на 8бит), MT29G16AAxxx (2Гбит, ориентированное на 16бит), Samsung K9K4G08 (4Гбит, ориентированное на 8бит).

Раскрытие изобретения

Изобретение можно использовать для записи в режиме реального времени потоковых видеоданных высокого разрешения на устройства на основе NAND флэш-памяти. Использование флэш-устройств при записи в реальном времени при высокой скорости передачи данных приводит к большим файлам. Важно иметь обработку, экономичную в отношении ресурсов и производительности, для динамического перераспределения дефектов из поврежденных блоков флэш-памяти в свободные блоки флэш-памяти. Большинство современных приложений NAND-флэш имеют защиту от ошибок на основе кода Рида-Соломона и не может работать в режиме реального времени.

Задача изобретения состоит в обеспечении алгоритма, экономичного в отношении ресурсов и производительности, для перераспределения дефектов во флэш-устройствах, которые возникают в ходе работы, для поддержки низкого энергопотребления, высокого быстродействия и режима реального времени. Эта задача решается благодаря способу, раскрытому в п. 1 формулы изобретения. Устройство, использующее этот способ, раскрыто в п. 2 формулы изобретения.

Согласно изобретению, высокоскоростные входные данные записываются в режиме мультиплексирования в матрицу множественных флэш-устройств. Осуществляется максимально простая обработка списка, и дефектные страницы блоков флэш-памяти единичных флэш-устройств адресуются в архитектуре матрицы. При записи в последовательном режиме содержание данных для текущей страницы флэш-устройства всех флэш-устройств матрицы также копируется в соответствующую область памяти в дополнительном буфере памяти. После того как текущая серия страниц записана без ошибок во флэш-устройства, соответствующую область памяти в дополнительном буфере памяти можно перезаписывать данными следующей страницы. В случае возникновения ошибки в текущей странице в одном или нескольких флэш-устройствах содержание этих текущих страниц сохраняется в дополнительном буфере памяти.

В принципе, способ, отвечающий изобретению, пригоден для записи высокоскоростных входных данных в матрицу запоминающих устройств первого типа, причем матрица включает в себя, по меньшей мере, два запоминающих устройства на строку и, по меньшей мере, два запоминающих устройства на столбец, в которой запоминающие устройства строки подключены к общей шине, и каждой строке матрицы назначена отдельная общая шина, и в которой все запоминающие устройства внутренне организованы в виде множественных страниц, в каковые страницы можно записывать входные данные в последовательном режиме, и в которой, при записи в запоминающие устройства первого типа, дефекты могут возникать в разных местах в запоминающих устройствах, способ включает в себя этапы, на которых:

A) записывают первую секцию входных данных в режиме мультиплексирования, с использованием общих шин, в одной и той же текущей странице запоминающих устройств, начиная с первого столбца запоминающих устройств, столбец за столбцом, и записывают эту первую секцию входных данных также в соответствующую секцию дополнительного запоминающего устройства второго типа, отличного от первого типа;

B) проверяют, возник ли, по меньшей мере, один дефект в, по меньшей мере, одном запоминающем устройстве при записи первой секции входных данных в текущую страницу запоминающих устройств;

C) записывают следующую секцию входных данных в режиме мультиплексирования, с использованием общих шин, в следующей странице запоминающих устройств, начиная с первого столбца запоминающих устройств, столбец за столбцом,

и если на предыдущем этапе дефектов не обнаружено, также записывают эту следующую секцию входных данных в одной и той же секции дополнительного запоминающего устройства,

и если на предыдущем этапе обнаружен дефект, также записывают эту следующую секцию входных данных в следующей соответствующей секции дополнительного запоминающего устройства;

D) проверяют, возник ли, по меньшей мере, один дефект в, по меньшей мере, одном запоминающем устройстве при записи следующей секции входных данных в следующую страницу;

E) переходят к этапам C) и D), пока все секции входных данных не будут записаны в матрицу запоминающих устройств и в дополнительное запоминающее устройство;

F) копируют входные данные, хранящиеся в соответствующих наборах страниц матрицы запоминающих устройств, каковые наборы включают в себя, по меньшей мере, один дефект на набор в, по меньшей мере, одном запоминающем устройстве, в соответствующие наборы страниц в матрице запоминающих устройств, которые еще не заняты входными данными, благодаря чему берут входные данные дефектных единичных страниц не из матрицы запоминающих устройств, но из соответствующих данных единичных страниц, хранящихся в дополнительном запоминающем устройстве.

В принципе, устройство, отвечающее изобретению, пригодно для записи высокоскоростных входных данных в матрицу запоминающих устройств первого типа, причем матрица включает в себя, по меньшей мере, два запоминающих устройства на строку и, по меньшей мере, два запоминающих устройства на столбец, в которой запоминающие устройства строки подключены к общей шине, и каждой строке матрицы назначена отдельная общая шина, и в которой все запоминающие устройства внутренне организованы в виде множественных страниц, в каковые страницы можно записывать входные данные в последовательном режиме, и в которой, при записи в запоминающие устройства первого типа, дефекты могут возникать в разных местах в запоминающих устройствах, причем устройство включает в себя дополнительное запоминающее устройство второго типа, отличного от первого типа, и средство, приспособленное для осуществления следующих функций:

A) запись первой секции входных данных в режиме мультиплексирования, с использованием общих шин, в одной и той же текущей странице запоминающих устройств, начиная с первого столбца запоминающих устройств, столбец за столбцом, и запись этой первой секции входных данных также в соответствующую секцию дополнительного запоминающего устройства;

B) проверка, возник ли, по меньшей мере, один дефект в, по меньшей мере, одном запоминающем устройстве при записи первой секции входных данных в текущую страницу запоминающих устройств;

C) запись следующей секции входных данных в режиме мультиплексирования, с использованием общих шин, в следующей странице запоминающих устройств, начиная с первого столбца запоминающих устройств, столбец за столбцом,

и если в предыдущей функции дефектов не обнаружено, также запись этой следующей секции входных данных в одной и той же секции дополнительного запоминающего устройства, и если в предыдущей функции обнаружен дефект, также запись этой следующей секции входных данных в следующей соответствующей секции дополнительного запоминающего устройства;

D) проверка, возник ли, по меньшей мере, один дефект в, по меньшей мере, одном запоминающем устройстве при записи следующей секции входных данных в следующую страницу;

E) переход к функциям C) и D), пока все секции входных данных не будут записаны в матрицу запоминающих устройств и в дополнительное запоминающее устройство;

F) копирование входных данных, хранящихся в соответствующих наборах страниц матрицы запоминающих устройств, каковые наборы включают в себя, по меньшей мере, один дефект на набор в, по меньшей мере, одном запоминающем устройстве, в соответствующие наборы страниц в матрице запоминающих устройств, которые еще не заняты входными данными, благодаря чему входные данные дефектных единичных страниц берутся не из матрицы запоминающих устройств, но из соответствующих данных единичных страниц, хранящихся в дополнительном запоминающем устройстве.

Дополнительные преимущественные варианты осуществления изобретения раскрыты в соответствующих зависимых пунктах формулы изобретения.

Краткое описание чертежей

Иллюстративные варианты осуществления изобретения описаны со ссылкой на прилагаемые чертежи, в которых:

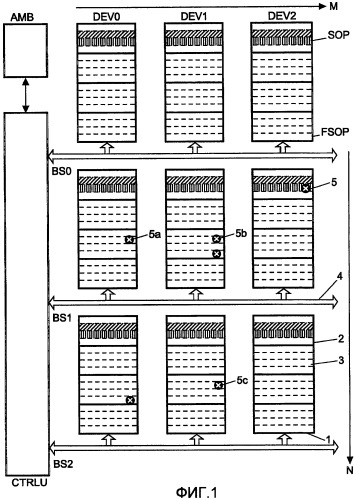

фиг. 1 - матрица флэш-устройств;

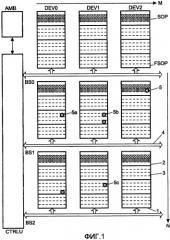

фиг. 2 - дополнительный буфер, содержащий копии неповрежденных данных поврежденных страниц флэш-памяти;

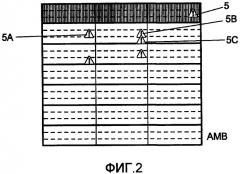

фиг. 3 - элемент списка дефектов;

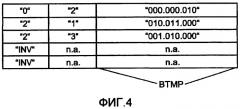

фиг. 4 - пример списка дефектов;

фиг. 5 - массив страничных регистров;

фиг. 6 - регистр битовой карты;

фиг. 7 - последовательность замены страниц.

Осуществление изобретения

Для записи в режиме реального времени предпочтительно, чтобы флэш-устройства были организованы в матрицу, подключенную несколькими шинами BS0, BS1, BS2, ... к блоку управления CTRLU, как показано на фиг. 1. Несколько флэш-устройств совместно используют одну и ту же шину данных, например устройства DEV0-DEV2 совместно используют шину BS0. В целом, количество флэш-устройств, совместно использующих одну и ту же шину данных, равно M. В матрице существует несколько таких строк, состоящих из флэш-устройств и общей шины, количество которых равно N. Матрица включает в себя, по меньшей мере, два запоминающих устройства на строку и, по меньшей мере, два запоминающих устройства на столбец. Блок управления CTRLU может принимать высокоскоростные входные данные, подлежащие хранению или записи. В отношении операции 'стирание' наименьшей адресуемой единицей в устройстве 1 наподобие NAND флэш-памяти является блок флэш-памяти 2 (отмеченный обведением жирной рамкой, т.е. на фигуре устройство 1 имеет четыре блока флэш-памяти).

В отношении операции 'запись' наименьшей адресуемой единицей в NAND флэш-памяти является страница флэш-памяти 3 (на фигуре каждый блок флэш-памяти содержит четыре страницы флэш-памяти).

В одной реализации полное количество блоков флэш-памяти в матрице равно, например, 4096. Каждый блок может содержать 64 страницы.

Входные данные, подлежащие хранению, мультиплексируются и записываются через N параллельных шин в одну и ту же текущую страницу в каждом из флэш-устройств в первом столбце матрицы, т.е. в устройство DEV0 и устройства, размещенные под ним. После заполнения текущей страницы, следующие входные данные записываются в ту же самую текущую страницу во втором столбце матрицы, т.е. в устройство DEV1 и устройства, размещенные под ним. Эта обработка записи продолжается M раз, пока текущая страница всех флэш-устройств матрицы не заполнится входными данными. Это состояние обозначено диагональной штриховкой второй страницы во флэш-устройствах. После этого обработка записи продолжается для следующей (т.е. третьей) страницы во флэш-устройствах, каковая третья страница обозначена на фиг. 1 вертикальной штриховкой. Эти страницы из набора страниц SOP.

Для достижения высокоскоростной записи в режиме реального времени и выявления дефектов содержание данных для текущей страницы флэш-памяти всех флэш-устройств матрицы всякий раз копируется в последовательном режиме в дополнительный буфер памяти AMB (например, SRAM), который может быть подключен к блоку управления CTRLU или к шинам, и эти данные будут оставаться в буфере AMB при возникновении одного или нескольких дефектов в текущей странице в одном или нескольких из флэш-устройств матрицы.

Дополнительный буфер AMB более подробно показан на фиг. 2. Матрица, изображенная на фиг. 1, включает в себя девять флэш-устройств. Первый столбец устройств в матрице связан с первым столбцом в памяти AMB, второй столбец в матрице связан со вторым столбцом в памяти AMB, и т.д. Линия в памяти AMB связана со страницей в строке устройств матрицы.

При записи в третью страницу (обозначенную вертикальной штриховкой) во флэш-устройствах матрицы возникла ошибка или дефект 5. Поэтому исходное содержание входных данных этих страниц сохраняется в соответствующей области (обозначенной вертикальной штриховкой) в памяти AMB, т.е. он сохраняется в AMB без дефекта 5. Поэтому, при записи следующей серии страниц (т.е. четвертой страницы) во флэш-устройства, исходные входные данные записываются в следующую секцию в памяти AMB (т.е. линии 3-6 на фиг. 2). В случае, когда ни в одной из четырех страниц нет дефектов, эта секция (линии 3-6) в памяти AMB перезаписывается следующей серией страниц (т.е. пятой страницей). Поскольку в десятой странице (т.е. в блоке три флэш-устройств) возникло три дефекта 5a, 5b и 5c, исходное содержание входных данных этих страниц сохраняется в соответствующей области (линии 3-6) в памяти AMB без дефектов в соответствующих ячейках 5A, 5B и 5C.

В результате, под управлением блока управления CTRLU, буфер AMB сохраняет копии неповрежденных данных поврежденных страниц флэш-памяти, но его емкость значительно меньше, чем у флэш-матрицы. Например, AMB типа ОЗУ может иметь емкость, позволяющую хранить содержание данных до 15 разных страниц каждого устройства матрицы.

Ошибки страницы (например, 5, 5a, 5b и 5c), возникшие при записи в режиме реального времени, помечены в списке дефектов, причем на фиг. 3 показан элемент списка дефектов. Этот элемент может содержать номер блока BLNO (0 ... B), номер страницы PGNO (0 ... P) и номер столбца устройств DEV0, ..., DEVm во флэш-матрице. Биты BTO, BT1, ..., BTn в номере столбца указывают, в строке под каким номером (=номер шины BS0, BS1, ..., BSn) матрицы возник дефект или возникли множественные дефекты в странице флэш-памяти. Сохранять положение дефекта на странице не требуется.

Иллюстративный список дефектов для девяти флэш-устройств, изображенных на фиг. 1, показан на фиг. 4. Этот список может храниться в блоке управления CTRLU. Этот иллюстративный список дефектов указывает дефектные страницы в матрице, показанной на фиг. 1.

Первый дефект 5 находится в блоке номер BLNO=0 в странице номер PGNO=2, и согласно части битовой карты BTMP в третьем столбце устройств DEV2 относительно второй шины BS1. Второй дефект 5a находится в блоке номер BLNO=2 в странице номер PGNO=1 в первом столбце устройств DEV0 относительно второй шины BS1.

Третий дефект 5b находится в блоке номер BLNO=2 в странице номер PGNO=1 во втором столбце устройств DEV1 относительно второй шины BS1.

Четвертый дефект 5c находится в блоке номер BLNO=2 в странице номер PGNO=1 во втором столбце устройств DEV1 относительно третьей шины BS2.

Другие дефекты находятся в блоке номер BLNO=2 в странице номер PGNO=3 в первом столбце устройств DEV0 относительно третьей шины BS2 и во втором столбце устройств DEV1 относительно второй шины BS1.

После или при записи входных данных во флэш-устройства, флэш-устройства сообщают о любых дефектах через шины BS0-BS2 на блок управления CTRLU.

Копии соответствующих страниц флэш-памяти должны храниться в буфере. При выявлении дефектов предпочтительно анализировать список дефектов в режиме, экономичном в отношении ресурсов и производительности, для поддержки низкого энергопотребления, высокого быстродействия и режима реального времени. Задача состоит в том, чтобы содержание блока флэш-памяти, который содержит одну или несколько поврежденных страниц флэш-памяти, копировался в соответствующие наборы FSOP из трех страниц флэш-памяти в свободный блок флэш-памяти в том же флэш-устройстве. Наконец, поврежденный блок флэш-памяти нужно логически перераспределять новым блоком флэш-памяти, например, в файловой системе.

Таким образом, задача анализа списка дефектов, который содержит информацию о блоке флэш-памяти, странице флэш-памяти, устройстве и шине каждого дефекта подробно описана ниже. В ходе обработки анализа соответствующая дефектная страница флэш-памяти в блоке должна копироваться из буфера в новый блок флэш-памяти. Все остальные страницы флэш-памяти в блоке должны копироваться из поврежденного блока флэш-памяти в новый блок флэш-памяти.

Для определения дефектных страниц флэш-памяти блока флэш-памяти:

a) Инициализируют массив регистров для значений 'страница' неверными значениями (на фиг. 5 показан соответствующий массив страничных регистров, содержащий дефектные страницы для блока флэш-памяти BLNO=2, каковой страничный регистр содержит соответствующие значения номера страницы из столбца PGNO для строк, относящихся к BLNO=2);

b) Задают первое верное значение BLNO «блок» из списка дефектов равным «опорный блок»;

c) Копируют соответствующее значение 'страница' из списка дефектов в надлежащее поле в массиве страничных регистров;

d) Анализируют следующий элемент списка дефектов;

e) Если текущее значение BLNO «блок» равно значению «опорный блок», переходят к этапу c), иначе переходят к этапу d);

f) Повторяют этапы c)-e), пока не будет достигнут конец списка дефектов.

На фиг. 6 показан регистр битовой карты для хранения битовых карт для элементов страницы, обрабатываемых на этапе c). Битовые карты для этих страниц обрабатываются в последовательном порядке обработки PRO (каждые N битов). Регистр битовой карты используется для быстрого вызова бездефектных флэш-устройств, для чего:

g) Инициализируют указатель для битовой карты или для 'счетчика устройств';

h) Инициализируют указатель для массива страничных регистров. Инициализируют регистр битовой карты нулями;

i) Обращаются к единичной ячейке в массиве страничных регистров;

j) Если этот элемент верен, переходят к этапу k), иначе переходят к этапу l);

k) Загружают N битов из соответствующей битовой карты (хранящейся в списке дефектов) и подвергают логической операции ИЛИ с соответствующими значениями регистра битовой карты (N=количество шин);

l) Увеличивают указатель массива страничных регистров и переходят к этапу i), пока не будет достигнут конец массива страничных регистров;

m) Если значение регистра битовой карты равно нулю, то увеличивают указатель битовой карты и 'счетчик устройств' и переходят к этапу h), пока не будет достигнут конец битовой карты. Если значение регистра битовой карты не равно нулю, то начинают следующие этапы n)-u).

На фиг. 7 представлена последовательность замены страниц в соответствии с анализом регистра битовой карты и битовой карты. Для определения шины для дефектного блока в дефектном флэш-устройстве и для копирования соответствующих страниц флэш-памяти:

n) инициализируют 'счетчик шины' и указатель для массива страничных регистров;

o) Считывают массив страничных регистров (фиг. 5) для верного значения;

p) Анализируют бит в регистре битовой карты, на который указывает 'счетчик шины': если этот бит равен нулю, увеличивают 'счетчик шины' и переходят к этапу o), если этот бит равен единице, переходят к этапу q);

q) Для всех значений страницы между нулем и значением, считанным на этапе o) минус один, копируют страницы флэш-памяти из поврежденного блока флэш-памяти в новый блок флэш-памяти. Номер опорного флэш-устройства соответствует значению 'счетчик устройств', номер опорной шины соответствует значению 'счетчик шины';

r) Для значения страницы, считанной на этапе o), копируют данные соответствующей страницы флэш-памяти из дополнительного буфера памяти AMB в новый блок флэш-памяти. Номер опорного флэш-устройства соответствует значению 'счетчик устройств', номер опорной шины соответствует значению 'счетчик шины';

s) Увеличивают указатель для массива страничных регистров и переходят к этапу o), пока не будет достигнут конец массива страничных регистров;

t) Обновляют 'таблицу перераспределения блоков' для соответствующего устройства и помечают соответствующий элемент блока в списке дефектов как неверный;

u) Переходят к этапу a).

Вышеупомянутыми регистрами, указателями, списком и таблицей может управлять блок управления CTRLU.

Изобретение можно использовать в блочно-ориентированном хранилище, которое может быть подвержено дефектам в ходе эксплуатации.

1. Способ записи высокоскоростных входных данных в матрицу запоминающих устройств первого типа, причем матрица включает в себя, по меньшей мере, два запоминающих устройства на строку и, по меньшей мере, два запоминающих устройства на столбец, при этом запоминающие устройства (DEV0, DEV1, DEV2) строки подключены к общей шине (BS0), и каждой строке матрицы назначена отдельная общая шина (BS0, BS1, BS2), и при этом все упомянутые запоминающие устройства внутренне организованы в виде множественных страниц, причем в эти страницы можно последовательно записывать входные данные, и причем при записи в запоминающие устройства первого типа могут возникать дефекты (5, 5а, 5b, 5с) в разных местах в запоминающих устройствах, при этом способ характеризуется этапами, на которых:A) записывают первую секцию входных данных в режиме мультиплексирования, с использованием общих шин, в одной и той же текущей странице запоминающих устройств, начиная с первого столбца (DEVO) запоминающих устройств, столбец за столбцом, и записывают эту первую секцию входных данных также в соответствующую секцию дополнительного запоминающего устройства (АМВ) второго типа, отличного от первого типа,B) проверяют (CTRLU), возник ли, по меньшей мере, один дефект (5, 5а, 5b, 5с) в, по меньшей мере, одном запоминающем устройстве при записи первой секции входных данных в текущую страницу запоминающих устройств,C) записывают следующую секцию входных данных в режиме мультиплексирования, с использованием общих шин, в следующей странице запоминающих устройств, начиная с первого столбца (DEV0) запоминающих устройств, столбец за столбцом, и, если на предыдущем этапе дефектов не обнаружено, также записывают эту следующую секцию входных данных в одной и той же секции упомянутого дополнительного запоминающего устройства, и если на предыдущем этапе обнаружен дефект, также записывают эту следующую секцию входных данных в следующей соответствующей секции дополнительного запоминающего устройства,D) проверяют (CTRLU), возник ли, по меньшей мере, один дефект (5, 5а, 5b, 5с), по меньшей мере, в одном запоминающем устройстве при записи следующей секции входных данных в следующей странице,Е) переходят к этапам С) и D), пока все секции входных данных не будут записаны в матрицу запоминающих устройств и в дополнительное запоминающее устройство (АМВ),F) копируют входные данные, хранящиеся в соответствующих наборах страниц (SOP) матрицы запоминающих устройств, причем эти наборы включают в себя, по меньшей мере, один дефект на набор в, по меньшей мере, одном запоминающем устройстве, в соответствующие наборы страниц (FSOP) в матрице запоминающих устройств, которые еще не заняты входными данными, при этом берут входные данные дефектных единичных страниц не из матрицы запоминающих устройств, а из соответствующих данных единичных страниц, хранящихся в дополнительном запоминающем устройстве (АМВ).

2. Способ по п.1, в котором упомянутые запоминающие устройства первого типа являются устройствами флэш-памяти.

3. Способ по п.1, в котором упомянутые дефекты сохраняют в списке дефектов, который содержит элементы информации о соответствующей странице, соответствующем запоминающем устройстве и соответствующей шине для каждого дефекта.

4. Способ по п.2, в котором упомянутые дефекты сохраняют в списке дефектов, который содержит элементы информации о соответствующем блоке, соответствующей странице, соответствующем запоминающем устройстве и соответствующей шине для каждого дефекта.

5. Способ по п.4, в котором дефектные страницы блока флэш-памяти определяются следующим образом:a) инициализируют массив регистров для значений «страница» неверными значениями;b) задают первое верное значение BLNO «блок» из списка дефектов равным значению «опорный блок»;c) копируют соответствующее значение «страница» из списка дефектов в надлежащее поле в упомянутом массиве страничных регистров;d) анализируют следующий элемент списка дефектов;e) если текущее значение BLNO «блок» равно значению «опорный блок», переходят к этапу с), иначе переходят к этапу d);f) повторяют этапы с)-е), пока не будет достигнут конец списка дефектов.

6. Способ по п.5, в котором генерируют регистр битовой карты для хранения битовых карт для элементов страницы, обрабатываемых на этапе с), и обрабатывают каждые N битов битовых карты для этих страниц в последовательном порядке обработки (PRO), и используют регистр битовой карты для быстрого вызова бездефектных флэш-устройств, при этом регистр битовой карты генерируют следующим образом:g) инициализируют указатель для битовой карты или для «счетчика устройств»;h) инициализируют указатель для упомянутого массива страничных регистров и инициализируют регистр битовой карты нулями;i) обращаются к единичной ячейке в упомянутом массиве страничных регистров;j) если этот элемент верен, переходят к этапу k), иначе переходят к этапу l);k) загружают N битов из соответствующей битовой карты, хранящейся в упомянутом списке дефектов, и подвергают логической операции ИЛИ с соответствующими значениями регистра битовой карты;l) увеличивают указатель массива страничных регистров и переходят к этапу i), пока не будет достигнут конец массива страничных регистров;m) если значение регистра битовой карты равно нулю, увеличивают указатель битовой карты и упомянутый «счетчик устройств» и переходят к этапу h), пока не будет достигнут конец битовой карты.

7. Способ по п.6, в котором, если на этапе m) значение регистра битовой карты не равно нулю, для определения шины для дефектного блока в дефектном флэш-устройстве и для копирования соответствующих страниц флэш-памяти выполняют этапы, на которых:n) инициализируют «счетчик шины» и указатель для массива страничных регистров;о) считывают массив страничных регистров для верного значения;р) анализируют бит в регистре битовой карты, на который указывает «счетчик шины»: если этот бит равен нулю, увеличивают «счетчик шины» и переходят к этапу о), если этот бит равен единице, переходят к этапу q), q) для всех значений страницы между нулем и значением, считанным на этапе о) минус один, копируют страницы флэш-памяти из поврежденного блока флэш-памяти в новый блок флэш-памяти, при этом номер опорного флэш-устройства соответствует значению «счетчик устройств», и номер опорной шины соответствует значению «счетчик шины»;r) для значения страницы, считанной на этапе о), копируют данные соответствующей страницы флэш-памяти из дополнительного буфера памяти (АМВ) в новый блок флэш-памяти, при этом номер опорного флэш-устройства соответствует значению «счетчик устройств», и номер опорной шины соответствует значению «счетчик шины»;s) увеличивают указатель для массива страничных регистров и переходят к этапу о), пока не будет достигнут конец массива страничных регистров;t) обновляют «таблицу перераспределения блоков» для соответствующего устройства и помечают соответствующий элемент блока в списке дефектов как неверный;u) переходят к этапу а) по п.5.

8. Устройство для записи высокоскоростных входных данных в матрицу запоминающих устройств первого типа, причем матрица включает в себя, по меньшей мере, два запоминающих устройства на строку и, по меньшей мере, два запоминающих устройства на столбец, в которой запоминающие устройства (DEV0, DEV1, DEV2) строки подключены к общей шине (BS0) и каждой строке матрицы назначена отдельная общая шина (BS0, BS1, BS2), и при этом все запоминающие устройства внутренне организованы в виде множественных страниц, в каковые страницы можно записывать входные данные в последовательном режиме, и причем, при записи в запоминающие устройства первого типа, дефекты (5, 5а, 5b, 5с) могут возникать в разных местах в запоминающих устройствах, причем упомянутое устройство включает в себя дополнительное запоминающее устройство (АМВ) второго типа, отличного от первого типа, и средство (CTRLU, BS0, BS1, BS2), выполненное с обеспечением возможности осуществления следующих функций:A) записи первой секции входных данных в режиме мультиплексирования, с использованием общих шин, в одной и той же текущей странице запоминающих устройств, начиная с первого столбца запоминающих устройств (DEV0), столбец за столбцом, и записи этой первой секции входных данных также в соответствующую секцию дополнительного запоминающего устройства (АМВ);B) проверки, возник ли, по меньшей мере, один дефект (5, 5а, 5b, 5с) в, по меньшей мере, одном запоминающем устройстве при записи первой секции входных данных в текущую страницу запоминающих устройств;C) записи следующей секции входных данных в режиме мультиплексирования, с использованием общих шин, в следующей странице запоминающих устройств, начиная с первого столбца запоминающих устройств (DEV0), столбец за столбцом, и если в предыдущей функции дефектов не обнаружено, также запись этой следующей секции входных данных в одной и той же секции дополнительного запоминающего устройства, и если в предыдущей функции обнаружен дефект, также записи этой следующей секции входных данных в следующей соответствующей секции дополнительного запоминающего устройства;D) проверки, возник ли, по меньшей мере, один дефект (5, 5а, 5b, 5с) в, по меньшей мере, одном запоминающем устройстве при записи следующей секции входных данных в следующую страницу;Е) перехода к функциям С) и D), пока все секции входных данных не будут записаны в матрицу запоминающих устройств и в упомянутое дополнительное запоминающее устройство (АМВ);F) копирования входных данных, хранящихся в соответствующих наборах страниц (SOP) матрицы запоминающих устройств, причем эти наборы включают в себя, по меньшей мере, один дефект на набор в, по меньшей мере, одном запоминающем устройстве, в соответствующие наборы страниц (FSOP) в матрице запоминающих устройств, которые еще не заняты упомянутыми входными данными, при этом входные данные дефектных единичных страниц берутся не из матрицы запоминающих устройств, а из соответствующих данных единичных страниц, хранящихся в дополнительном запоминающем устройстве (АМВ).

9. Устройство по п.8, в котором упомянутые запоминающие устройства первого типа являются устройствами флэш-памяти.

10. Устройство по п.8, в котором упомянутые дефекты хранятся в списке дефектов, который содержит элементы информации о соответствующей странице, соответствующем запоминающем устройстве и соответствующей шине для каждого дефекта.

11. Устройство по п.9, в котором упомянутые дефекты хранятся в списке дефектов, который содержит элементы информации о соответствующем блоке, соответствующей странице, соответствующем запоминающем устройстве и соответствующей шине для каждого дефекта.

12. Устройство по п.11, в котором дефектные страницы блока флэш-памяти определяются следующим образом:a) инициализируют массив регистров для значений «страница» неверными значениями;b) задают первое верное значение BLNO «блок» из списка дефектов равным «опорный блок»;c) копируют соответствующее значение «страница» из списка дефектов в надлежащее поле в массиве страничных регистров;d) анализируют следующий элемент списка дефектов;e) если текущее значение BLNO «блок» равно значению «опорный блок», переходят к этапу с), иначе переходят к этапу d);f) повторяют этапы с)-е), пока не будет достигнут конец списка дефектов.

13. Устройство по п.12, в котором генерируют регистр битовой карты для хранения битовых карт для элементов страницы, обрабатываемых на этапе с), и обрабатывают каждые N битов битовых карты для этих страниц в последовательном порядке обработки (PRO), и используют регистр битовой карты для быстрого вызова бездефектных флэш-устройств, при этом регистр битовой карты генерируют следующим образом:g) инициализируют указатель для битовой карты и для «счетчика устройств»;h) инициализируют указатель для упомянутого массива страничных регистров и инициализируют регистр битовой карты нулями;i) обращаются к единичной ячейке в упомянутом массиве страничных регистров;j) если этот элемент верен, переходят к этапу k), иначе переходят к этапу l);k) загружают N битов из соответствующей битовой карты, хранящейся в списке дефектов и подвергают логической операции ИЛИ с соответствующими значениями регистра битовой карты;l) увеличивают указатель массива страничных регистров и переходят к этапу i), пока не будет достигнут конец массива страничных регистров;m) если значение регистра битовой карты равно нулю, увеличивают указатель битовой карты и «счетчик устройств» и переходят к этапу h), пока не будет достигнут конец битовой карты.

14. Устройство по п.13, в котором, если на этапе m) значение регистра битовой карты не равно нулю, для определения шины для дефектного блока в дефектном флэш-устройстве и для копирования соответствующих страниц флэш-памяти выполняют этапы, на которых:n) инициализируют «счетчик шины» и указатель для массива страничных регистров;о) считывают массив страничных регистров для верного значения;р) анализируют бит в регистре битовой карты, на который указывает «счетчик шины»: если этот бит равен нулю, увеличивают «счетчик шины» и переходят к этапу о), если этот бит равен единице, переходят к этапу q), q) для всех значений страницы между нулем и значением, считанным на этапе о) минус один, копируют страницы флэш-памяти из поврежденного блока флэш-памяти в новый блок флэш-памяти, при этом номер опорного флэш-устройства соответствует значению «счетчик устройств», и номер опорной шины соответствует значению «счетчик шины»;r) для значения страницы, считанной на этапе о), копируют данные соответствующей страницы флэш-памяти из дополнительного буфера памяти (АМВ) в новый блок флэш-памяти, благодаря чему номер опорного флэш-устройства соответствует значению «счетчик устройств», и номер опорной шины соответствует значению «счетчик шины»;s) увеличивают указатель для массива страничных регистров и переходят к этапу о), пока не будет достигнут конец массива страничных регистров;t) обновляют «таблицу перераспределения блоков» для соответствующего устройства и помечают соответствующий элемент блока в списке дефектов как неверный;u) переходят к этапу а) по п.12.