Устройство поиска информации

Иллюстрации

Показать всеИзобретение относится к устройству для поиска информации и оперативной идентификации в цифровых системах связи, в частности в сети передачи данных типа "Internet" стека коммуникационных протоколов TCP/IP. Техническим результатом является повышение устойчивости функционирования автоматизированных систем в условиях несанкционированного информационного воздействия в сетях передачи данных типа "Internet". Устройство содержит первый блок памяти, первый счетчик, первый и второй блок дешифрации, второй счетчик, второй блок памяти, третий счетчик, третий блок памяти, четвертый счетчик, четвертый блок памяти, пятый счетчик, третий блок дешифрации, седьмой счетчик, пятый блок памяти, восьмой счетчик, шестой блок памяти, шестой счетчик, седьмой блок памяти, девятый счетчик, восьмой блок памяти, десятый счетчик, четвертый, пятый и шестой блоки дешифрации, блок «запросов», блок «нагрузки», блок «сканирования SYN», блок «сканирования FIN», блок «достоверности», первый и второй блоки сравнения, элемент 2И, блок управления, блок индикации. Поставленная цель достигается за счет введения дополнительно десятого счетчика, третьего, четвертого, пятого, шестого, седьмого, восьмого блоков памяти, второго блока сравнения, элемента 2И, блока «запросов», блока «нагрузки», блока «сканирования SYN», блок «сканирования FIN», блока «достоверности» и введения новых связей между блоками. 7 ил.

Реферат

Изобретение относится к области электросвязи и может быть использовано для поиска информации и оперативной идентификации стека коммуникационных протоколов TCP/IP, применяемого в цифровых системах связи, в частности в сети передачи данных типа "Internet".

Известно устройство поиска информации по патенту РФ №2219577, G06F 17/40, заявленном 24.04.2002, содержащее делитель частоты, два блока памяти, вычитающий счетчик, четыре блока дешифрации, четыре счетчика, четыре блока приема адреса, два блока сравнения, два дешифратора и блок индикации.

Данное устройство имеет недостаток - узкую область применения, поэтому предназначено только для анализа сравнительно небольшого количества параметров проходящих через него потоков, что приводит к неустойчивому функционированию автоматизированных систем в условиях несанкционированного информационного воздействия и ограничивает область его применения в сетях передачи данных типа "Internet" в условиях несанкционированного воздействия (информационных атак).

Наиболее близким по технической сущности (прототипом) является устройство поиска информации, содержащее два блока памяти, девять счетчиков, одиннадцать блоков дешифрации, блок сравнения, блок управления и блок индикации, патент 2301443, опубликованный 20.06.2007. Вход первого блока памяти является входом устройства поиска информации, а его выход подключен к информационному входу первого блока дешифрации, второй вход которого подключен к первому счетчику, а выход дешифратора - к входу второго счетчика, первый выход которого соединен с вторым входом второго блока дешифрации, первый вход которого подключен к выходу первого блока памяти. Выход второго блока дешифрации соединен с входом второго блока памяти, а выход второго счетчика соединен с входом третьего счетчика, выход которого соединен с первым входом третьего блока дешифрации, второй вход которого подключен к выходу первого блока памяти. Первый и второй выходы третьего блока дешифрации подключены к входам четвертого и пятого счетчиков. Выход счетчика подключен к первому входу пятого блока дешифрации, второй вход которого соединен с выходом первого блока памяти, выход пятого блока дешифрации соединен с вторым входом блока сравнения, первый вход которого подключен через четвертый блок дешифрации к выходу четвертого счетчика, причем второй вход четвертого блока дешифрации соединен с выходом первого блока памяти. Входы блока управления подключены к второму выходу первого блока дешифрации, к третьему выходу третьего блока дешифрации, к второму выходу блока сравнения, к второму выходу шестого блока дешифрации, к первому выходу седьмого блока дешифрации, к выходу восьмого блока дешифрации, к выходу девятого блока дешифрации, к первому выходу десятого блока дешифрации, к двум выходам одиннадцатого блока дешифрации. Одиннадцатый выход блока управления подключен к входу первого счетчика и к первому блоку памяти, двенадцатый выход блока управления - к первому блоку памяти, тринадцатый выход - к входу блока индикации. Выход второго блока памяти соединен с первым входом шестого счетчика, второй вход которого подключен к выходу первого блока сравнения, а выход шестого счетчика соединен с входом шестого блока дешифрации, первый выход которого соединен с входом седьмого счетчика, выход которого подключен к входу седьмого блока дешифрации, второй выход которого соединен с входом восьмого счетчика, выход которого подключен к первым входам десятого, восьмого и девятого блоков дешифрации, вторые входы каждого из которых соединены с выходом первого блока памяти. Вторые входы шестого, седьмого и одиннадцатого блоков дешифрации соединены с выходом первого блока памяти, а второй выход десятого блока дешифрации соединен с входом девятого счетчика, выход которого подключен к первому входу одиннадцатого блока дешифрации. Блок индикации является выходом устройства.

К недостаткам устройства - прототипа относится анализ сравнительно небольшого количества параметров проходящих через него потоков, основанный на сигнатурном методе, что приводит к неустойчивому функционированию автоматизированных систем в условиях несанкционированного информационного воздействия.

Задачей изобретения является разработка устройства поиска информации, обеспечивающего расширенную область применения за счет анализа протоколов, учета правил установления и ведения сеанса связи, а именно за счет выявления случаев аномального возрастания количества запросов на установление соединения, выявления случаев аномального увеличения входящего графика, выявления сканирования, проводимого в сети, определения достоверности используемого источником IP адреса и выявления случаев установки запрещенных комбинаций флагов.

Эта задача достигается тем, что в известное устройство поиска информации, содержащее счетчики, дешифраторы, блоки памяти, первый блок сравнения, блок управления и блок индикации, который подключен к первому выходу блока управления, второй выход которого соединен с управляющим входом первого блока памяти, адресный вход которого является входом устройства, выход данных первого блока памяти подключен к адресным входам всех дешифраторов, причем выход первого счетчика соединен с входом данных первого дешифратора, первый выход которого подключен к входу разрешения счета второго счетчика, а второй выход первого дешифратора соединен с первым входом блока управления, первый выход второго счетчика через второй дешифратор подключен к входу разрешения записи второго блока памяти, выход которого соединен с первым входом шестого счетчика, второй выход второго счетчика подключен к входу разрешения счета третьего счетчика, дополнительно введены десятый счетчик, третий, четвертый, пятый, шестой, седьмой, восьмой блоки памяти, второй блок сравнения, элемент 2И, блок "запросов", вырабатывающий сигнал об обнаружении аномального количества повторяющихся импульсов на установление соединения по протоколу TCP, блок "нагрузки", вырабатывающий сигнал об обнаружении аномальной нагрузки в последовательности пакетов IСМР, блок "сканирования SYN", вырабатывающий сигнал об обнаружении сканирования флагом SYN протокола TCP, блок "сканирования FIN", вырабатывающий сигнал об обнаружении сканирования флагом FIN протокола TCP, блок "достоверности", вырабатывающий сигнал об обнаружении не достоверного IP адреса полученного пакета, причем выход третьего счетчика соединен с входом разрешения записи третьего блока памяти, первый выход которого подключен к входу разрешения счета четвертого счетчика, выход которого соединен с входом разрешения записи четвертого блока памяти, выход которого подключен к входу разрешения счета пятого счетчика, выход которого через третий дешифратор соединен с входом разрешения счета седьмого счетчика, выход которого подключен к входу записи пятого блока памяти, первый выход которого соединен с входом разрешения счета восьмого счетчика, выход которого подключен к входу записи шестого блока памяти, первый выход которого соединен с входом предустановки шестого счетчика, выход которого подключен к входу разрешения записи седьмого блока памяти, первый выход которого соединен с входом разрешения счета девятого счетчика, выход которого подключен к входу разрешения записи восьмого блока памяти, первый выход которого подключен к входу разрешения счета десятого счетчика, выход которого соединен с входами данных четвертого, пятого и шестого дешифраторов и подключен к третьему входу блока управления, четвертый вход которого соединен с адресным входом первого блока памяти, второй выход которого подключен к входу разрешения первого счетчика, а выход данных первого блока памяти подключен к входам данных всех других блоков памяти. Выход четвертого дешифратора соединен с входом блока "запросов" и первым входом блока "сканирования SYN", выход которого подключен к пятому входу блока управления, а второй вход блока "сканирования SYN" соединен с вторым входом блока "сканирования FIN", первым входом блока "достоверности", первым входом первого блока сравнения и подключен ко второму выходу пятого блока памяти, выход пятого дешифратора соединен с первым входом блока "сканирования FIN", выход которого соединен с шестым входом блока управления, к седьмому входу которого подключен выход блока "запросов", а восьмой вход блока управления подключен к выходу блока нагрузки, первый вход которого соединен с вторым выходом третьего блока памяти, а второй вход блока нагрузки соединен с вторым выходом третьего дешифратора и подключен к второму входу блока управления, третий выход которого соединен с тактовыми входами всех счетчиков импульсов, входы сброса которых объединены и подключены к четвертому выходу блока управления, девятый вход которого соединен с выходом блока "достоверности", второй вход которого соединен с первым выходом первого дешифратора, а третий вход блока "достоверности" подключен к второму выходу четвертого блока памяти, при этом второй выход шестого блока памяти соединен со вторым входом первого блока сравнения, выход которого подключен в первому входу элемента 2И, второй вход которого соединен с выходом второго блока сравнения, первый и второй входы которого подключены соответственно к вторым выходам седьмого и восьмого блоков памяти, а выход элемента 2И соединен с десятым входом блока управления, одиннадцатый вход которого подключен к выходу шестого дешифратора.

Проведенный анализ уровня техники позволил установить, что аналоги, характеризующиеся совокупностью признаков, тождественных всем признакам заявленного технического решения, отсутствуют, что указывает на соответствие заявленного устройства условию патентоспособности «Новизна». Результаты поиска известных решений в данной и смежных областях техники с целью выявления признаков, совпадающих с отличительными от прототипа признаками заявленного объекта, показали, что они не следуют явным образом из уровня техники. Из современного уровня техники также не выявлена известность влияния предусматриваемых существенными признаками заявленного изобретения преобразований на достижение указанного технического результата. Следовательно, заявленное изобретение соответствует условию патентоспособности «Изобретательский уровень».

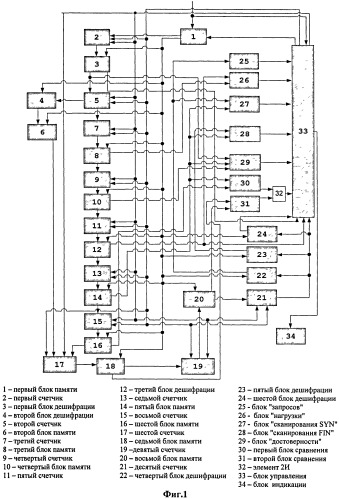

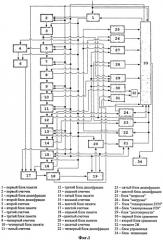

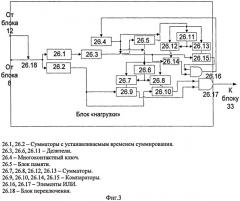

Заявленное устройство поясняется следующими чертежами:

фиг.1 - структурная схема устройства;

фиг.2 - структурная схема блока «запросов»;

фиг.3 - структурная схема блока «нагрузки»;

фиг.4 - структурная схема блока «сканирования SYN»;

фиг.5 - структурная схема блока «сканирования FIN»;

фиг.6 - структурная схема блока «достоверности»;

фиг.7 - структурная схема блока управления и индикации.

Устройство поиска информации, показанное на фиг.1, содержит первый блок памяти 1, первый счетчик 2, первый 3 и второй 4 блок дешифрации, второй счетчик 5, второй блок памяти 6, третий счетчик 7, третий блок памяти 8, четвертый счетчик 9, четвертый блок памяти 10, пятый счетчик 11, третий блок дешифрации 12, седьмой счетчик 13, пятый блок памяти 14, восьмой счетчик 15, шестой блок памяти 16, шестой счетчик 17, седьмой блок памяти 18, девятый счетчик 19, восьмой блок памяти 20, десятый счетчик 21, четвертый 22, пятый 23 и шестой 24 блоки дешифрации, блок «запросов» 25, блок «нагрузки» 26, блок «сканирования SYN» 27, блок «сканирования FIN» 28, блок «достоверности» 29, первый 30 и второй 31 блоки сравнения, элемент 2И 32, блок управления 33, блок индикации 34.

Адресный вход первого блока памяти 1 является входом устройства, а его управляющий вход соединен с вторым выходом блока управления 33, первый выход которого подключен к входу блока индикации 34. Выход данных первого блока памяти 1 подключен к адресным входам первого 3, второго 4, третьего 12, четвертого 22, пятого 23, шестого 24 дешифраторов. Выход первого счетчика 2 соединен с входом данных первого дешифратора 3, первый выход которого подключен к входу разрешения счета второго счетчика 5, а второй выход первого дешифратора 3 соединен с первым входом блока управления 33, первый выход второго счетчика 5 через второй дешифратор 4 подключен к входу разрешения записи второго блока памяти 6, выход которого соединен с первым входом шестого счетчика 17. Второй выход второго счетчика 5 подключен к входу разрешения счета третьего счетчика 7, выход которого соединен с входом разрешения записи третьего блока памяти 8, первый выход которого подключен к входу разрешения счета четвертого счетчика 9, выход которого соединен с входом разрешения записи четвертого блока памяти 10, первый выход которого подключен к входу разрешения счета пятого счетчика 11, выход которого через третий дешифратор 12 соединен с входом разрешения счета седьмого счетчика 13, выход которого подключен к входу разрешения записи пятого блока памяти 14, первый выход которого соединен с входом разрешения счета восьмого счетчика 15, выход которого подключен к входу разрешения записи шестого блока памяти 16, первый выход которого соединен с входом предустановки шестого счетчика 17, выход которого подключен к входу разрешения записи седьмого блока памяти 18, первый выход которого соединен с входом разрешения счета девятого счетчика 19, выход которого подключен к входу разрешения записи восьмого блока памяти 20, первый выход которого подключен к входу разрешения счета десятого счетчика 21, выход которого соединен с входами данных четвертого 22, пятого 23 и шестого 24 дешифраторов и подключен к третьему входу блока управления 33, четвертый вход которого соединен с адресным входом первого блока памяти 1, второй выход которого подключен к входу разрешения первого счетчика 2. Выход данных первого блока памяти 1 подключен к входам данных второго 6, третьего 8, четвертого 10, пятого 14, шестого 16, седьмого 18, восьмого 20 блоков памяти. Выход четвертого дешифратора 22 соединен с входом блока "запросов" 25 и первым входом блока "сканирования SYN" 27, выход которого подключен к пятому входу блока управления 33. Второй вход блока "сканирования SYN" 27 соединен с вторым входом блока "сканирования FIN" 28, первым входом блока "достоверности" 29, первым входом первого блока сравнения 30 и подключен ко второму выходу пятого блока памяти 14. Выход пятого дешифратора 23 соединен с первым входом блока "сканирования FIN" 28, выход которого соединен с шестым входом блока управления 33, к седьмому входу которого подключен выход блока "запросов" 25. Восьмой вход блока управления 33 подключен к выходу блока нагрузки 26, первый вход которого соединен с вторым выходом третьего блока памяти 8, а второй вход блока нагрузки 26 соединен с вторым выходом третьего дешифратора 12 и подключен к второму входу блока управления 33, третий выход которого соединен с тактовыми входами первого 2, второго 5, третьего 7, четвертого 9, пятого 11, шестого 17, седьмого 13, восьмого 15, девятого 19 и десятого 21 счетчиков импульсов, входы сброса которых объединены и подключены к четвертому выходу блока управления 33, девятый вход которого соединен с выходом блока "достоверности" 29, второй вход которого соединен с первым выходом первого дешифратора 3, а третий вход блока "достоверности" 29 подключен к второму выходу четвертого блока памяти 10. Второй выход шестого блока памяти 16 соединен со вторым входом первого блока сравнения 30, выход которого подключен к первому входу элемента 2И 32, второй вход которого соединен с выходом второго блока сравнения 31, первый и второй входы которого подключены соответственно к вторым выходам седьмого 18 и восьмого 20 блоков памяти, а выход элемента 2И 32 соединен с десятым входом блока управления, одиннадцатый вход которого подключен к выходу шестого дешифратора 24. Блок индикации 34 является выходом устройства.

Разрядность шины «Байты данных пакета» определяется разрядностью анализируемых данных, и так как устройство обрабатывает байты, она является восьмиразрядной. Информационные связи между выходом первого блока памяти 1 и адресными входами первого 3, второго 4, третьего 12, четвертого 22, пятого 23, шестого 24 блоков дешифрации, а также адресными входами третьего 8, четвертого 10, пятого 14, шестого 16, седьмого 18, восьмого 20 блоков памяти являются восьмиразрядными, так как служат для передачи байтов и физически представляют из себя шину из восьми параллельных проводников. Управляющие связи между первым счетчиком 2 и первым блоком дешифрации 3, первым блоком дешифрации 3 и вторым счетчиком 5, вторым счетчиком 5 и вторым блоком дешифрации 4, вторым блоком дешифрации 4 и вторым блоком памяти 6, вторым счетчиком 5 и третьим счетчиком 7, третьим счетчиком 7 и третьим блоком памяти 8, третьим блоком памяти 8 и четвертым счетчиком 9, четвертым счетчиком 9 и четвертым блоком памяти 10, четвертым блоком памяти 10 и пятым счетчиком 11, пятым счетчиком 11 и третьим блоком дешифрации 12, третьим блоком дешифрации 12 и седьмым счетчиком 13, седьмым счетчиком 13 и пятым блоком памяти 14, пятым блоком памяти 14 и восьмым счетчиком 15, восьмым счетчиком 15 и шестым блоком памяти 16, шестым блоком памяти 16 и шестым счетчиком 17, шестым счетчиком 17 и седьмым блоком памяти 18, седьмым блоком памяти 18 и девятым счетчиком 19, девятым счетчиком 19 и восьмым блоком памяти 20, восьмым блоком памяти 20 и десятым счетчиком 21, десятым счетчиком 21 и четвертым 22, пятым 23, шестым 24 блоками дешифрации являются одноразрядными, так как служат для передачи логических сигналов «0» или «1» и физически представляют собой один проводник. Информационная связь между вторым блоком памяти 6 и шестым счетчиком 17 является восьмиразрядной, так как служит для передачи байтов и физически представляет из себя шину из восьми параллельных проводников. Информационные связи между первым блоком дешифрации 3 и блоком «достоверности» 29, третьим блоком дешифрации 12 и блоком «нагрузки» 26, четвертым блоком дешифрации 22 и блоком «запросов» 25, четвертым блоком дешифрации 22 и блоком «сканирования SYN» 27, пятым блоком дешифрации 23 и блоком «сканирования FIN» 28, шестым блоком дешифрации 24 и блоком управления 33 являются одноразрядными, так как служат для передачи логических сигналов «0» или «1» и физически представляют собой один проводник. Информационные связи между третьим блоком памяти 8 и блоком «нагрузки» 26 являются шестнадцатиразрядными, так как служат для передачи двухбайтовых слов и физически представляют из себя шину из шестнадцати параллельных проводников. Информационные связи между четвертым блоком памяти 10 и блоком «достоверности» 29 являются восьмиразрядными, так как служат для передачи байтов и физически представляют из себя шину из восьми параллельных проводников. Информационные связи между пятым блоком памяти 14 и блоком «сканирования SYN» 27, пятым блоком памяти 14 и блоком «сканирования FIN» 28, пятым блоком памяти 14 и блоком «достоверности» 29, пятым блоком памяти 14 и первым блоком сравнения 30, шестым блоком памяти 16 и первым блоком сравнения 30, седьмым блоком памяти 18 и вторым блоком сравнения 31, восьмым блоком памяти 20 и вторым блоком сравнения 31, являются шестнадцатиразрядными, так как служат для передачи двухбайтовых слов и физически представляют из себя шину из шестнадцати параллельных проводников. Информационные связи между блоком «запросов» 25 и блоком управления 33, блоком «нагрузки» 26 и блоком управления 33, блоком «сканирования SYN» 27 и блоком управления 33, блоком «сканирования FIN» 28 и блоком управления 33, блоком «достоверности» 29 и блоком управления 33, первым блоком сравнения 30 и элементом 2И 32, вторым блоком сравнения 31 и элементом 2И 32, элементом 2И 32 и блоком управления 33, десятым счетчиком 21 и блоком управления 33, третьим блоком дешифрации 12 и блоком управления 33, первым блоком дешифрации 3 и блоком управления 33, блоком управления 33 и блоком памяти 1, блоком памяти 1 и первым счетчиком 2, канальным контроллером и блоком управления 33, блоком управления 33 и блоком индикации 34 являются одноразрядными, так как служат для передачи логических сигналов «0» или «1» и физически представляют собой один проводник.

Информационные связи между блоком управления 33 и всеми счетчиками являются одноразрядными, так как служат для передачи тактовых импульсов и импульсов сброса и физически представляют каждая из себя один проводник.

Первый блок памяти 1 предназначен для хранения и последующего считывания с них байтов данных пакетов, поступающих с демодулирующего устройства (канального контроллера) и подачи команды об окончании записи пришедших данных пакета на первый счетчик 2.

Первый счетчик 2 отсчитывает 14 байт в цифровой последовательности для определения пакета IP.

Первый блок дешифрации 3 предназначен для определения в последовательности поступающих данных протокола IP и подачи управляющего сигнала на блок «достоверности» 29.

Второй счетчик 5 предназначен для отсчета 4 бит для обнаружения поля длины заголовка пакета.

Второй блок дешифрации 4 служит для определения значения длины заголовка.

Третий счетчик 7 предназначен для отсчета 12 бит для нахождения общего размера IP пакета и подачи управляющего сигнала разрешения записи этого значения в третий блок памяти 8.

Второй блок памяти 6 предназначен для записи в него и хранения длины заголовка IP пакета.

Третий блок памяти 8 предназначен для записи в него и хранения общего размера пакета IP.

Четвертый счетчик 9 предназначен для отсчета 6 байт для нахождения значения поля TTL пакета и подачи управляющего сигнала о разрешении его записи в четвертый блок памяти 10.

Четвертый блок памяти 10 предназначен для записи в него и хранения значения поля TTL пакета IP.

Пятый счетчик 11 предназначен для отсчета 1 байта для нахождения значения поля, обозначающего протокол вышестоящего уровня, пакета и подаче управляющего сигнала о разрешении его записи в третий блок дешифрации 12.

Третий блок дешифрации 12 служит для определения числового значения «шесть» в десятичном виде, т.с. определения протокола TCP или значения «один» в десятичном виде, т.е. определения протокола IСМР и подачи управляющего сигнала «1» на седьмой счетчик 13 или на блок «нагрузки» 26.

Седьмой счетчик 13 предназначен для отсчета 5 байт для нахождения двух последних байт адреса отправителя IP пакета и подачи управляющего сигнала разрешения записи этого значения в пятый блок памяти 14.

Пятый блок памяти 14 предназначен для записи в него и хранения значения двух последних байт адреса отправителя пакета IP.

Восьмой счетчик 15 предназначен для отсчета 4 байт для нахождения двух последних байт адреса получателя IP пакета и подачи управляющего сигнала разрешения записи этого значения в шестой блок памяти 16.

Шестой блок памяти 16 предназначен для записи в него и хранения значения двух последних байт адреса получателя пакета IP.

На первый вход шестого счетчика 17 поступает информация о длине заголовка, и он отыскивает поле, содержащее номер порта источника в заголовке TCP и подает управляющий сигнал разрешения записи этого значения в седьмой блок памяти 18.

Седьмой блок памяти 18 предназначен для записи в него и хранения значения номера порта источника заголовка TCP.

Девятый счетчик 19 предназначен для нахождения значения номера порта приемника заголовка TCP и подачи управляющего сигнала разрешения записи этого значения в восьмой блок памяти 20.

Восьмой блок памяти 20 предназначен для записи в него и хранения значения номера порта приемника заголовка TCP.

Десятый счетчик 21 предназначен для нахождения байта флагов заголовка TCP и подачи управляющего сигнала разрешения записи этого байта в четвертый 22, пятый 23, шестой 24 блоки дешифрации.

Четвертый блок дешифрации 22 предназначен для определения случая установки флага SYN в заголовке TCP и подачи управляющего сигнала на блоки «запросов» 25 и «сканирования SYN» 27.

Пятый блок дешифрации 23 предназначен для определения случая установки флага FIN в заголовке TCP и подачи управляющего сигнала на блок «сканирования FIN» 28.

Шестой блок дешифрации 24 предназначен для определения случая совместной установки флага SYN и FIN в заголовке TCP и подачи управляющего сигнала на блок управления 33.

Блок «запросов» 25 предназначен для выработки сигнала об обнаружении аномального количества повторяющихся запросов на установление соединения по протоколу TCP и подачи его на блок управления 33. Вариант схемы блока «запросов» 25 представлен на фиг.2.

Блок «нагрузки» 26 предназначен для выработки сигнала об обнаружении аномальной нагрузки в последовательности пакетов IСМР и подачи его на блок управления 33. Вариант схемы блока «нагрузки» 26 представлен на фиг.3.

Блок «сканирования SYN» 27 предназначен для выработки сигнала об обнаружении сканирования флагом SYN, протокола TCP и подачи его на блок управления 33. Вариант схемы блока «сканирования SYN» 27 представлен на фиг.4.

Блок «сканирования FIN» 28 предназначен для выработки сигнала об обнаружении сканирования флагом FIN, протокола TCP и подачи его на блок управления 33. Вариант схемы блока «сканирования FIN» 28 представлен на фиг.5.

Блок «достоверности» 29 предназначен для выработки сигнала об обнаружении недостоверного IP адреса полученного пакета и подачи его на блок управления 33. Вариант схемы блока «достоверности» 29 представлен на фиг.6.

Первый блок сравнения 30 предназначен для обнаружения совпадения двух последних байт адреса отправителя и адреса получателя IP пакета и подачи сигнала на элемент 2И 32.

Второй блок сравнения 31 предназначен для обнаружения совпадения номера порта источника и приемника заголовка TCP и подачи сигнала на элемент 2И 32.

Элемент 2И 32 указывает о срабатывании обоих блоков сравнения и подает сигнал об этом на блок управления 33.

Блок управления 33 предназначен для формирования тактовых импульсов и импульсов сброса на все счетчики и подачи управляющего сигнала на первый блок памяти 1 для разрешения считывания следующего пакета информации. Вариант схемы блока управления 33 представлен на фиг.7.

Блок индикации 34 предназначен для визуального отображения принятого решения об аномальности проходящего графика.

Входящие в общую структуру устройства поиска информации элементы являются типовыми и могут быть технически реализованы в настоящее время при использовании имеющейся элементной базы.

Схемы первого 1, второго 6, третьего 8, четвертого 10, пятого 14, шестого 16, седьмого 18, восьмого 20 блоков памяти известны и приведены, например, в книге: Шило В.Л. "Популярные цифровые микросхемы". - М.: Радио и связь, 1987 г. и могут быть реализованы на микросхемах К555 РЕ24 или К1533 ИР22. Один разряд блока памяти используется в качестве второго выхода для формирования управляющих сигналов, а остальные разряды используются для записи и хранения информации и являются первым выходом блока памяти.

Схемы первого 30 и второго 31 блоков сравнения для сравнения двух N - разрядных слов известны и приведены, например, в книге: Шило В.Л. "Популярные цифровые микросхемы". - М.: Радио и связь, 1987 г. и могут быть реализованы на микросхемах К561 СП1.

Схемы первого 3, второго 4, третьего 12, четвертого 22, пятого 23, шестого 24, блоков дешифрации известны и приведены, например, в изобретении №2219577, МПК G06F 17/40 и могут быть реализованы на микросхеме К555 ИД10. Типовая схема блока дешифрации, преобразующего двоично-десятичный код в десятичный имеет десять выходов от 0 до 9, в этом случае выход «1» является первым выходом блока дешифрации, а выход «6» является вторым выходом блока дешифрации.

Блок «запросов» 25 содержит два счетчика 25.1 и 25.2 с разным временем счета ΔТ и Δt соответственно, при этом ΔТ>>Δt. Делитель на ΔТ 25.4, устройство ручного переключения (многоконтактный ключ) 25.3, делители на четыре 25.6 и 25.11, сумматоры 25.6 и 25.12, вычитатели 25.8 и 25.13, компараторы 25.9, 25.10, 25.14, 25.15, блок памяти 25.5 и два элемента ИЛИ 25.16, 25.17. Счетчики 25.1 и 25.2 могут быть построены на программируемых интервальных таймерах и счетчиках, например, типа К561 ИЕ 14.

Блок «нагрузки» 26 содержит два сумматора 26.1 и 26.2 с разным временем суммирования ΔТ и Δt соответственно, при этом ΔТ≥≥Δt. Делитель на ΔТ 26.3, устройство ручного переключения (многоконтактный ключ) 26.4, делители на четыре 26.6 и 26.11, сумматоры 26.6 и 26.12, вычитатели 26.8 и 26.13, компараторы 26.9, 26.10, 26.14, 26.15, блок памяти 26.5 и два элемента ИЛИ 26.16, 26.17, блок переключения 26.18. Сумматоры 26.1 и 26.2 могут быть построены на программируемых интервальных таймерах и накапливающих сумматорах типа К561 ИМ1.

Блок «сканирования SYN» 27 содержит блок перебора двоичных чисел 27.1, блок отображения числа 27.4, блок памяти 27.3, счетчик с тремя номиналами времени счета ΔT1, ΔT2, ΔТ3 27.2, сумматор на единицу 27.5, блок установления числа 27.6, компаратор 27.7, управляемые переключатели 27.8, 27.9 и 27.10. Блок перебора двоичных чисел 27.1 может быть построен на счетчиках типа К561 ИЕ14. Счетчик 27.2 может быть реализован на микросхемах К561 ИЕ14. Сумматор 27.5 может быть построен на микросхемах К561 ИМ1.

Блок «сканирования FIN» 28 содержит блок перебора двоичных чисел 28.1, блок отображения числа 28.4, блок памяти 28.3, счетчик с тремя номиналами времени счета ΔТ1, ΔТ2, ΔТ3 28.2, сумматор на единицу 28.5, блок установления числа 28.6, компаратор 28.7, управляемые переключатели 28.8, 28.9 и 28.10. Блок перебора двоичных чисел 28.1 может быть построен на счетчиках типа К561 ИЕ14. Счетчик 28.2 может быть реализован на ИМС типа К561 ИЕ14. Сумматор 28.5 может быть построен на ИМС типа К561 ИМ1.

Блок «достоверности» 29 содержит блок памяти 29.1, блок вычисления среднего значения 29.2, делитель на четыре 29.3, сумматор 29.4, вычитатель 29.5, компараторы 29.6 и 29.7, элемент ИЛИ 29.8. Блок вычисления среднего значения 29.2 может быть построен на арифметико-логических устройствах, схемы которых известны и описаны в книге: Угрюмов Е.П. «Цифровая схемотехника»: Справочное пособие. - СПб.: БХВ-Петербург, 2004. В частности, такая схема может быть реализована на микросхемах К555ИПЗ.

Блок управления 33 содержит элементы 2И 33.2, 33.3, 33.4, 33.5, 33.6, 33.7, 33.8, 33.13, 33.14, 33.15, 33.16, линии задержки 33.1, 33.10, 33.11, элемент ИЛИ 33.12, элемент НЕ 33.9, 33.17, генератор импульсов 33.18, счетчик 33.19, триггер 33.20, формирователь импульсов 33.21. В качестве линии задержки может быть использована одна из известных микросхем серии 155, например К155 ИР13, описанная в книге: Шило В.Л. "Популярные цифровые микросхемы". - М.: Радио и связь, 1987. Схема счетчика 33.19 известна и может быть реализована на микросхеме К561ИЕ14. Схема триггера 33.20 известна и может быть реализована на микросхеме К561ТР1. Схемы генератора импульсов 33.18 и формирователя импульсов 33.21 известны и могут быть реализованы на элементах И-НЕ типа К561 ЛН1 c RC-цепью.

Схемы первого 2, второго 5, третьего 7, четвертого 9, пятого 11, шестого 17, седьмого 13, восьмого 15, девятого 19, десятого 21 счетчиков известны и приведены, например, в изобретении №2219577, МПК G06F 17/40 и могут быть реализованы на элементах И типа К561 ЛИ1, счетчиках типа К561 ИЕ14 и дешифраторах типа К 176 ИД2.

Схемы используемых в устройстве поиска информации элементов И, И-НЕ, счетчиков и дешифраторов известны и описаны, например, в книге: Шило В.Л. "Популярные цифровые микросхемы". - М.: Радио и связь, 1987. В частности, схема элемента И может быть реализована на микросхеме К555ЛИ2, элементов И-HE могут быть реализованы на микросхемах К555 ЛР12. Схема счетчика может быть реализована на микросхеме серии К555. Дешифратор может быть реализован на микросхемах дешифраторов, имеющих четыре разряда. В частности, такая схема может быть реализована на микросхеме К555ИД3.

Схемы используемых в устройстве поиска информации элементов ИЛИ известны и описаны, например, в книге: Якубовский С.В. «Цифровые и аналоговые интегральные микросхемы»: Справочник. - М.: Радио и связь, 1990. В частности, схема элемента ИЛИ может быть реализована на микросхеме К555ЛП2.

Схема делителя может быть реализована на регистре сдвига. Схемы сумматоров, вычитателей, компараторов, регистров сдвига, блоков памяти, и программируемых интервальных таймеров известны и описаны, например, в книге: Угрюмов Е.П. «Цифровая схемотехника»: Справочное пособие.- СПб.: БХВ-Петербург, 2004. В частности, схема программируемого интервального таймера может быть реализована на микросхеме ВИ54 серии К 1821 и К 1860. Схемы регистров сдвига могут быть реализованы на микросхеме ИР 13 серии КР1533. Схемы блоков памяти могут быть реализованы на микросхемах К531 РУ9. Схемы сумматоров и вычитателей могут быть реализованы на микросхемах К555 ИМ3. Схемы блоков сравнения 30 и 31 могут быть реализованы на микросхемах КР1533СП1.

Устройства ручного переключения 25.3, 26.18, а также управляемые переключатели 27.8, 27.9, 27.10, 28.8, 28.9 и 28.10 могут быть реализованы на мультиплексорах и демультиплексорах. Схемы которых известны и описаны, например, в книге: Угрюмов Е.П. «Цифровая схемотехника»: Справочное пособие. - СПб.: БХВ-Петербург, 2004. В частности, они строятся на элементах И-НЕ, которые могут быть реализованы на микросхемах К555 ЛР12.

Блоки памяти 25.5, 26.5, а также блоки установления числа 27.6 и 28.6 могут быть реализованы на регистровом запоминающем устройстве (ЗУ). Схемы регистровых ЗУ известны и описаны, например, в книге: Угрюмов Е.П. «Цифровая схемотехника»: Справочное пособие. - СПб.: БХВ-Петербург, 2004.. В частности они могут быть построены на микросхемах КР1533ИР46.

Блоки отображения числа 27.4, 28.4 и блок индикации 34 могут быть построены на индикаторах. Схемы индикаторов известны и описаны, например, в книге: Вениаминов В.Н., Лебедев О.Н., Мирошниченко А.И. «Микросхемы и их применение»: Справочное пособие. - М.: Радио и связь, 1989.

Устройство работает следующим образом. Первый блок памяти 1 предназначен для хранения и последующего считывания с него байтов данных пакета. При получении с выхода блока управления 33 разрешения на запись (логическая «1») производится заполнение ячеек ОЗУ первого блока памяти 1 байтами пакета, поступившими на адресный вход с демодулирующего устройства (канального контроллера). После того как записаны все байты очередного пакета анализируемого протокола, на втором выходе блока памяти 1 формируется разрешение на побайтное считывание информации (логическая «1»). С выхода первого блока памяти 1 байты пакетов последовательно поступают на адресные входы первого 3, второго 4, третьего 12, четвертого 22, пятого 23, шестого 24 блоков дешифрации, а также на входы данных второго 6, третьего 8, четвертого 10, пятого 14, шестого 16, седьмого 18, восьмого 20 блоков памяти.

При поступлении на вход первого счетчика 2 сигнала с блока памяти 1 (логическая «1»), считывается 14 байт для определения в сигнальной цифровой последовательности значения «шесть» (06) в десятичном виде, соответствующего наличию в пакете протокола IP.

В данном описании рассматривается формат кадра Ethernet 802.3/LLC. В случае других типов кадров, например Ethernet DIX (Ethernet II), длина этого поля составляет 2 байта, и его значение равно в десятичном виде числу «восемь» (0800).

Если значение «шесть» не найдено, на втором выходе первого блока дешифрации 3 формируется сигнал логического «0», поступающий на первый вход блока управления 33.

На первом выходе первого дешифратора 3 формируется управляющий сигнал, поступающий на второй счетчик 5, который отсчитывает 4 бита для обнаружения поля длины заголовка и вырабатывает на первом выходе управляющий сигнал разрешения записи этих бит во второй блок дешифрации 4, который служит для определения значения длины заголовка. На выходе второго блока дешифрации 4 формируется сигнал для записи значения длины заголовка во второй блок памяти 6.

На втором выходе второго счетчика 5 формируется управляющий сигнал, поступающий на третий счетчик 7, служащий для отсчета 12 бит для нахождения общего размера IP пакета в сигнально цифровой последовательности и подачи управляющего сигнала разрешения записи этого значения в третий блок памяти 8.

Третий блок памяти 8 хранит значение общего размера пакета и по второму выходу передает его на блок «нагрузки» 26, при этом на первом выходе вырабатывает сигнал для запуска четвертого счетчика 9, который отсчитывает 6 байт для нахождения значения поля TTL пакета и подает управляющий сигнал о разрешении его записи в четвертый блок памяти 10.

Четвертый блок памяти 10 хранит значение поля TTL пакета и по второму выходу передает его на блок «достоверности» 29, при этом на первом выходе вырабатывает сигнал для запуска пятого счетчика 11, который отсчитывает 1 байт для нахождения значения поля, обозначающего протокол вышестоящего уровня пакета, и подает управляющий сигнал о разрешении его записи в третий блок дешифрации 12.

Третий блок дешифраци