Способы компенсирования неэффективности универсальных процессоров при реализации алгоритмов и устройство для их реализации

Иллюстрации

Показать всеИзобретение относится к обработке сигналов при реализации алгоритмов обнаружения сигналов в задачах позиционирования. Схема для обнаружения сигналов позиционирования в мобильном терминале включает в себя универсальный процессор, формирующий команды для выполнения, по меньшей мере, одного алгоритма обнаружения сигналов и выполняющий, по меньшей мере, одну иную функцию, не связанную с алгоритмом обнаружения сигналов, причем схема обнаружения, реагирующая на команды универсального процессора выполнить упомянутый, по меньшей мере, один алгоритм обнаружения сигналов, и, по меньшей мере, один из упомянутого универсального процессора и упомянутой схемы обнаружения, сконфигурированный для выполнения, по меньшей мере, одного процесса повышения эффективности для оптимизации выполнения упомянутого, по меньшей мере, одного алгоритма обнаружения сигналов. Раскрываются также соответствующие способы и реализация их этапов с помощью машиночитаемого носителя информации. Технический результат - обеспечение эффективности обнаружения сигналов с меньшими затратами. 4 н. и 36 з.п. ф-лы, 10 ил.

Реферат

ПЕРЕКРЕСТНАЯ ССЫЛКА НА РОДСТВЕННЫЕ ЗАЯВКИ

Настоящая заявка на патент испрашивает приоритет, в соответствии с §119(e) раздела 35 Кодекса законов США, по предварительной заявке США №60/815,675, озаглавленной «Способы компенсирования неэффективности универсальных процессоров при реализации алгоритмов обнаружения сигналов», поданной 21 июня 2006 г., права на которую принадлежат заявителю данной заявки, и содержание которой полностью включено сюда посредством ссылки.

ОБЛАСТЬ ТЕХНИКИ, К КОТОРОЙ ОТНОСИТСЯ ИЗОБРЕТЕНИЕ

Описанные здесь способы и устройства в целом направлены на решение и компенсирование проблемы неэффективности универсальных процессоров, таких как используемые при реализации обработки сигналов и других алгоритмов, и в частности при реализации алгоритмов обнаружения сигналов в задачах позиционирования.

УРОВЕНЬ ТЕХНИКИ

Многие устройства, такие как мобильные терминалы и подобные им устройства, включают в себя схемы реализации алгоритмов, таких как алгоритмы обнаружения беспроводных сигналов и другие подобные им. При реализации алгоритмов, таких как алгоритмы обнаружения сигналов, имеется необходимость обработки данных с малым временем ожидания, большой частотой прерываний и большой пропускной способностью. Соответственно, для реализации этих алгоритмов обычно использовались аппаратные блоки специального назначения, работающие под управлением заказных микроконтроллеров вместо универсальных процессоров.

Пример такого обычным образом реализованного устройства изображен на Фиг.10, на которой изображена типичная традиционная схема 1000 для использования в мобильных терминалах и других подобных устройствах, имеющая специализированные аппаратные блоки S 1006, управляемые заказным микроконтроллером Pmicro 1004. Такие заказные микроконтроллеры обычно называются процессорами цифровой обработки сигналов (ЦОС), модемами, ЦОС-модемами, поисковыми процессорами и проч. Схема 1000 обычно включает в себя универсальный процессор, например, Pmacro 1002, для обеспечения управления сигналами или для управления блоком Pmicro 1004 через интерфейс шины/памяти 1014. Сигналами управления обычно являются высокоуровневые команды процессора. Управление специальными аппаратными блоками S 1006 выполняется микроконтроллером Pmicro 1004 через интерфейс 1018.

Заказной микроконтроллер Pmicro 1004 данного обычным образом реализованного устройства специально разработан (предназначен) для конкретного приложения. Заказной микроконтроллер Pmicro 1004 выполнен с возможностью выполнения специализированных команд, для того чтобы управлять специализированными аппаратными блоками S 1006. Микроконтроллер Pmicro 1004 обычно сконфигурирован с возможностью поддержания большой частоты прерываний и обеспечения коммуникации со специализированными аппаратными блоками S 1006 через интерфейс с малыми задержками и большой пропускной способностью. Это обеспечивается, в частности, высокой степенью схемной интеграции Pmicro 2004. Описанный тип устройства особенно полезен в цифровой обработке сигналов, в частности в задачах обнаружения сигналов.

Однако использование для таких приложений заказного микроконтроллера, такого как Pmicro 2004 в описанном примере, связано с рядом проблем и недостатков. Например, такие заказные микросхемы характеризуются высокой стоимостью реализации из-за больших размеров кристалла, требующих высоких производственных затрат, большой сложности и т.д. Стоимость дополнительно увеличивают затраты на разработку и поддержку кода, используемого в заказном микроконтроллере, таком как Pmicro 1004. В частности, разработка и поддержка такого кода должна выполняться специализированными разработчиками. Эта специализация может соответствовать конкретному типу задач, для которого используется данный заказной микроконтроллер, и может включать, например, программирование на специализированном ассемблере для данного заказного микроконтроллера и разработку его программно-аппаратной среды.

Стоимость реализации может быть уменьшена за счет отказа от использования заказного микроконтроллера. В отсутствие заказного микроконтроллера в схеме 1000 управление специализированными аппаратными блоками S 1006 должно будет выполняться напрямую универсальным процессором. Однако управление с помощью универсального процессора вызовет столь значительные проблемы и ограничения, включая увеличение времени ожидания, уменьшение поддерживаемой частоты прерываний и уменьшение пропускной способности коммуникационного интерфейса, что опытный специалист должен будет признать неработоспособность такого варианта. В частности, поскольку указанные характеристики ухудшатся на несколько порядков по сравнению со схемами, использующими заказной микроконтроллер, опытный специалист отвергнет такой подход.

Поэтому существует потребность в выполнении сложных алгоритмов обработки сигналов, в частности алгоритмов обнаружения сигналов в задачах позиционирования, более эффективным образом и с меньшими затратами, чем при использовании заказного микроконтроллера обычного типа, обеспечивая в то же время малое время ожидания, поддержку большой частоты прерываний и большую пропускную способность, достигаемые при использовании заказного микроконтроллера.

РАСКРЫТИЕ ИЗОБРЕТЕНИЯ

Описанные здесь способы и устройства отвечают вышеупомянутым требованиям и позволяют устранить недостатки и негативные стороны предшествующего уровня техники благодаря выполнению алгоритма обработки сигналов на универсальном процессоре вместо заказного микроконтроллера, используя при этом один или несколько способов компенсирования неэффективности, позволяющих добиться более эффективной работы этого универсального процессора. Новые способы компенсирования дают значительную экономию в стоимости реализации и другие преимущества, которые будут очевидны из нижеследующего описания.

Наряду с тем, что описанные ниже решения особенно полезны при реализации алгоритмов обнаружения сигналов, применяемых в мобильных терминалах Системы Спутникового Позиционирования (SPS), специалист в данной области техники сможет убедиться, что описанные способы и устройства применимы и в других приложениях, включая любые приложения, требующие обнаружения и демодуляции сигналов, когда может применяться интегрирование на больших длительностях сигнала, а использование заказного микроконтроллера нежелательно. Таким образом, эти способы и устройства могут быть применены к общим процессорам специального назначения, а также к процессорам, выполняющим алгоритмы, не связанные с обработкой сигналов, когда возникают проблемы, аналогичные описанным здесь.

В соответствии с одним вариантом осуществления изобретения, схема для обнаружения сигналов позиционирования в мобильном терминале включает в себя универсальный процессор, формирующий команды для выполнения по меньшей мере одного алгоритма обнаружения сигналов и выполняющий по меньшей мере одну иную функцию, не связанную с алгоритмом обнаружения сигналов, специализированные аппаратные блоки, реагирующие на команды универсального процессора выполнить упомянутый по меньшей мере один алгоритм обнаружения сигналов, и по меньшей мере один из упомянутого универсального процессора и упомянутых специализированных аппаратных блоков, сконфигурированный для выполнения по меньшей мере одного процесса повышения эффективности для оптимизации выполнения упомянутого по меньшей мере одного алгоритма обнаружения сигналов.

Упомянутый, по меньшей мере, один процесс повышения эффективности может включать в себя по меньшей мере один из процесса задания длительности поиска, процесса уменьшения взаимозависимости команд, процесса сокращения обмена данными, процесса организации кода и процесса кэширования памяти. Упомянутый процесс задания длительности поиска может включать в себя выполнение более короткого поиска, когда имеются строгие ограничения по времени, и выполнение более длинного поиска, когда универсальный процессор менее загружен. Процесс уменьшения взаимозависимости команд в свою очередь может включать в себя параллельное выполнение алгоритмов и/или выполнение многозвенных алгоритмов с использованием блоков вычислений с плавающей точкой. Процесс сокращения обмена данными может включать в себя определение важных данных для обмена между универсальным процессором и специализированными аппаратными блоками и передачу универсальному процессору только важных данных. Процесс организации кода может включать в себя по меньшей мере одно из упреждающего выполнения команд и конвейерного выполнения команд. Процесс кэширования памяти может включать в себя кэширование выходных данных специализированных аппаратных блоков, например, когда универсальный процессор занят.

В соответствии с другим вариантом осуществления изобретения, способ обнаружения сигналов позиционирования в мобильном терминале включает следующие этапы: в универсальном процессоре формируют команды для выполнения по меньшей мере одного алгоритма обнаружения сигналов и по меньшей мере одной иной функции, не связанной с алгоритмом обнаружения сигналов; в ответ на команды универсального процессора в специализированных аппаратных блоках выполняют упомянутый по меньшей мере один алгоритм обнаружения сигналов; и выполняют по меньшей мере один процесс повышения эффективности для оптимизации выполнения упомянутого алгоритма.

Этап выполнения, по меньшей мере, одного процесса повышения эффективности может включать в себя по меньшей мере один из следующих этапов: реализуют процесс задания длительности поиска, реализуют процесс уменьшения взаимозависимости команд, реализуют процесс сокращения обмена данными, реализуют процесс организации кода и реализуют процесс кэширования памяти. Этап реализации процесса задания длительности поиска может включать в себя выполнение более короткого поиска, когда имеются строгие ограничения по времени, и выполнение более длинного поиска, когда универсальный процессор менее загружен. Этап реализации процесса уменьшения взаимозависимости команд в свою очередь может включать в себя параллельное выполнение алгоритмов и/или выполнение многозвенных алгоритмов с использованием блоков вычислений с плавающей точкой. Этап реализации процесса сокращения обмена данными может включать в себя определение важных данных для обмена между универсальным процессором и специализированными аппаратными блоками и передачу универсальному процессору только важных данных. Этап реализации процесса организации кода может включать в себя по меньшей мере одно из упреждающего выполнения команд и конвейерного выполнения команд. Этап реализации процесса кэширования памяти может включать в себя кэширование выходных данных специализированных аппаратных блоков, например, когда универсальный процессор занят.

Согласно еще одному варианту осуществления, машиночитаемый носитель информации содержит команды, которые, будучи выполняемыми по меньшей мере одним из универсального процессора и специализированных аппаратных блоков, вызывают обнаружение сигналов позиционирования этими специализированными аппаратными блоками, где упомянутые команды включают в себя команды формирования команд в универсальном процессоре для выполнения по меньшей мере одного алгоритма обнаружения сигналов, команды выполнения в универсальном процессоре по меньшей мере одной иной функции, не связанной с алгоритмом обнаружения сигналов, команды выполнения в специализированных аппаратных блоках, в ответ на команды универсального процессора, упомянутого по меньшей мере одного алгоритма обнаружения сигналов, и команды выполнения, в по меньшей мере одном из упомянутого универсального процессора и упомянутых специализированных аппаратных блоков, по меньшей мере одного процесса повышения эффективности для оптимизации выполнения упомянутого алгоритма.

Команды выполнения по меньшей мере одного процесса повышения эффективности могут включать в себя по меньшей мере одно из следующих: команды выполнения процесса задания длительности поиска, команды выполнения процесса уменьшения взаимозависимости команд, команды выполнения процесса сокращения обмена данными, команды выполнения процесса организации кода и команды выполнения процесса кэширования памяти. Команды выполнения процесса задания длительности поиска могут включать в себя выполнение более короткого поиска, когда имеются строгие ограничения по времени, и выполнение более длинного поиска, когда универсальный процессор менее загружен. Команды выполнения процесса уменьшения взаимозависимости команд в свою очередь могут включать в себя команды для параллельного выполнения алгоритмов и/или для выполнения многозвенных алгоритмов с использованием блоков вычислений с плавающей точкой. Команды выполнения процесса сокращения обмена данными могут включать в себя команды для определения важных данных, требующих обмена между универсальным процессором и специализированными аппаратными блоками, и для передачи только важных данных. Команды выполнения процесса организации кода могут включать в себя по меньшей мере одно из упреждающего выполнения команд и конвейерного выполнения команд. Команды выполнения процесса кэширования памяти могут включать в себя кэширование выходных данных специализированных аппаратных блоков, например, когда универсальный процессор занят.

В соответствии с еще одним аспектом, схема обнаружения сигналов позиционирования в мобильном терминале включает в себя средства для формирования команд в универсальном процессоре для выполнения по меньшей мере одного алгоритма обнаружения сигналов и по меньшей мере одной иной функции, не связанной с алгоритмом обнаружения сигналов, средства для выполнения в специализированных аппаратных блоках, в ответ на команды упомянутого универсального процессора, по меньшей мере одного алгоритма обнаружения сигналов, и средства для выполнения, в по меньшей мере одном из упомянутого универсального процессора и упомянутых специализированных аппаратных блоков, по меньшей мере одного процесса повышения эффективности для оптимизации выполнения упомянутого по меньшей мере одного алгоритма обнаружения сигналов.

Упомянутый по меньшей мере один процесс повышения эффективности может включать в себя по меньшей мере один из следующих процессов: процесс задания длительности поиска, процесс уменьшения взаимозависимости команд, процесс сокращения обмена данными, процесс организации кода и процесс кэширования памяти. Процесс задания длительности поиска может включать в себя выполнение более короткого поиска, когда имеются строгие ограничения по времени, и выполнение более длинного поиска, когда универсальный процессор менее загружен. Процесс уменьшения взаимозависимости команд может включать в себя параллельное выполнение алгоритмов и/или выполнение многозвенных алгоритмов с использованием блоков вычислений с плавающей точкой. Процесс сокращения обмена данными может включать в себя определение важных данных для обмена между универсальным процессором и специализированными аппаратными блоками, и передачу универсальному процессору только важных данных. Процесс организации кода может включать в себя по меньшей мере одно из упреждающего выполнения команд и конвейерного выполнения команд. Процесс кэширования памяти может включать в себя кэширование выходных данных специализированных аппаратных блоков, например, когда универсальный процессор занят.

Дополнительные свойства, преимущества и варианты осуществления описываемых здесь способов и устройств будут очевидны или будут вытекать из рассмотрения нижеследующего подробного описания, чертежей и формулы изобретения. Кроме того, должно быть понятно, что как вышеприведенное изложение сущности изобретения, так и нижеследующее его подробное описание являются примерными и предложены в качестве дополнительного объяснения и не ограничивают объем описываемых способов и устройств, заявленных в формуле изобретения.

КРАТКОЕ ОПИСАНИЕ ЧЕРТЕЖЕЙ

Прилагаемые чертежи, приведенные с целью предоставления лучшего понимания описываемых здесь способов и устройств, иллюстрируют варианты осуществления этих способов и устройств и, будучи включены как часть в подробное описание, служат для объяснения принципов этих способов и устройств. Конструкционные детали этих способов и устройств показаны на чертежах настолько подробно, насколько это необходимо для понимания их и различных вариантов их осуществления. На чертежах:

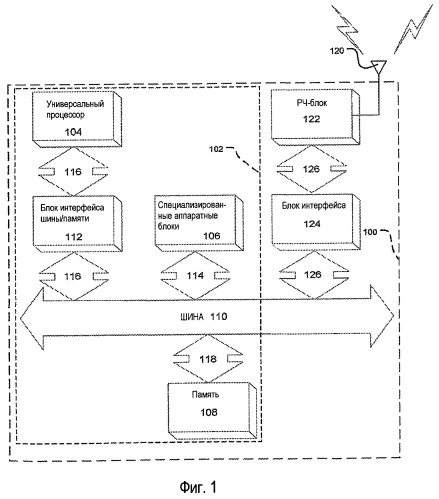

Фиг.1 изображает структурную схему устройства, реализованного в мобильном терминале в соответствии с описанными здесь принципами компенсирования неэффективности универсальных процессоров при реализации алгоритмов;

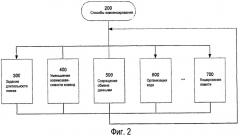

Фиг.2 иллюстрирует блок-схему, показывающую различные способы компенсирования, которые могут применяться для выполнения алгоритмов с помощью универсального процессора вместо заказного контроллера;

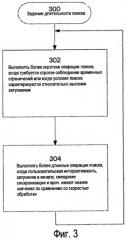

Фиг.3 иллюстрирует блок-схему способа компенсирования путем задания длительности поиска;

Фиг.4 иллюстрирует блок-схему способа компенсирования путем уменьшения взаимозависимости команд;

Фиг.5 иллюстрирует блок-схему способа компенсирования путем сокращения обмена данными;

Фиг.6 иллюстрирует блок-схему способа компенсирования путем организации кода;

Фиг.7 иллюстрирует блок-схему способа компенсирования путем кэширования памяти;

Фиг.8 иллюстрирует структурную схему реализации описываемых здесь принципов, показывающую два различных мобильных терминала в спутниковой и/или сотовой системе;

Фиг.9 иллюстрирует структурную схему устройства, реализованного в соответствии с описанными здесь принципами, которое может быть использовано в других приложениях, чем мобильные терминалы; и

Фиг.10 показывает схему устройства обычного типа с заказным микроконтроллером, управляющим специализированными аппаратными блоками, выполняющими алгоритмы обнаружения цифровых сигналов.

ОСУЩЕСТВЛЕНИЕ ИЗОБРЕТЕНИЯ

Различные варианты осуществления представленных здесь способов и устройств, а также их преимущества, объясняются более подробно на примерах изобретения и вариантах его осуществления, изображенных на прилагаемых чертежах и детализованных в нижеследующем подробном описании, не ограничивающих объем раскрываемого изобретения. Следует отметить, что приведенные на чертежах элементы не обязательно изображены в соответствующем масштабе и что элементы одного варианта осуществления могут использоваться в других вариантах, что будет очевидно специалисту в данной области техники, даже если на это явно не указано в тексте. Описания хорошо известных компонентов и способов обработки могут быть опущены, так чтобы не усложнять без необходимости описание вариантов осуществления изобретения. Использованные здесь примеры предназначены лишь для облегчения понимания того, каким образом можно применять описываемые здесь принципы, способы и устройства, и чтобы тем самым еще более облегчить специалистам использование данного изобретения. Соответственно, описанные здесь примеры и варианты осуществления изобретения не должны истолковываться как ограничивающие его объем, который определен только приложенной формулой изобретения и применимыми законами. Далее, следует иметь в виду, что одинаковые позиции на разных чертежах обозначают одни и те же элементы.

На Фиг.1 проиллюстрирована структурная схема примерного устройства, реализованного в мобильном терминале в соответствии с принципами настоящего изобретения. Более конкретно, пример на Фиг.1 показывает состав и конфигурацию мобильного терминала 100, используемого для приема беспроводных сигналов от системы спутникового позиционирования (SPS) (не показанной на чертеже). Мобильный терминал 100 включает в себя схему 102, в которой может быть реализован некоторый алгоритм, например алгоритм цифровой обработки сигналов для обнаружения или приема сигналов от SPS.

Мобильный терминал 100 может быть выполнен с возможностью работы в беспроводной среде. Более конкретно, мобильный терминал 100 может включать в себя антенну 120 для приема беспроводного сигнала. Беспроводной сигнал может быть сигналом в любой из описанных ниже технологий радиодоступа (RAT). Беспроводной сигнал может приниматься радиочастотным (РЧ) блоком 122 любым способом, хорошо известным в данной области техники. На Фиг.1 показан интерфейсный блок 124, который может взаимодействовать с радиочастотным блоком 122. Интерфейсный блок 124 может содержать один или несколько компонентов, включая сюда интерфейсы 126, 126, для обработки беспроводного сигнала и направления его на схему 102 для дальнейшей обработки, как описано ниже и как хорошо известно специалистам.

Схема содержит специализированные аппаратные блоки 106 для выполнения некоторого алгоритма обработки сигналов, такого как алгоритм обнаружения или приема сигнала. Специализированные аппаратные блоки 106 могут реагировать на данные и/или управляющие сигналы через интерфейс 114 с шиной 110. Управление специализированными аппаратными блоками 106 обеспечивается универсальным процессором 104. Для управления специализированными аппаратными блоками 106 в схеме нет заказного микроконтроллера. Управление специализированными аппаратными блоками 106 может выполняться через блок 112 интерфейса шины/памяти по интерфейсам 116, 116 с шиной 110. Использование такого блока интерфейса факультативно; коммуникации между универсальным процессором 104 и специализированными аппаратными блоками 106 могут осуществляться любым известным способом.

Схема 102 может дополнительно содержать память 108, подключенную к шине 110 через интерфейс 118. Кроме того, универсальный процессор 104 может включать в себя аппаратный ускоритель, как это хорошо известно специалистам. Следует иметь в виду, что на Фиг.1 показан лишь пример комбинации различных компонентов. В этом отношении схема 102 может включать в себя большее или меньшее число компонентов, другие комбинации большего или меньшего числа компонентов и т.д. Комбинация компонентов на Фиг.1 является лишь примерной, и другие комбинации также соответствуют духу и объему настоящего изобретения, если только они не содержат в составе схемы 102 заказного микроконтроллера для управления специализированными аппаратными блоками 106. Отсутствие заказного микроконтроллера значительно уменьшает стоимость реализации схемы 102. Более конкретно, схема 102 может быть реализована с меньшими затратами благодаря, в частности, уменьшению размеров и сложности кристалла микросхемы. Далее, затраты на реализацию схемы 102 уменьшаются по сравнению с вариантом, требующим составления и поддержки программного кода для заказного микроконтроллера. При этом, однако, без описанных ниже конфигураций и/или способов компенсирования неэффективности в соответствии с настоящим изобретением, схема 102 будет иметь, по сравнению с обычной схемой, использующей заказной микроконтроллер (как показано на Фиг.10), многочисленные недостатки, существенное (на порядок) ухудшение параметров, включая высокие задержки, низкую поддерживаемую частоту прерываний, ограниченную скорость передач и т.д.

Различные способы уменьшения недостатков и компенсирования неэффективности универсального процессора при реализации алгоритмов без использования заказного микроконтроллера, соответствующие настоящему изобретению, описаны ниже по отдельности. На Фиг.2, однако, графически показано, что один или несколько предлагаемых в данном изобретении способов могут использоваться совместно. Таким образом, имеется возможность как совместного использования предлагаемых в изобретении способов компенсирования, так и отдельной реализации одного или нескольких таких способов.

На Фиг.3 показана блок-схема предлагаемого согласно данному изобретению способа компенсирования путем задания длительности поиска. Более конкретно, Фиг.3 иллюстрирует способ 300 задания длительности поиска, согласно которому в каждой команде на выполнение алгоритмов обнаружения сигналов путем поиска, поданной специализированным аппаратным блокам 106, задается своя длительность поиска. Увеличение длительности поиска при выполнении определенных задаваемых командами сценариев позволяет минимизировать поток управляющих данных. Более того, выборочное увеличение длительности операций поиска позволит избежать негативного влияния на общую производительность алгоритма благодаря выполнению укороченного поиска в тех случаях, когда это необходимо.

В частности, изменение длительности поиска может быть сделано исходя из ограничений по времени и условий поиска. На этапе 302, способ задания длительности поиска может задать укорочение отдельных операций поиска, и таким образом увеличить скорость их выполнения, когда данное приложение требует строгого соблюдения временных ограничений или когда условия поиска характеризуются относительно высоким затуханием.

Изменение длительности поиска может также основываться на других критериях. Согласно одному аспекту настоящего изобретения, для показанного на Фиг.3 способа 300 задания длительности поиска может быть использован тот факт, что ограничения на длину индивидуальных команд поиска, посылаемых специализированным аппаратным блокам 106, могут быть получены из высокоуровневых параметров приложения. Такие высокоуровневые параметры приложения могут включать в себя факторы пользовательской интерактивности, низкоуровневых параметров канала и аналогичные факторы, например, когда пользовательская интерактивность выше миллисекунды или микросекунды. Факторы пользовательской интерактивности могут включать в себя, например, такое приложение позиционирования, при котором требуется вычислять местоположение мобильного пользователя исходя из результатов, получаемых устройством поиска с некоторой номинальной частотой, например 1 раз в секунду. Поскольку не предполагается, что местоположение пользователя изменяется очень быстро, нет нужды выполнять новую операцию позиционирования, а следовательно, и новый поиск с большей частотой, чем упомянутая номинальная частота. Другим примером является поддержка хэндовера (эстафетной передачи) при перемещении пользователя из одной ячейки сотовой сети в другую. Периодическим опросом сигналов в соответствующем диапазоне (обнаружение и/или демодуляция сигнала) можно обнаружить сигналы от новой базовой станции и таким образом запустить процесс хэндовера. Частота выполнения поиска и в этом случае тоже может быть невысокой, например не выше чем 1/мс. Низкоуровневые параметры канала могут включать в себя коэффициент затухания, смещение синхронизации и т.д.

Как показано на этапе 304, когда обнаруживается, что пользовательская интерактивность, затухание в канале, смещение синхронизации имеют низкие значения по сравнению со скоростью обработки универсальным процессором 104, или при других аналогичных условиях, операции поиска могут быть более длительными, с соблюдением при этом требуемой их частоты. Разумеется, длительность поиска может быть изменена на основе любого критерия с целью сделать обеспечения более эффективной работы универсального процессора 104.

Соответственно, выборочно меняя длительность поиска в каждой команде, подаваемой специализированным аппаратным блокам 106, можно минимизировать управление вызовами при минимальном влиянии на общую производительность алгоритма.

На Фиг.4 проиллюстрирована блок-схема способа компенсирования путем уменьшения взаимозависимости команд, предлагаемого согласно данному изобретению. В частности, этот вариант изобретения уменьшает зависимость между командами, посылаемыми специализированным аппаратным блокам 106, как показано на этапе 400. На этапе 402 уменьшение зависимости между командами производится, во-первых, на основании того факта, что многие команды поиска могут считаться независимыми друг от друга и могут выполняться параллельно на специализированных аппаратных блоках 106. Более конкретно, как показано на этапе 402, поиск при различных параметрах, таких как различные предположения о времени, частоте, коде, может выполняться параллельно. Такой параллельный поиск дает возможность получать результаты поиска с большей скоростью.

Далее, в подходах, известных из уровня техники, как правило, требуется, чтобы многозвенные операции поиска выполнялись последовательно для данной комбинации предполагаемых временных и частотных кодов. Частично это было вызвано ограничениями на динамический диапазон операций поиска. Например, операции поиска должны были выполняться так, чтобы покрыть каждый 1/N сегмент требуемого динамического диапазона. Эти N операций поиска обычно должны были выполняться последовательно, взаимозависимым образом, чтобы уменьшить необходимость поиска ненужных сигналов в неиспользуемых диапазонах. Такой последовательный режим увеличивал количество времени, необходимое на выполнение N операций поиска.

Как показано на этапе 404, поиск согласно настоящему изобретению может быть выполнен с использованием блоков вычислений с плавающей точкой. Использование блоков вычислений с плавающей точкой позволяет покрыть весь динамический диапазон в одной операции поиска. Взаимозависимость команд здесь устраняется благодаря уменьшению числа операций поиска и устранению необходимости последовательного выполнения поиска. Таким образом сильно сокращается время выполнения процесса поиска. Кроме того, в других алгоритмах могут использоваться блоки вычислений с плавающей точкой и параллельный способ выполнения. Таким образом, согласно различным вариантам осуществления способов, показанным на Фиг.4, уменьшают зависимость между командами и тем самым сокращают время выполнения операций поиска.

На Фиг.5 проиллюстрирована блок-схема способа компенсирования путем сокращения обмена данными, предлагаемого согласно данному изобретению. Этот вариант осуществления способа согласно данному изобретению специально направлен на сокращение обмена данными между универсальным процессором 104 и специализированными аппаратными блоками 106. В частности, в этом аспекте изобретения используется преимущество того факта, что алгоритмы, как правило, формируют большой объем данных, касающихся обнаружения сигналов, из которого необходима только некоторая часть данных. Путем определения, какие именно данные требуют просмотра («блок важных данных»), и передачи только этих данных между специализированными аппаратными блоками 106 и универсальным процессором 104 можно уменьшить общий объем пересылаемых данных. Например, для алгоритмов обнаружения сигналов необходима проверка только тех данных, которые связаны с самым высоким пиком сигнала или с некоторыми из самых высоких пиков для обнаружения сигналов.

На этапе 502, конкретный специализированный аппаратный блок 106 может определить, какие данные являются важными и должны быть проанализированы универсальным процессором 104. Например, при обработке сигналов это может быть сделано с помощью сортировщика пиков, реализованного в упомянутом специализированном аппаратном блоке 106. Сортировщик пиков может определить индекс и величину одного или нескольких самых высоких пиков. На этапе 504, только самый высокий пик и/или данные о самых высоких пиках передаются универсальному процессору 104. «Менее важные» данные не посылаются универсальному процессору 104, и таким образом объем обмена данными сокращается, давая возможность универсальному процессору 104 работать более эффективно.

На Фиг.6 показана блок-схема способа компенсирования путем организации кода, предлагаемого согласно данному изобретению. В этом варианте осуществления изобретения могут использоваться некоторые из этапов, показанных на Фиг.5, а также могут применяться различные подходы к оптимизации кода. Более конкретно, этот аспект изобретения может использовать различные виды организации кода в универсальном процессоре 104 с целью более эффективного выполнения алгоритма.

Из разнообразных видов процесса 600 организации кода, которые могут использоваться согласно этому варианту осуществления данного изобретения, некоторые могут включать в себя упреждающее и/или конвейерное выполнение команд в универсальном процессоре 104 и/или в специализированных аппаратных блоках 106. Упреждающее выполнение может рассматриваться как подпроцедура, пытающаяся предвидеть результат выбора переменной ветвления для оценки одного из ее значений. Две основные задачи при упреждающем выполнении состоят в выборе очередной переменной ветвления для оценки следующего и порядка присваиваемых ей значений. Конвейерное выполнение может использовать набор последовательно соединенных модулей обработки данных, так что выход одного элемента является входом следующего. Конвейерное выполнение уменьшает длительность рабочего цикла процессора и увеличивает поток команд и количество команд, которые могут быть выполнены за единицу времени. Конвейерное выполнение может предотвращать задержки на ветвление и другие проблемы, связанные с последовательным выполнением команд.

Соответственно, использование упреждающего и/или конвейерного выполнения команд совместно со способом сокращения обмена данными, показанным на Фиг.5, обеспечивает более эффективное выполнение алгоритмов универсальным процессором 104. Кроме того, здесь имеются в виду и рассматриваются как принадлежащие объему настоящего изобретения и другие способы организации кода, известные в данной области техники.

На Фиг.7 проиллюстрирована блок-схема способа компенсирования путем кэширования памяти, предлагаемого согласно данному изобретению. В частности, использование буферов памяти скрывает или уменьшает задержки в универсальном процессоре 104 и позволяет специализированным аппаратным блокам 106 работать более эффективно. Более конкретно, этот аспект данного изобретения позволяет использовать процесс 700 кэширования памяти для обеспечения более эффективной реализации алгоритмов. Например, выходные данные конкретного специализированного аппаратного блока 106 могут быть, как показано на этапе 702, буферизованы на то время, пока универсальный процессор 104 недоступен. В этом отношении эффективность работы универсального процессора 104 может страдать из-за различных проблем, связанных с задержками. Кроме того, наличие различных ограничений на выделение памяти, определенных процессами Фиг.3 и Фиг.5 данного изобретения, минимизирует скорость передачи выходных данных от специализированных аппаратных блоков 106, задерживая их отправку универсальному процессору 104. Чтобы справиться с этим ограничением, данные, необходимые универсальному процессору 104, могут быть помещены в буфер памяти. Соответственно, использование буферов памяти уменьшает или скрывает задержки в универсальном процессоре 104 и позволяет специализированным аппаратным блокам 106 работать более эффективно.

Описанная здесь техника определения местоположения, включая прием и обработку сигналов, может использоваться в различных беспроводных коммуникационных сетях 906, таких как изображенная на Фиг.8 сеть с антенной 904 для связи с различными мобильными терминалами 100 или как беспроводная глобальная сеть (WWAN), беспроводная локальная сеть (WLAN), беспроводная персональная сеть (WPAN) и т.д. Под мобильным терминалом (MS) здесь понимается такое устройство, как сотовый телефон, беспроводное коммуникационное устройство, пользовательское оборудование, другое устройство в сетях персональных коммуникаций (PCS), устройство определения местоположения с помощью той или иной техники позиционирования и т.п. Термины «сеть» и «система» часто применяются взаимозаменяемым образом. Сеть WWAN может быть сетью многостанционного доступа с кодовым разделением каналов (CDMA), сетью многостанционного доступа с временным разделением каналов (TDMA), сетью множественного доступа с частотным разделением (FDMA), сетью множественного доступа с ортогональным частотным раздел