Приемник для сети беспроводной связи с расширенным диапазоном

Иллюстрации

Показать всеИзобретение относится к области беспроводной связи и, в частности, к обнаружению и демодуляции сигнала. Техническим результатом является обеспечение сети беспроводной связи и станции, функционирования с расширенным диапазоном покрытия. Указанный технический результат достигается тем, что обнаружение сигналов выполняется в несколько этапов с использованием корреляции во временной области для первого этапа, обработки в частотной области для второго этапа и обработки во временной области для третьего этапа. Для первого этапа формируют произведения символов по меньшей мере для двух разных задержек, выполняют корреляцию между произведениями для каждой задержки и известными значениями и результаты корреляции для всех задержек объединяют и используют для объявления наличия сигнала. Для демодуляции регулируют синхронизацию входных выборок для получения отрегулированных по времени выборок. Уход частоты оценивают и удаляют из отрегулированных по времени выборок для получения выборок с частотной коррекцией, которые обрабатывают с помощью оценки канала для получения обнаруженных символов. Фазы обнаруженных символов корректируют для получения символов с фазовой коррекцией, которые демодулируют, обратно перемежают и декодируют. 8 н. и 32 з.п. ф-лы, 11 ил., 1 табл.

Реферат

ОБЛАСТЬ ТЕХНИКИ, К КОТОРОЙ ОТНОСИТСЯ ИЗОБРЕТЕНИЕ

Настоящее раскрытие изобретения в целом относится к связи, а конкретнее к приемнику для беспроводной связи.

УРОВЕНЬ ТЕХНИКИ

Сети беспроводной связи широко используются для предоставления различных услуг связи, например данных, речи, видео и т.д. Эти сети включают в себя беспроводные региональные сети радиосвязи (WWAN), которые обеспечивают зону радиосвязи для больших географических областей (например, городов), беспроводные локальные вычислительные сети (WLAN), которые обеспечивают зону радиосвязи для географических областей среднего размера (например, зданий и кампусов), и персональные беспроводные сети (WPAN), которые обеспечивают зону радиосвязи для небольших географических областей (например, домов). Беспроводная сеть обычно включает в себя одну или несколько точек доступа (или базовых станций), которые поддерживают связь для одного или нескольких терминалов пользователей (или беспроводных устройств).

IEEE 802.11 является семейством стандартов, разработанных Институтом инженеров по электротехнике и электронике (IEEE) для WLAN. Эти стандарты описывают беспроводной интерфейс между точкой доступа и терминалом пользователя или между двумя терминалами пользователя. Стандарт IEEE 802.11 редакции 1999 (или просто «802.11»), который озаглавлен «Part 11: Wireless LAN Medium Access Control (MAC) and Physical Layer (PHY) Specifications» (Часть 11: Спецификации протокола управления доступом к среде передачи (MAC) и протокола физического уровня (PHY) для беспроводной LAN), поддерживает скорости передачи данных в 1 и 2 мегабит в секунду (Мбит/с) в частотном диапазоне 2,4 гигагерц (ГГц), используя либо расширение спектра путем скачкообразной перестройки частоты (FHSS), либо расширение спектра методом прямой последовательности (DSSS). Стандарт IEEE 802.11a-1999 (или просто «802.11a») является дополнением к 802.11, использует мультиплексирование с ортогональным частотным разделением каналов (OFDM) вместо FHSS или DSSS и поддерживает скорости передачи данных до 54 Мбит/с в частотном диапазоне 5 ГГц. Стандарт IEEE 802.11b-1999 (или просто «802.11b») является другим дополнением к 802.11 и использует DSSS для поддержки скоростей передачи данных до 11 Мбит/с. Стандарт IEEE 802.11g-2003 (или просто «802.11g») является еще одним дополнением к 802.11, использует DSSS и OFDM и поддерживает скорости передачи данных до 54 Мбит/с в полосе 2,4 ГГц. Эти разные стандарты общеизвестны в данной области техники и являются общедоступными.

Наименьшая скорость передачи данных, поддерживаемая 802.11, 802.11a, 802.11b и 802.11g, равна 1 Мбит/с. Для 802.11b и 802.11g (или просто «802.11b/g») для отправки передачи (передаваемых данных) на наименьшей скорости передачи (данных) в 1 Мбит/с используются особая схема DSSS и особая схема модуляции. DSSS и схема модуляции для 1 Мбит/с требуют определенного минимального отношения уровня сигнала к совокупному уровню взаимных помех и шумов (SNR) для надежного приема передачи (передаваемых данных). Диапазон передачи (передаваемых данных) затем определяется географической областью, в пределах которой приемная станция может достигать требуемого или лучшего SNR. В некоторых случаях желательно отправлять передачи (передаваемые данные) с диапазоном, который больше диапазона для наименьшей скорости передачи данных, поддерживаемой 802.11b/g.

Следовательно, в данной области техники имеется необходимость в сети беспроводной связи и станции, допускающих функционирование с расширенным диапазоном покрытия.

СУЩНОСТЬ ИЗОБРЕТЕНИЯ

В этом документе описываются методики для обнаружения и демодуляции сигнала/передачи (передаваемых данных) в плохих канальных условиях (например, низкое SNR). В одном аспекте обнаружение сигнала выполняют в несколько этапов, используя разные типы обработки сигнала для достижения хорошей эффективности обнаружения. В варианте осуществления обнаружение сигналов выполняют с использованием корреляции во временной области для первого этапа, обработки в частотной области для второго этапа и обработки во временной области для третьего этапа. Обнаружение сигнала для каждого этапа можно дополнительно выполнять на основе адаптивной (самонастраивающейся) пороговой величины, которую выводят на основании принятой энергии для интервала (окна) символов, для того чтобы эффективность обнаружения была менее чувствительной к уровню принятого сигнала. Наличие сигнала может быть объявлено на основании результатов всех трех этапов.

В аспекте первого этапа входные выборки на приемной станции могут быть кодированы с сужением спектра с помощью кодовой последовательности для формирования суженных символов. Затем формируют произведения суженных символов по меньшей мере для двух задержек, например 1-символьной и 2-символьной задержек. Выполняют корреляцию между произведениями для каждой задержки и известными значениями для той задержки. Затем объединяют результаты корреляции для всех задержек, например, некогерентно или когерентно для множества предполагаемых фаз. Наличие сигнала и синхронизация сигнала могут быть определены на основании объединенных результатов корреляции.

В другом аспекте демодуляцию выполняют таким образом, чтобы достичь хорошей эффективности при плохих канальных условиях. В варианте осуществления синхронизацию входных выборок регулируют (например, с помощью многофазного фильтра) для получения отрегулированных по времени выборок. Уход частоты оценивают и удаляют из отрегулированных по времени выборок для получения выборок с частотной коррекцией, которые обрабатывают с помощью оценки канала (например, используя многоотводный (рейк) приемник) для получения обнаруженных символов. Фазы обнаруженных символов корректируют для получения символов с фазовой коррекцией. Затем над символами с фазовой коррекцией выполняют демодуляцию для получения демодулированных символов, которые обратно перемежают и декодируют для получения декодированных данных.

Обработка сигнала для каждого этапа обнаружения и для демодуляции подробно описывается ниже. Различные аспекты и варианты осуществления изобретения также описываются ниже.

КРАТКОЕ ОПИСАНИЕ ЧЕРТЕЖЕЙ

Признаки и сущность настоящего изобретения станут более очевидными из изложенного ниже подробного описания, рассматриваемого совместно с чертежами, на которых одинаковые номера позиций определяют соответственно по всему документу.

Фиг.1 показывает передающую станцию и приемную станцию.

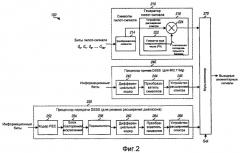

Фиг.2 показывает процессор передачи в передающей станции.

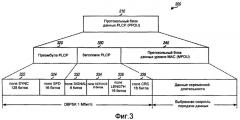

Фиг.3 показывает структуру PPDU, используемую 802.11b/g.

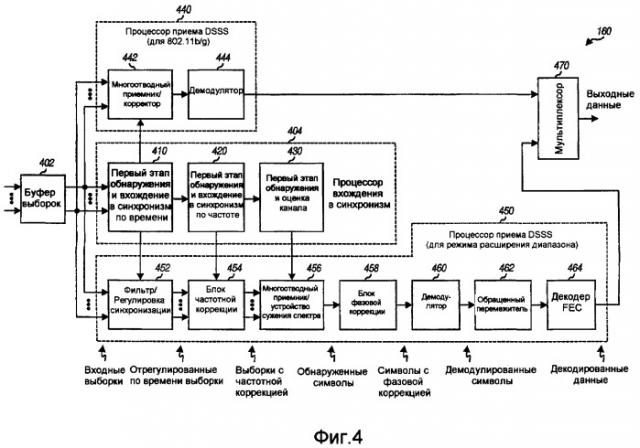

Фиг.4 показывает процессор приема в приемной станции.

Фиг.5 показывает первый этап обнаружения и блок вхождения в синхронизм по времени.

Фиг.6 показывает второй этап обнаружения и блок вхождения в синхронизм по частоте.

Фиг.7 показывает третий этап обнаружения и блок оценки канала.

Фиг.8 показывает блок фазовой коррекции.

Фиг.9 показывает процесс для выполнения обнаружения сигнала для первого этапа.

Фиг.10 показывает процесс для выполнения обнаружения сигнала с несколькими этапами.

Фиг.11 показывает процесс для приема передачи (передаваемых данных).

ПОДРОБНОЕ ОПИСАНИЕ

Слово «типовой» используется в данном документе, чтобы обозначать «служащий в качестве примера, отдельного случая или иллюстрации». Любой вариант осуществления или образец, описанный в данном документе как «типовой», не обязательно должен быть истолкован как предпочтительный или выгодный по сравнению с другими вариантами осуществления или образцами.

Фиг.1 показывает блок-схему передающей станции 110 и приемной станции 150 в беспроводной сети 100. Передающая станция 110 оборудована одной антенной и может быть точкой доступа или терминалом пользователя. Приемная станция 150 оборудована несколькими (например, R=2) антеннами и также может быть точкой доступа или терминалом пользователя. Вообще, каждая станция может быть оборудована любым количеством антенн, которые могут использоваться для передачи и приема данных. Точкой доступа обычно является стационарная станция, которая обменивается информацией с терминалами пользователя и также может называться базовой станцией, базовой приемопередающей системой (BTS) или какой-либо другой терминологией. Терминал пользователя может быть стационарным или мобильным и также может называться мобильной станцией, беспроводным устройством, абонентским оборудованием (UE) или какой-либо другой терминологией.

На передающей станции 110 процессор 130 передачи принимает данные трафика от источника 120 данных, обрабатывает данные трафика в соответствии со скоростью передачи данных, выбранной для передачи, и предоставляет выходные элементарные сигналы. Ниже описывается обработка процессором 130 передачи. Модуль 132 передатчика (TMTR) обрабатывает (например, преобразует в аналоговую форму, усиливает, фильтрует и преобразует с повышением частоты) выходные элементарные сигналы и формирует модулированный сигнал, который передается через антенну 134.

На приемной станции 150 R антенн 152a-152r принимают переданный сигнал, и каждая антенна 152 предоставляет принятый сигнал соответствующему модулю 154 приемника (RCVR). Антенна также может называться «разнесением», и R приемных антенн обеспечивают кратность R разнесения. Каждый модуль 154 приемника обрабатывает свой принятый сигнал и предоставляет поток входных выборок процессору 160 приема. Процессор 160 приема обрабатывает входные выборки от всех R модулей 154a-154r приемника способом, дополнительным к обработке, выполненной процессором 130 передачи, и предоставляет декодированные данные приемнику 170 данных. Декодированные данные являются оценкой данных трафика, отправленных передающей станцией 110.

Процессоры 140 и 180 управляют работой блоков обработки на передающей станции 110 и приемной станции 150 соответственно. Запоминающие устройства 142 и 182 хранят данные и/или программные коды, используемые процессорами 140 и 180 соответственно.

Станции 110 и 150 могут поддерживать 802.11b и/или 802.11g. 802.11g обратно совместим с 802.11b и поддерживает все режимы работы, определенные 802.11b. Станции 110 и 150 могут дополнительно поддерживать режим расширения диапазона, который поддерживает по меньшей мере одну скорость передачи данных, которая меньше наименьшей скорости передачи данных в 802.11b/g. Меньшая скорость (скорости) передачи данных может использоваться для расширения диапазона покрытия, который выгоден для некоторых применений, например портативных раций.

Таблица 1 перечисляет две наименьшие скорости передачи данных, поддерживаемые 802.11b и 802.11g и обработку для каждой скорости передачи данных. Таблица 1 также перечисляет три скорости передачи данных, поддерживаемые режимом расширения диапазона, и обработку для каждой скорости передачи данных в соответствии с вариантом осуществления. В Таблице 1 DBPSK обозначает дифференциальную двухпозиционную фазовую манипуляцию, а DQPSK обозначает дифференциальную квадратурную фазовую манипуляцию.

| Таблица 1 | |||||

| Режим | Скорость передачи данных | Кодовая скорость | Модуляция | Кодирование с расширением спектра | Эффективность |

| 802.11b/g | 2 Мбит/с | нет | DQPSK | DSSS | 2 бит/символ |

| 1 Мбит/с | нет | DBPSK | DSSS | 1 бит/символ | |

| Режим расшире-ния диапазона | 1 Мбит/с | 1/2 | DQPSK | DSSS | 1 бит/символ |

| 500 Кбит/с | 1/2 | DBPSK | DSSS | 0,5 бит/символ | |

| 250 Кбит/с | 1/4 | DBPSK | DSSS | 0,25 бит/символ |

Для ясности в последующем описании термин «бит» относится к количеству до модуляции (или преобразованию символов) на передающей станции, термин «символ» относится к количеству после преобразования символов и термин «элементарный сигнал» относится к количеству после спектрального кодирования с расширением спектра. Термин «выборка» относится к количеству до спектрального кодирования с сужением спектра на приемной станции.

Фиг.2 показывает вариант осуществления процессора 130 передачи на передающей станции 110. Процессор 130 передачи включает в себя генератор 210 пилот-сигнала, процессор 240 передачи DSSS для 802.11b/g, процессор 250 передачи DSSS для режима расширения диапазона и мультиплексор (Mux) 270.

Генератор 210 пилот-сигнала формирует пилот-сигнал (который также называется преамбулой или опорным сигналом) как для 802.11b/g, так и для режима расширения диапазона. В генераторе 210 пилот-сигнала преобразователь 214 символов принимает биты пилот-сигнала, преобразует эти биты в символы модуляции на основе BPSK и предоставляет символы пилот-сигнала устройству 216 расширения спектра. Для целей данного документа символом пилот-сигнала является символ модуляции для пилот-сигнала, символом данных является символ модуляции для данных трафика, символ модуляции является комплексной величиной для точки в сигнальном созвездии для схемы модуляции (например, для M-PSK или M-QAM), и символ является любой комплексной величиной. Устройство 216 расширения спектра спектрально расширяет символы пилот-сигнала и предоставляет выходные элементарные сигналы. В устройстве 216 расширения спектра генератор 222 кода псевдослучайного числа (PN) формирует кодовую последовательность PN. В некоторых вариантах осуществления это может называться последовательностью Баркера. Последовательность Баркера длиной в 11 элементарных сигналов обладает скоростью передачи в 11 миллионов элементарных сигналов в секунду (Mcps) и состоит из следующей 11-сигнальной последовательности {+1, -1, +1, +1, -1, +1, +1, +1, -1, -1, -1}. Умножитель 224 принимает символы пилот-сигнала на скорости в 1 миллион символов в секунду (Msps) от преобразователя 214 символов и последовательность Баркера от генератора 222 кода PN. Умножитель 224 умножает каждый символ пилот-сигнала на все 11 элементарных сигналов из последовательности Баркера, формирует 11 выходных элементарных сигналов для каждого символа пилот-сигнала и предоставляет последовательность выходных элементарных сигналов для пилот-сигнала. Выходная скорость передачи элементарного сигнала в 11 раз выше скорости передачи символа пилот-сигнала, или 11 Mcps. Каждый выходной элементарный сигнал является комплексной величиной, которую необходимо отправить в один период Tc элементарного сигнала, который равен приблизительно 90,9 наносекунд (нс) для 802.11b/g.

Процессор 240 передачи DSSS выполняет дифференциальную модуляцию и спектральное кодирование с расширением спектра для 802.11b/g. В процессоре 240 дифференциальный кодер 242 принимает информационные биты для данных трафика, выполняет дифференциальное кодирование информационных битов для DBPSK или DQPSK и предоставляет дифференциально-кодированные биты. Для DBPSK информационный бит «0» приводит к изменению фазы в 0°, а информационный бит «1» приводит к изменению фазы в 180°. Для DQPSK пара информационных битов «00» приводит к изменению фазы в 0°, пара информационных битов «01» приводит к изменению фазы в +90°, пара информационных битов «11» приводит к изменению фазы в +180° и пара информационных битов «10» приводит к изменению фазы в +270°. В некоторых вариантах осуществления преобразователь 244 символов преобразует дифференциально-кодированные биты в символы модуляции на основе BPSK для скорости передачи данных в 1 Мбит/с и на основе QPSK для скорости передачи данных в 2 Мбит/с. Тем не менее, могут использоваться другие схемы модуляции для скоростей передачи. Преобразователь 244 символов предоставляет символы модуляции BPSK на скорости в 1 Msps для скорости передачи данных 1 Мбит/с и предоставляет символы модуляции QPSK на скорости 1 Msps для скорости передачи данных 2 Мбит/с. Устройство 246 расширения спектра спектрально расширяет символы данных из преобразователя 244 символов и предоставляет выходные элементарные сигналы для данных трафика.

Процессор 250 передачи DSSS выполняет кодирование с прямым исправлением ошибок (FEC), преобразование символов и спектральное кодирование с расширением спектра для режима расширения диапазона. В процессоре 250 кодер 252 FEC принимает информационные биты для данных трафика, кодирует информационные биты в соответствии со схемой кодирования FEC и предоставляет кодовые биты. Кодер 252 FEC может обеспечивать выполнение сверточного кода, турбо-кода, кода разреженного контроля четности (LDPC), блочного кода, какого-либо иного кода или их сочетания. Блок 254 повторения/исключения может либо повторять, либо исключать некоторые или все кодовые биты для получения нужной кодовой скорости. Перемежитель 256 перемежает или переупорядочивает кодовые биты на основе схемы перемежения. Дифференциальный кодер 262 выполняет дифференциальное кодирование перемеженных битов, например для DBPSK или DQPSK, и предоставляет дифференциально-кодированные биты. Преобразователь 264 символов преобразует дифференциально-кодированные биты в символы модуляции на основе схемы модуляции, например BPSK или QPSK. Устройство 266 расширения спектра спектрально расширяет символы данных из преобразователя 264 символов и предоставляет выходные элементарные сигналы для данных трафика. Устройства 246 и 266 расширения спектра могут реализовываться так же, как и устройство 216 расширения спектра, и могут расширять каждый символ данных с помощью 11-сигнальной последовательности Баркера для формирования 11 выходных элементарных сигналов для этого символа данных.

Мультиплексор 270 принимает выходные элементарные сигналы от генератора 210 пилот-сигнала и процессоров 240 и 250 передачи DSSS, предоставляет выходные элементарные сигналы для пилот-сигнала в нужное время, предоставляет выходные элементарные сигналы от процессора 240, если выбирается режим 802.11b/g, и предоставляет выходные элементарные сигналы от процессора 250, если выбирается режим расширения диапазона.

Для IEEE 802.11 данные обрабатываются посредством уровня протокола управления доступом к среде передачи (MAC) в качестве протокольных блоков данных уровня MAC (MPDU). Каждый MPDU обрабатывается протоколом конвергенции физического уровня (PLCP) и помещается в протокольный блок данных PLCP (PPDU). Каждый PPDU обрабатывается физическим уровнем (как показано на фиг.2) и передается через радиоканал.

Фиг.3 показывает структуру 300 PPDU, используемую 802.11b/g. Для структуры 300 PPDU, PPDU 310 включает в себя преамбулу 320 PLCP, заголовок 330 PLCP и MPDU 340. MPDU 340 служит носителем данных трафика для PPDU 310 и имеет переменную длину. Преамбула 320 PLCP включает в себя поле 322 синхронизации PLCP (SYNC) и поле 324 ограничителя начала кадра (SFD). Поле 322 SYNC служит носителем фиксированной 128-битной последовательности, которая может использоваться приемной станцией для обнаружения сигнала, вхождения в синхронизм и других целей. Биты в 128-битной последовательности обозначаются d 0, d 1,…, d 127 . Поле 324 SFD служит носителем фиксированной 16-битной последовательности, которая указывает начало заголовка PLCP. Заголовок 330 PLCP включает в себя поле 332 SIGNAL, которое указывает скорость передачи данных для MPDU, поле 334 SERVICE, которое устанавливается в «0» для обозначения соответствия IEEE 802.11, поле 336 LENGTH, которое указывает количество времени (в единицах, равных миллисекундам), требуемое для отправки MPDU 340, и поле 338 CRC, которое служит носителем значения CRC, сформированного на основе полей SIGNAL, SERVICE и LENGTH. Преамбула 320 PLCP и заголовок 330 PLCP отправляются на скорости 1 Мбит/с с использованием DBPSK. Преамбула 320 PLCP содержит в целом 144 бита, которые обрабатываются для формирования 144 символов BPSK. Каждый символ BPSK состоит из 11 выходных элементарных сигналов, которые получаются путем кодирования с расширением спектра этого символа BPSK с помощью 11 элементарных сигналов из последовательности Баркера. 144 символа BPSK передаются в 144 периодах символов, при этом каждый период символа имеет длительность в 1 микросекунду (мкс).

Для режима расширения диапазона может использоваться структура 300 PPDU или другая структура PPDU. Структура PPDU для режима расширения диапазона может включать в себя поле SYNC, поле CHANEST, которое служит носителем фиксированной (например 32-битной) последовательности, используемой для оценки канала, одно или несколько полей сигнализации и MPDU.

Приемная станция 150 выполняет вхождение в синхронизм для обнаружения PPDU, отправленных передающей станцией 110. Вхождение в синхронизм для режима расширения диапазона более перспективно, чем обычное вхождение в синхронизм для 802.11b/g вследствие следующих отличий:

1. Низкое SNR/разнесение. Требуемое отношение энергии бита к общему уровню шума (Eb/No) ниже, например для 802.11b/g оно приблизительно 8 децибел (дБ), тогда как требуемое Eb/No для режима расширения диапазона приблизительно равно 3 дБ. Требуемое отношение энергии символа к общему уровню шума на кратность разнесения (Es/No/div) приблизительно равно -6 дБ при наименьшей скорости передачи данных 250 кбит/с. Желательно достигать обнаружения лучше 90% при этой пороговой величине Es/No/div в диспергирующих канальных условиях.

2. Вхождения в синхронизм по частоте. Приемник стандарта 802.11b/g обычно выполняет дифференциальную демодуляцию. Приемник для режима расширения диапазона может выполнять когерентную демодуляцию для повышения эффективности. Для получения хорошей оценки канала, используемой для когерентной демодуляции, приемнику может потребоваться определить отклонение частоты между генераторами на передающей и приемной станциях. Отклонение частоты ±20 промилле (ppm) на приемной станции интерпретируется в отклонение частоты ±232 кГц на частоте 5,8 ГГц, что может ухудшить эффективность.

3. Оценка канала. Мощность шума в оценке канала должна быть гораздо ниже, чем общая мощность шума, чтобы достигать хорошей эффективности для когерентной демодуляции.

Фиг.4 показывает вариант осуществления процессора 160 приема на приемной станции 150 на фиг.1. В процессоре 160 приема буфер 402 выборок принимает поток входных выборок от каждого из модулей 154a-154r приемника. Процессор 404 вхождения в синхронизм выполняет вхождение в синхронизм для PPDU. В процессоре 404 первый этап обнаружения и блок 410 вхождения в синхронизм по времени принимает входные выборки из буфера 402, обнаруживает PPDU и определяет синхронизацию каждого обнаруженного PPDU. Второй этап обнаружения и блок 420 вхождения в синхронизм по частоте также обнаруживает PPDU и дополнительно оценивает отклонение частоты во входных выборках. Третий этап обнаружения и блок 430 оценки канала также обнаруживает PPDU и дополнительно оценивает отклик радиоканала между передающей станцией 110 и приемной станцией 150. Блоки 410, 420 и 430 могут выполнять обработку на основе 128-битной последовательности в поле SYNC из преамбулы PPDU, как описано далее.

Фиг.5 показывает вариант осуществления первого этапа обнаружения и блока 410 вхождения в синхронизм по времени, который выполняет обнаружение сигнала с использованием корреляции во временной области. Блок 410 производит действия над комплекснозначными входными выборками на частоте выборки, которая больше либо равна скорости передачи элементарного сигнала. Для простоты последующее описание предполагает, что входные выборки предоставляются со скоростью передачи элементарного сигнала. В последующем описании «m» является индексом для приемной антенны, «n» является индексом для периода элементарного сигнала, «k» является индексом для элемента разрешения по частоте и «i» является индексом для 128 битов в фиксированной последовательности, отправленной в поле SYNC. Скорость передачи символов равна скорости передачи битов для пилот-сигнала, отправленного в поле SYNC. Когерентная сумма относится к сумме комплексных величин, а некогерентная сумма относится к сумме действительных величин (например, значений величин).

В блоке 410 корреляторы 510a-510r задержки принимают входные выборки от модулей 154a-154r приемника соответственно. В корреляторе 510a задержки для антенны 1 (или m=1) устройство 512a сужения спектра по Баркеру декодирует с сужением спектра входные выборки с помощью 11-сигнальной последовательности Баркера и предоставляет суженные символы на скорости передачи элементарного сигнала. Для каждого периода n элементарного сигнала устройство 512a сужения спектра по Баркеру умножает 11 входных выборок для периодов элементарного сигнала с n по n-10 на 11 элементарных сигналов из последовательности Баркера, суммирует результаты умножения и предоставляет суженный символ x m(n) для этого периода элементарного сигнала. Устройство 512a сужения спектра по Баркеру выполняет корреляцию с перестраиваемым опорным сигналом последовательности Баркера с входными выборками для получения суженного символа для каждого периода элементарного сигнала (вместо каждого периода символа) и предоставляет суженные символы буферу 514a символов и умножителю 520a задержки.

Умножитель 520a задержки формирует 1-символьные и 2-символьные произведения с задержкой из суженных символов. В умножителе 520a задержки суженные символы предоставляются двум последовательно соединенным блокам 522a и 522b задержки, при этом каждый блок задержки обеспечивает задержку в один период Ts символа, который равен 11 периодам элементарных сигналов, или Ts=11·Tc. Блоки 524a и 524b обеспечивают комплексное сопряжение суженных символов от блоков 522a и 522b задержки соответственно. Умножитель 526a умножает суженный символ для каждого периода n элементарного сигнала на выходной сигнал блока 524a и предоставляет 1-символьное произведение y1,m(n) с задержкой для этого периода элементарного сигнала. Аналогично умножитель 526b умножает суженный символ для каждого периода n элементарного сигнала на выходной сигнал блока 524b и предоставляет 2-символьное произведение y2,m(n) с задержкой для этого периода элементарного сигнала.

Коррелятор задержки для каждой оставшейся антенны обрабатывает входные выборки для этой антенны способом, описанным выше для антенны 1. Каждый коррелятор задержки предоставляет 1-символьные произведения y 1,m(n) с задержкой и 2-символьные произведения y 2,m(n) с задержкой для ассоциированной антенны m. Для каждого периода n элементарного сигнала сумматор 528a когерентно суммирует произведения y 1,m(n) для m=1, …, R от всех R корреляторов 510a-510r задержки и предоставляет произведение y 1(n) для этого периода элементарного сигнала. Для каждого периода n элементарного сигнала сумматор 528b суммирует произведения y 2,m(n) для m=1, …, R от всех корреляторов 510a-510r задержки и предоставляет произведение y 2(n) для этого периода элементарного сигнала. Произведения y 1(n) и y 2(n) могут выражаться в виде:

| , | Ур. (1a) |

| Ур. (1b) |

1-символьное произведение y 1,m(n) с задержкой свидетельствует о разности фаз между двумя суженными символами x m(n) и x m(n-Ts), которые разделены одним периодом символа для антенны m. 2-символьное произведение y 2,m(n) с задержкой свидетельствует о разности фаз между двумя суженными символами x m(n) и x m(n-2Ts), которые разделены двумя периодами символов для антенны m. Фиг.5 показывает использование 1-символьного и 2-символьного произведений с задержкой для обнаружения сигнала. Вообще, для обнаружения сигнала могут использоваться произведения для любого количества различных задержек (например, 1, 2, 3 периода символов и т.д.). Использование произведений для больших задержек может улучшить SNR и эффективность обнаружения. Однако, поскольку уход частоты вызывает чередование фаз во входных выборках, максимальная задержка может быть ограничена уходом частоты. Величина задержки также влияет на сложность дифференциальных корреляторов 530a и 530b. Например, имеются 127 операций умножения и суммирования для задержки в один период символа, 126 операций умножения и суммирования для задержки в два периода символов и т.д.

Дифференциальные корреляторы 530a и 530b принимают произведения y 1(n) и y 2(n) соответственно. В дифференциальном корреляторе 530a произведения y 1(n) предоставляются последовательности чередующихся элементов 532a и 534a задержки. Каждый элемент 532a задержки обеспечивает задержку в один период элементарного сигнала, каждый элемент 534a задержки обеспечивает задержку в 10 периодов элементарного сигнала, каждая пара соседних элементов 532a и 534a задержки обеспечивает задержку в 11 периодов элементарного сигнала (которая равна одному периоду символа), и вся последовательность элементов 532a и 534a задержки обеспечивает задержку примерно в 126 периодов символов. Группа из 127 сумматоров 536a соединяется со 127 элементами 532a задержки. Каждый сумматор 536a суммирует входной сигнал и выходной сигнал ассоциированного элемента 532a задержки и предоставляет выходной сигнал y 1(n-11·i)·y 1(n-11·i-1), где i {0, …, 126}. Группа из 127 умножителей 538a соединяется с группой из 127 сумматоров 536a и также принимает 1-символьную дифференциальную последовательность, содержащую 127 известных значений. Эта последовательность образуется посредством побитового произведения первой последовательности d 0 - d 126 на вторую последовательность d 1-d 127, где d 0-d 127 являются 128 битами фиксированной последовательности (или битами пилот-сигнала), используемой для поля SYNC. Поскольку биты пилот-сигнала являются действительными значениями, для i {0, …, 126}. Каждый умножитель 538a умножает выходной сигнал ассоциированного сумматора 536a на d i d i+1 . Для каждого периода n элементарного сигнала сумматор 540a добавляет выходные сигналы от всех 127 умножителей 538a и предоставляет результат c 1(n) корреляции для этого периода элементарного сигнала.

Дифференциальный коррелятор 530b аналогичен дифференциальному коррелятору 530a. Произведения y 2(n) предоставляются последовательности чередующихся элементов 532b и 534b задержки, которые обеспечивают задержку приблизительно в 125 периодов символов. Группа из 126 сумматоров 536b соединяется со 126 элементами 532b задержки. Каждый сумматор 536b суммирует входной сигнал и выходной сигнал ассоциированного элемента 532b задержки и предоставляет выходной сигнал y 2(n-11·i)·y 2(n-11·i-1), где i {0, …, 125}. Группа из 126 умножителей 538b соединяется с группой из 126 сумматоров 536b и также принимает 2-символьную дифференциальную последовательность, содержащую 126 известных значений. Эта последовательность образуется посредством побитового произведения последовательности d 0-d 125 с последовательностью d 2-d 127. Каждый умножитель 538b умножает выходной сигнал ассоциированного сумматора 536b на d i d i+2 . Для каждого периода n элементарного сигнала сумматор 540b добавляет выходные сигналы от всех 126 умножителей 538b и предоставляет результат c 2(k) корреляции для этого периода элементарного сигнала.

Дифференциальный коррелятор 530a выполняет корреляцию между 1-символьными произведениями y 1(n) с задержкой с 1-символьной дифференциальной последовательностью. Дифференциальный коррелятор 530b выполняет корреляцию между 2-символьными произведениями y 2(n) с задержкой с 2-символьной дифференциальной последовательностью. Показанный на фиг.5 вариант осуществления предполагает, что радиоканал имеет разброс задержек (т.е. рассеяние или загрязнение) из небольшого количества элементарных сигналов. Сумматоры 536a и 536b используются для накопления энергии на этом разбросе задержек. Энергия также может накаливаться на большем количестве элементарных сигналов для большего разброса задержек либо может пропускаться, если радиоканал обладает нулевым или очень маленьким разбросом задержек (например, для строгой траектории радиоволны при распространении в пределах прямой видимости).

Каждый дифференциальный коррелятор 530 предоставляет результат корреляции для каждого периода элементарного сигнала. Фазы результатов c 2(n) корреляции из дифференциального коррелятора 530b могут не совпадать с фазами соответствующих результатов c 1(n) корреляции из дифференциального коррелятора 530a. Умножитель 542 умножает каждый результат c 2(n) корреляции из дифференциального коррелятора 530b на комплексный вектор для L различных предполагаемых фаз и предоставляет множество из L повернутых по фазам результатов корреляции. Например, предполагаемыми фазами могут быть {0, 90°, 180°, -90°} для L=4, {0, 60°, -60°} для L=3 и т.д. L предполагаемых фаз могут выбираться для охвата возможного диапазона относительных фаз. Например, максимальный уход частоты может составлять 232 кГц для отклонения частоты в ±20 ppm и 5,8 ГГц несущей частоты. Максимальная разность фаз между 1-символьными и 2-символьными корреляциями с задержкой равна ±232 кГц умножить на 1 мкс, что приблизительно равно 90 градусам. Отсюда, если используются предполагаемые фазы 0, 60° и -60°, то по меньшей мере одна предполагаемая фаза находится в пределах 30°. Если разность фаз больше (например, вследствие использования большей задержки или большего ухода частоты), то предполагаемые фазы должны охватывать больший диапазон, вплоть до полных ±180°.

Умножитель 542 поворачивает c 2(n) на разные фазы. Для каждого периода n элементарного сигнала сумматор 544 когерентно складывает результат c 1(n) корреляции из сумматора 540a с каждым из L соответствующих повернутых по фазам результатов корреляции из умножителя 542 и предоставляет L объединенных результатов z p(n) корреляции для p=1,…, L. Если используются K дифференциальных корреляторов для K разных задержек, где K>1, то один дифференциальный коррелятор может использоваться в качестве опорного (без фазового сдвига). Тогда один объединенный результат корреляции получается для каждого предположения, соответствующего определенной фазе для каждого из K-1 оставшихся дифференциальных корреляторов. Например, если K=3, то один объединенный результат корреляции получается для каждого предположения, соответствующего другой паре предполагаемых фаз для двух дифференциальных корреляторов. Для LK-1 возможных предположений получаются вплоть до LK-1 объединенных результатов корреляции. Для каждого периода n элементарного сигнала блок 546 вычисляет возведенную в квадрат величину каждого из L объединенных результатов корреляции (для K=2), определяет наибольшее значение величины в квадрате среди L значений величин в квадрате и предоставляет это наибольшее значение Z(n) величины в квадрате. Для каждого периода n элементарного сигнала детектор 548 сигналов сравнивает наибольшее значение Z(n) величины в квадрате с заранее установленной пороговой величиной Zth и объявляет наличие PPDU, если Z(n) превосходит пороговую величину, или Z(n)>Zth. Детектор 548 сигналов продолжает наблюдать за значениями величин в квадрате для поиска максимального значения и предоставляет период элементарного сигнала для этого максимального значения как начальную синхронизацию tau для обнаруженного PPDU.

В качестве альтернативы результаты c 1(n) и c 2(n) корреляции для каждого периода элементарного сигнала могут некогерентно объединяться. Это может достигаться путем вычисления величины c 1(n) в квадрате, вычисления величины c 2(n) в квадрате и суммирования двух возведенных в квадрат величин для получения Z(n). Пороговая величина Zth может устанавливаться в различные значения в зависимости от того, как выводится Z(n).

Пороговая величина Zth, используемая для первого этапа обнаружения, может быть самонастраивающейся пороговой величиной, которая изменяется, например, вместе с принятой энергией Erx для 128-битного поля SYNC. Например, пороговая величина Zth может быть задана равной принятой энергии Erx