Дифференциальный усилитель с повышенным коэффициентом усиления

Иллюстрации

Показать всеИзобретение относится к области радиотехники и связи и может быть использовано в качестве устройства усиления аналоговых сигналов, в структуре аналоговых микросхем различного функционального назначения (например, SiGe-операционных усилителях, компараторах). Технический результат: повышение в 8-10 раз коэффициента усиления по напряжению при использовании сравнительно низкоомного двухполюсника нагрузки (например, R5=1÷2 кОм). Дифференциальный усилитель содержит входной дифференциальный каскад (ДК) (1) с первым (2) и вторым (3) токовыми выходами, первое (4) токовое зеркало (ТЗ), вход которого соединен с первым (2) токовым выходом входного ДК (1), а выход подключен ко второму (3) токовому выходу входного ДК (1), выходной буферный усилитель (5), выход которого связан с низкоомной нагрузкой (6). В схему введены второе ТЗ (7) и третье ТЗ (8) и дополнительный токостабилизирующий двухполюсник (ТД) (9), связанный со входом выходного буферного усилителя (5), базовый вход второго ТЗ (7) соединен со вторым (3) токовым выходом входного ДК (1) и выходом третьего ТЗ (8), вход которого связан с выходом второго ТЗ (7), причем общий эмиттерный выход второго ТЗ (7) соединен со входом выходного буферного усилителя (5). 6 ил.

Реферат

Изобретение относится к области радиотехники и связи и может быть использовано в качестве устройства усиления аналоговых сигналов, в структуре аналоговых микросхем различного функционального назначения (например, SiGe-операционных усилителях (ОУ), компараторах, стабилизаторах напряжения и т.п.).

В современной аналоговой микроэлектронике широко применяются двухкаскадные дифференциальные усилители (ДУ) с активными нагрузками в виде токовых зеркал на биполярных транзисторах, тип проводимости которых противоположен типу проводимости входных транзисторов ДУ (фиг.1) [1-14]. Данная архитектура ДУ относится к числу достаточно широкополосных и весьма часто используется в ВЧ и СВЧ аналоговых устройствах. Однако при низкоомных нагрузках (например, волновых сопротивлениях Rн=50 Ом) такие ДУ имеет невысокие коэффициенты усиления по напряжению (Kу).

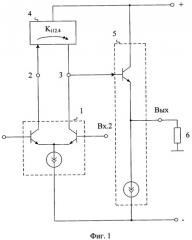

Наиболее близким по технической сущности к заявляемому устройству является ДУ (фиг.1), рассмотренный в патенте США фирмы Sony (Япония) №5.144.169, fig.3. Он содержит входной дифференциальный каскад 1 с первым 2 и вторым 3 токовыми выходами, первое 4 токовое зеркало, вход которого соединен с первым 2 токовым выходом входного дифференциального каскада 1, а выход подключен ко второму 3 токовому выходу входного дифференциального каскада 1, выходной буферный усилитель 5, выход которого связан с низкоомной нагрузкой 6.

Существенный недостаток известного ДУ состоит в том, что при реализации нагрузки в виде низкоомного резистора (например, 50 Ом) его коэффициент усиления получается небольшим.

Основная задача предполагаемого изобретения состоит в повышении на один-два порядка коэффициента усиления по напряжению ДУ при использовании сравнительно низкоомных двухполюсников нагрузки (например, Rн=50 Ом).

Поставленная задача достигается тем, что в дифференциальном усилителе фиг.1, содержащем входной дифференциальный каскад 1 с первым 2 и вторым 3 токовыми выходами, первое 4 токовое зеркало, вход которого соединен с первым 2 токовым выходом входного дифференциального каскада 1, а выход подключен ко второму 3 токовому выходу входного дифференциального каскада 1, выходной буферный усилитель 5, выход которого связан с низкоомной нагрузкой 6, предусмотрены новые элементы и связи - в схему введены второе 7 и третье 8 токовые зеркала и дополнительный токостабилизирующий двухполюсник 9, связанный со входом выходного буферного усилителя 5, базовый вход второго 7 токового зеркала соединен со вторым 3 токовым выходом входного дифференциального каскада 1 и выходом третьего 8 токового зеркала, вход которого связан с выходом второго 7 токового зеркала, причем общий эмиттерный выход второго 7 токового зеркала соединен со входом выходного буферного усилителя 5.

На фиг.1 приведена схема ДУ-прототипа.

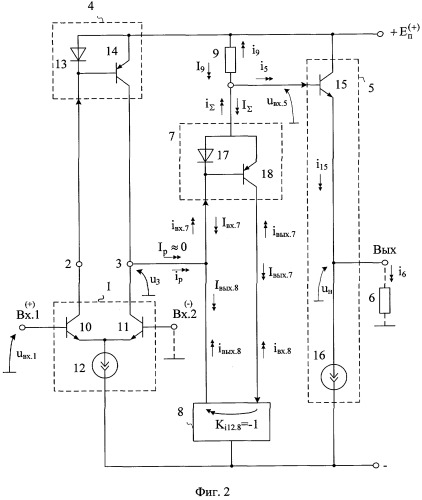

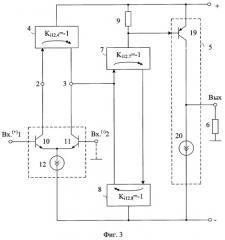

Схема заявляемого устройства, соответствующего формуле изобретения, представлена на фиг.2, а на фиг.3 - его архитектура для случая, когда выходной буферный усилитель реализован на транзисторе с общим эмиттером.

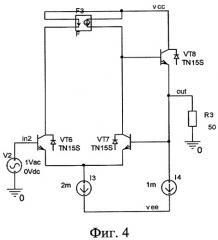

На фиг.4-5 показаны схема ДУ-прототипа (фиг.4) и схема заявляемого ДУ (фиг.5) в среде компьютерного моделирования Pspice на моделях интегральных транзисторов ФГУП НПП «Пульсар», а на фиг.6 - зависимость коэффициента усиления по напряжению сравниваемых схем (фиг.4, 5) от частоты. Данные графики показывают, что несмотря на применение низкоомной нагрузки (Rн=50 Ом в схеме фиг.5) коэффициент усиления по напряжению улучшается на 40,0 Дб (в 100 раз) в сравнении с Kу известного устройства. Это важное достоинство предлагаемого ДУ.

Дифференциальный усилитель с повышенным коэффициентом усиления фиг.2 содержит входной дифференциальный каскад 1 с первым 2 и вторым 3 токовыми выходами, первое 4 токовое зеркало, вход которого соединен с первым 2 токовым выходом входного дифференциального каскада 1, а выход подключен ко второму 3 токовому выходу входного дифференциального каскада 1, выходной буферный усилитель 5, выход которого связан с низкоомной нагрузкой 6. В схему введены второе 7 и третье 8 токовые зеркала и дополнительный токостабилизирующий двухполюсник 9, связанный со входом выходного буферного усилителя 5, базовый вход второго 7 токового зеркала соединен со вторым 3 токовым выходом входного дифференциального каскада 1 и выходом третьего 8 токового зеркала, вход которого связан с выходом второго 7 токового зеркала, причем общий эмиттерный выход второго 7 токового зеркала соединен со входом выходного буферного усилителя 5.

В частном случае (фиг.2) входной дифференциальный каскад 1 реализован на базе транзисторов 10, 11 и двухполюснике 12, токовое зеркало 4 - транзисторах 13 и 14, буферный усилитель - транзисторе 15 и двухполюснике 16, токовое зеркало 7 - диоде 17 и транзисторе 18.

На фиг.5 представлен ДУ фиг.2, в котором выходной буферный усилитель 5 реализован на транзисторе 19 и двухполюснике 20.

Рассмотрим работу ДУ фиг.2.

Статический режим транзисторов 10 и 11 ДУ фиг.2 устанавливается двухполюсником 12. При введении общей отрицательной обратной связи в ДУ фиг.2 статический ток через его двухполюсник 9:

где R9 - сопротивление двухполюсника 9;

Uэб.15%≈0,7 В - напряжение эмиттер-база транзистора 15;

I0 - статический ток токовых зеркал 7 и 8.

Если на вход Bx.(+)1 подается положительное напряжение uвх.1, то это вызывает увеличение напряжения в узле 3 (u3), а также напряжения на входе буферного усилителя 5 (uвх.5) и, как следствие, напряжения на нагрузке 6 (u6=uн), причем

Поэтому ток в нагрузке 6 увеличивается, что приводит к изменению входного тока i5 буферного усилителя 5:

где Ki5 - коэффициент усиления по току буферного усилителя 5.

Как следствие, суммарный переменный ток iΣ общей эмиттерной цепи второго 7 токового зеркала

Если положить, что коэффициенты передачи второго 7 и третьего 8 токовых зеркал близки к единице, то разностный ток ip, «нагружающий» входной дифференциальный каскад 1, будет близок к нулю:

Или после преобразований:

Таким образом, эквивалентное сопротивление нагрузки выходной подсхемы ДУ фиг.2:

Учитывая, что Ki7≈1, Ki8≈1, находим, что в заявляемой схеме сопротивление нагрузки R6=Rн не влияет на коэффициент усиления по напряжению Kу

где rэ10=rэ11 - сопротивления эмиттерных переходов транзисторов 10 и 11 входного дифференциального каскада 1.

Это позволяет получить более высокие значения Kу при малых Rн=10÷50 Ом.

Таким образом, заявляемое устройство имеет существенные преимущества в сравнении с прототипом.

Источники информации

1. Патент США №4.042.886.

2. Патент Японии JP 10032437.

3. Патент Японии JP 2005033558.

4. Патент США №4.595.883, fig.4.

5. Патентная заявка США №2005/0063270 А1, fig.2.

6. Патент США №5.166.638, fig.1.

7. Патент США №5.537.081, fig.3.

8. Патент США №6.114.904.

9. Патент США №5.144.169 fig.3.

10. Патент США №4.223.276.

11. Патент США №5.365.191, fig.9.

12. Патент США №5.144.259.

13. Патент США №6.870.426, fig.5.

14. Патент США№5.148.121, fig.1.

Дифференциальный усилитель с повышенным коэффициентом усиления, содержащий входной дифференциальный каскад (1) с первым (2) и вторым (3) токовыми выходами, первое (4) токовое зеркало, вход которого соединен с первым (2) токовым выходом входного дифференциального каскада (1), а выход подключен ко второму (3) токовому выходу входного дифференциального каскада (1), выходной буферный усилитель (5), выход которого связан с низкоомной нагрузкой (6), отличающийся тем, что в схему введены второе (7) и третье (8) токовые зеркала и дополнительный токостабилизирующий двухполюсник (9), связанный со входом выходного буферного усилителя (5), базовый вход второго (7) токового зеркала соединен со вторым (3) токовым выходом входного дифференциального каскада (1) и выходом третьего (8) токового зеркала, вход которого связан с выходом второго (7) токового зеркала, причем общий эмиттерный выход второго (7) токового зеркала соединен со входом выходного буферного усилителя (5).