Каскодный усилитель с парафазным выходом

Иллюстрации

Показать всеИзобретение относится к области радиотехники и связи для усиления аналоговых сигналов, в структуре аналоговых микросхем различного функционального назначения (например, СВЧ-усилителях, смесителях сигналов и т.п.). Технический результат: получение двух выходных противофазных напряжений uвых.1 и uвых.2, пропорциональных входному напряжению ивх. Каскодный усилитель содержит первый (1) и второй (2) входные транзисторы, эмиттеры которых подключены к шине источника питания (3), источник входного сигнала (4), связанный с базой первого (1) входного транзистора, первый (5) и второй (6) выходные транзисторы с объеденными базами, коллекторы которых соединены с первой (7) и второй (8) цепями нагрузки, а эмиттеры подключены к коллекторам соответствующих первого (1) и второго (2) входных транзисторов. В схему введены первый (9) и второй (10) дополнительные транзисторы, базы которых подключены к базам соответствующих первого (1) и второго (2) входных транзисторов, эмиттеры связаны с шиной источника питания (3), коллекторы объединены и через согласующий двухполюсник (11) связаны с объединенными базами первого (5) и второго (6) выходных транзисторов, которые подключены к дополнительному источнику опорного тока (12), причем эмиттер первого (5) выходного транзистора связан с базой второго (2) входного транзистора, а эмиттер второго (6) выходного транзистора связан с базой первого (1) входного транзистора. 1 з.п. ф-лы, 8 ил.

Реферат

Изобретение относится к области радиотехники и связи и может быть использовано в качестве устройства усиления аналоговых сигналов, в структуре аналоговых микросхем различного функционального назначения (например, СВЧ-усилителях, смесителях и перемножителях сигналов и т.п.).

Широкое применение СВЧ дифференциальных сигналов в современной микроэлектронике позволяет снизить влияние синфазных помех, нелинейных искажений четного порядка, повысить качество обработки сигналов при низких значениях напряжения питания. Применение дифференциальных сигналов часто сопровождается необходимостью преобразования их в однофазный сигнал и обратно, так как большинство периферийных устройств могут работать лишь с однофазными сигналами. Для выполнения таких преобразований служат специальные симметрирующие устройства - так называемые балуны (balanced to unbalanced). Балуны наиболее часто применяются при построении усилителей мощности, смесителей и аналоговых перемножителей. Заявляемое устройство может быть отнесено к данному классу усилительных каскадов, которые применяются не только в качестве фазорасщепителей сигналов, но и для их усиления.

Известны схемы каскодных усилителей (КУ) с парафазным выходом, в которых эмиттеры входных транзисторов подключены к общей шине источника питания [1-12]. Однако они не обеспечивают преобразование однофазного сигнала в два противофазных и в этом смысле являются псевдодифференциальными усилителями, требующими два противофазных входных напряжения uвх.1 и .

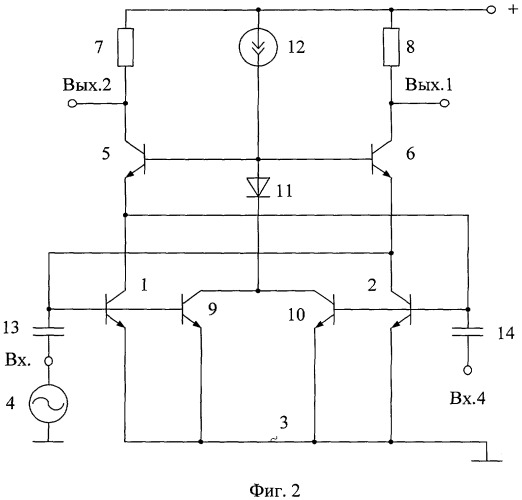

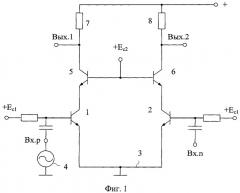

Ближайшим прототипом заявляемого устройства является каскодный усилитель, описанный в патентной заявке США 2005/0174175 (фиг.1), содержащий первый 1 и второй 2 входные транзисторы, эмиттеры которых подключены к шине источника питания 3, источник входного сигнала 4, связанный с базой первого 1 входного транзистора, первый 5 и второй 6 выходные транзисторы с объеденными базами, коллекторы которых соединены с первой 7 и второй 8 цепями нагрузки, а эмиттеры подключены к коллекторам соответствующих первого 1 и второго 2 входных транзисторов.

Существенный недостаток известного устройства состоит в том, что оно не обеспечивает преобразование однофазного входного сигнала uвх в два противофазных и uвых.2, т.е. не является классическим дифференциальным усилителем, для которого напряжения на каждом из выходов пропорциональны uвх, но имеют разные фазы (отличающиеся на 180°).

Основная задача предлагаемого изобретения состоит в получении двух выходных противофазных напряжений и uвых.2, пропорциональных входному напряжению uвх.

Поставленная задача достигается тем, что в каскодном усилителе (фиг.1), содержащем первый 1 и второй 2 входные транзисторы, эмиттеры которых подключены к шине источника питания 3, источник входного сигнала 4, связанный с базой первого 1 входного транзистора, первый 5 и второй 6 выходные транзисторы с объеденными базами, коллекторы которых соединены с первой 7 и второй 8 цепями нагрузки, а эмиттеры подключены к коллекторам соответствующих первого 1 и второго 2 входных транзисторов, предусмотрены новые элементы и связи - в схему введены первый 9 и второй 10 дополнительные транзисторы, базы которых подключены к базам соответствующих первого 1 и второго 2 входных транзисторов, эмиттеры связаны с шиной источника питания 3, коллекторы объединены и через согласующий двухполюсник 11 связаны с объединенными базами первого 5 и второго 6 выходных транзисторов, которые подключены к дополнительному источнику опорного тока 12, причем эмиттер первого 5 выходного транзистора связан с базой второго 2 входного транзистора, а эмиттер второго 6 выходного транзистора связан с базой первого 1 входного транзистора.

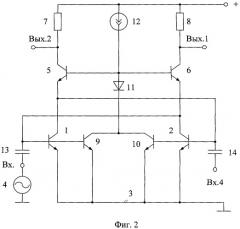

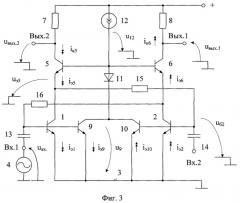

Схема заявляемого устройства, соответствующего п.1 формулы изобретения, показана на фиг.2, а пункту 2 - на фиг.3.

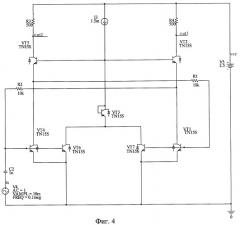

На фиг.4 показана схема заявляемого КУ (фиг.3) в среде компьютерного моделирования PSpice на моделях интегральных транзисторов ФГУП НПП «Пульсар», а на фиг.5 - зависимость фазового сдвига по каждому каналу и коэффициента усиления от частоты. При этом на фазо-частотных характеристиках принято, что φ1=φ2+180°.

На фиг.6 представлена схема заявляемого КУ (фиг.3) в среде компьютерного моделирования Cadence на моделях интегральных транзисторов IHP, а на фиг.7 - зависимости коэффициентов усиления для каждого из выходов от частоты и фазо-частотные характеристики (фиг.8) по каждому каналу.

Каскодный усилитель с парафазным выходом (фиг.2) содержит первый 1 и второй 2 входные транзисторы, эмиттеры которых подключены к шине источника питания 3, источник входного сигнала 4, связанный с базой первого 1 входного транзистора, первый 5 и второй 6 выходные транзисторы с объеденными базами, коллекторы которых соединены с первой 7 и второй 8 цепями нагрузки, а эмиттеры подключены к коллекторам соответствующих первого 1 и второго 2 входных транзисторов. В схему введены первый 9 и второй 10 дополнительные транзисторы, базы которых подключены к базам соответствующих первого 1 и второго 2 входных транзисторов, эмиттеры связаны с шиной источника питания 3, коллекторы объединены и через согласующий двухполюсник 11 связаны с объединенными базами первого 5 и второго 6 выходных транзисторов, которые подключены к дополнительному источнику опорного тока 12, причем эмиттер первого 5 выходного транзистора связан с базой второго 2 входного транзистора, а эмиттер второго 6 выходного транзистора связан с базой первого 1 входного транзистора. Источник входного сигнала 4 соединен с базой входного транзистора через первый 13 разделительный конденсатор. Аналогично второй источник питания сигнала может подключаться к схеме через второй 14 разделительный конденсатор.

В схеме фиг.3, в соответствии с п.2 формулы изобретения, эмиттер первого 5 выходного транзистора связан с базой второго 2 входного транзистора через первый 15 дополнительный резистор, а эмиттер второго 6 выходного транзистора связан с базой первого 1 входного транзистора через второй 16 дополнительный резистор.

Рассмотрим работу ДУ заявляемого устройства.

Статический режим транзисторов схем фиг.2 и фиг.3 устанавливается дополнительным источником опорного тока 12 (I12). При этом коллекторные токи

При подаче на левый вход ДУ фиг.3 положительной полуволны входного сигнала uвх увеличиваются эмиттерные токи транзисторов 1, 9, 5:

где rэi - сопротивление эмиттерных переходов транзисторов 1 и 9.

Как следствие, уменьшается напряжение u12≈u9≈uэ5 на дополнительном источнике опорного тока 12, которое передается в эмиттер транзистора 5 и далее через первый дополнительный резистор 15 на базу транзисторов 2 и 10:

Напряжение uб2 запирает транзисторы 10 и 2 так, что приращения их эмиттерных токов одинаковы, но противофазны: iэ9+iэ10=0, т.е. в схеме фиг.3:

Таким образом, в схеме фиг.3 токи коллекторов транзисторов 5 и 6 также противофазны, но равны друг другу iк5≈iэ1, iк6≈iэ2. Следовательно, противофазны и выходные напряжения uвых.1 и uвых2.

Данные теоретические выводы соответствуют результатам компьютерного моделирования схем фиг.4 и фиг.6, представленных графиками фиг.5, фиг.7, фиг.8.

Таким образом, заявляемое устройство выполняет функции СВЧ-усилителя, обеспечивающего преобразование однофазного сигнала в два противофазных до частот 20-25 ГГц и может быть реализовано по внедряемой в России технологии SGB25VD.

ЛИТЕРАТУРА

1. Патентная заявка США № 2005/0174175 fig.2 - прототип.

2. Патент ЕР № 1.480.333.

3. Патент WO № 03/084054.

4. Патент США № 6.682.223.

5. Патент США № 6.615.547.

6. Патентная заявка США № 2006/0049874.

7. Патентная заявка США № 2006/0071712 A.

8. Патент США № 5.990.741 fig.3.

9. Патентная заявка США № 2005/134387.

10. Патент США № 7.088.185.

11. Патентная заявка США № 2007/0290754 fig.1.

12. Патентная заявка США № 2008/0309411 fig.1.

1. Каскодный усилитель с парафазным выходом, содержащий первый (1) и второй (2) входные транзисторы, эмиттеры которых подключены к шине источника питания (3), источник входного сигнала (4), связанный с базой первого (1) входного транзистора, первый (5) и второй (6) выходные транзисторы с объеденными базами, коллекторы которых соединены с первой (7) и второй (8) цепями нагрузки, а эмиттеры подключены к коллекторам соответствующих первого (1) и второго (2) входных транзисторов, отличающийся тем, что в схему введены первый (9) и второй (10) дополнительные транзисторы, базы которых подключены к базам соответствующих первого (1) и второго (2) входных транзисторов, эмиттеры связаны с шиной источника питания (3), коллекторы объединены и через согласующий двухполюсник (11) связаны с объединенными базами первого (5) и второго (6) выходных транзисторов, которые подключены к дополнительному источнику опорного тока (12), причем эмиттер первого (5) выходного транзистора связан с базой второго (2) входного транзистора, а эмиттер второго (6) выходного транзистора связан с базой первого (1) входного транзистора.

2. Устройство по п.1, отличающееся тем, что эмиттер первого (5) выходного транзистора связан с базой второго (2) входного транзистора, через первый (15) дополнительный резистор, а эмиттер второго (6) выходного транзистора связан с базой первого (1) входного транзистора через второй (16) дополнительный резистор.