Широкополосный дифференциальный усилитель

Иллюстрации

Показать всеИзобретение относится к области радиотехники и связи для усиления аналоговых сигналов в структуре аналоговых микросхем различного функционального назначения (например, СВЧ-усилителях, сумматоров двух сигналов, логарифмирующих каскадов и т.п.). Технический результат: создание простого сверхширокополосного аналогового преобразователя дифференциальных сигналов в недифференциальный сигнал, обеспечение стабильных единичных значений коэффициентов усиления по напряжению Ку1=-1, Ку2=-1 относительно иизкоомного выхода широкополосного дифференциального усилителя (ШДУ) и при высокой стабильности нуля ШДУ в диапазоне температур и радиационных воздействий. ШДУ содержит входной дифференциальный каскад (ДК) (1) с первым (2) и вторым (3) токовыми выходами, связанными с эмиттерами соответствующих первого (4) и второго (5) вспомогательных транзисторов (Т), а также базами первого (6) и второго (7) выходных Т, первый (8) токостабилизирующий двухполюсник (ТД), включенный между шиной первого (9) источника питания (ИП) и объединенными базами первого Т(4) и второго Т (5), второй ТД (10), включенный между эмиттером второго Т (7) и шиной второго (11) ИП. Коллектор первого Т (6) соединен с базами первого Т (4) и второго Т (5), его эмиттер связан с общей шиной (12) первого (9) и второго (11) ИП, а коллекторы первого Т (4), второго Т (5), а также коллектор второго Т (7) связаны с шиной первого (9) ИП, причем выход ШДУ связан с эмиттером второго Т (7). 1 з.п. ф-лы, 10 ил.

Реферат

Изобретение относится к области радиотехники и связи и может быть использовано в качестве устройства усиления аналоговых сигналов, в структуре аналоговых микросхем различного функционального назначения (например, СВЧ-усилителях, сумматоров двух сигналов, логарифмирующих каскадов и т.п.),

В совремемнной микроэлектронике при построении систем на кристалле возникает необходимость применения широкополосных дифференциальных усилителей (ШДУ) с единичным коэффициентом усиления по напряжению |Ky|=1. При этом такие ШДУ должны быть как инвертирующими, так и неинвертирующими фазу входного сигнала, а их коэффициент усиления должен быть достаточно стабильным в широком диапазоне температур и напряжений источников питания. Предлагаемое изобретение относится к данному классу усилительных устройств.

Известны схемы широкополосных двухкаскадных дифференциальных усилителей (ДУ) на основе логарифмирующих p-n-переходов - так называемые ячейки Джильберта [1-18].

Наиболее близким но технической сущности к заявляемому устройству является широкополосный дифференциальный усилитель фиг.1, рассмотренный в патенте США № 5.521.544. Эта же схема присутствует в патентах |2-18|. Однако данные структуры ШДУ не обеспечивают преобразование симметричного дифференциального входного сигнала к несимметричному иизкоомному выходу, имеющему в статическом режиме нулевой потенциал, т.е. выходу, согласованному с общей шиной источников питания. Это затрудняет последовательное каскадирование таких ШДУ, их практическое использование в разных устройствах связи, автоматики и вычислительной техники, а также согласование по выходу с другими функциональными узлами РЭА.

Основная задача предлагаемого изобретения состоит в создании простого сверхширокополосного аналогового преобразователя дифференциальных сигналов в недифференциальный сигнал, обеспечении стабильных единичных значений коэффициентов усиления по напряжению Ky1=-1, Ky2=-1 относительно низкоомного выхода ШДУ при высокой стабильности нуля ШДУ в диапазоне температур и радиационных воздействий.

Устройство с такими характеристиками может послужить основой для построения различных функциональных узлов систем на кристалле и IP-модулей - логарифматоров, перемножителей напряжения, фильтров, простейших СВЧ операционных усилителей, стабилизаторов напряжения и т.п.

Поставленная задача достигается тем, что в широкополосном дифференциальном усилителе фиг.1, содержащем входной дифференциальный каскад 1 с первым 2 и вторым 3 токовыми выходами, связанными с эмиттерами соответствующих первого 4 и второго 5 вспомогательных транзисторов, а также базами первого 6 и второго 7 выходных транзисторов, первый 8 токостабилизирующий двухполюсник, включенный между шиной первого 9 источника питания и объединенными базами первого 4 и второго 5 вспомогательных транзисторов, второй токостабилизирующий двухполюсник 10, включенный между эмиттером второго 7 выходного транзистора и шиной второго 11 источника питания, предусмотрены новые элементы и связи - коллектор первого 6 выходного транзистора соединен с базами первого 4 и второго 5 вспомогательных транзисторов, его эмиттер связан с общей шиной 12 первого 9 и второго 11 источников питания, а коллекторы первого 4, второго 5 вспомогательных транзисторов, а также коллектор второго 7 выходного транзистора связаны с шиной первого 9 источника питания, причем выход широкополосного дифференциального усилителя связан с эмиттером второго 7 выходного транзистора.

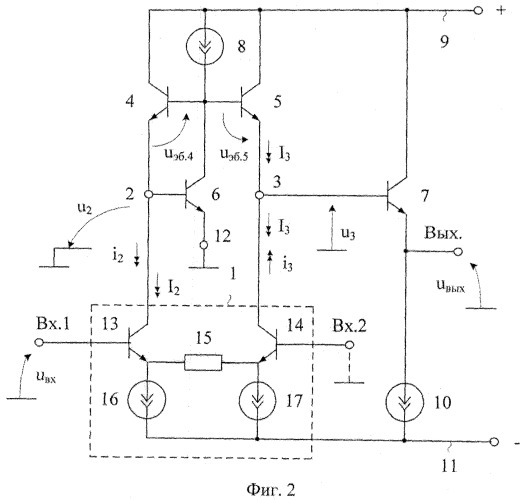

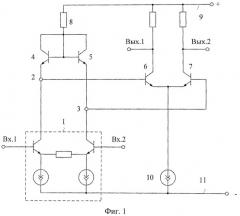

На фиг.1 представлена схема ШДУ-прототипа.

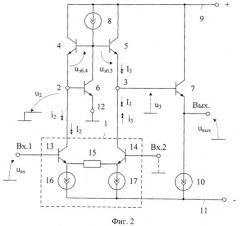

На фиг.2 представлена схема заявляемого ШДУ в соответствии с п.1 формулы изобретения.

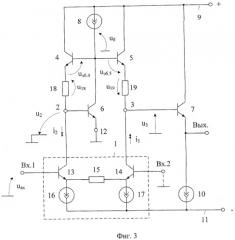

На фиг.3 приведена схема ШДУ, соответствующая п.2 формулы изобретения.

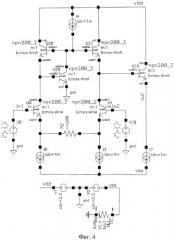

На фиг.4 показана схема фиг, 2 в среде компьютерного моделирования Cadence на моделях интегральных транзисторов IНР, а на чертеже фиг.5 - зависимость выходного напряжения ШДУ от входного напряжения при разных значениях сопротивлений резистора R15=R0. Анализ графика фиг.5 показывает, что при R15=R0=0 заявляемый ШДУ обеспечивает линейное усиление сигнала с амплитудой до 200-250 мВ.

На фиг.6 приведены амплитудно-частотные характеристики ШДУ фиг.4 при подаче сигнала на входы in2 и in1, т.е. в инвертирующем и неинвертирующем включении. Анализ данных графиков показывает, что заявляемый ШДУ обеспечивает единичное усиление сигналов до частоты 35-38 ГГц. При этом сигнал со входа 1 инвертируется по фазе, а со входа 2 - не инвертируется.

График фиг.7 показывает фазовые соотношения входного и выходного напряжений для инвертирующего включения ШДУ фиг.4. Из его рассмотрения следует, что ШДУ фиг.4 обеспечивает инверсию входного сигнала на 180° при единичном коэффициенте усиления.

Фиг.8 иллюстрирует зависимость напряжения смещения нуля ШДУ фиг.3 от температуры. Из данного графика следует, что напряжение смещения нуля в диапазоне температур от -50°C до 75°C изменяется на 0,2 мкВ. т.е. отличается достаточно высокой стабильностью.

На фиг.9 показана схема фиг.3 в среде компьютерного моделирования Cadence на моделях интегральных транзисторов IHP, а на фиг.10 - ее амплитудно-частотные характеристики при разных значениях сопротивлений резистора R15=R0. Из данных графиков следует, что предлагаемый ШДУ обеспечивает усиление около 20 дБ до частоты 17 ГГц.

Широкополосный дифференциальный усилитель фиг.2 содержит входной дифференциальный каскад 1 с первым 2 и вторым 3 токовыми выходами, связанными с эмиттерами соответствующих первого 4 и второго 5 вспомогательных транзисторов, а также базами первого 6 и второго 7 выходных транзисторов, первый 8 токостабилизирующий двухполюсник, включенный между шиной первого 9 источника питания и объединенными базами первого 4 и второго 5 вспомогательных транзисторов, второй токостабилизирующий двухполюсник 10, включенный между эмиттером второго 7 выходного транзистора и шиной второго 11 источника питания. Коллектор первого 6 выходного транзистора соединен с базами первого 4 и второго 5 вспомогательных транзисторов, его эмиттер связан с общей шиной 12 первого 9 и второго 11 источников питания, а коллекторы первого 4, второго 5 вспомогательных транзисторов, а также коллектор второго 7 выходного транзистора связаны с шиной первого 9 источника питания, причем выход широкополосного дифференциального усилителя связан с эмиттером второго 7 выходного транзистора. В частном случае входной дифференциальный каскад 1 реализован на транзисторах 13, 14 и двухполюсниках 15, 16 и 17.

На фиг.3, в соответствии с п.2 формулы изобретения, первый 2 и второй 3 токовые выходы входного дифференциального каскада 1 связаны с эмиттерами соответствующих первого 4 и второю 5 выходных транзисторов через соответствующие первый 18 и второй 19 дополнительные резисторы.

Рассмотрим работу схемы фиг.2.

В статическом режиме при пулевом uвх=0 в узлах 2 и 3 протекают одинаковые токи I2 и I3. Выходное напряжение ШДУ определяется напряжениями на эмиттерно-базовых переходах транзисторов 7, 5, 4, 6:

где

Uxx - напряжение на эмиттерно-базовом p-n-переходе i-го транзистора при эмиттерном токе Iэi=Ixx.

Учитывая, что все транзисторы идентичны, а также то, что эмиттерные токи транзисторов 6 и 7 одинаковы и не изменяются при изменении uвх, из уравнения (1) находим

Для входного дифференциального каскада 1

где R15 - сопротивление двухполюсника 15.

Таким образом, в широком диапазоне изменения uвх, выходное напряжение ШДУ фиг.2

где Uгр≈I0R15+2φт.

Функция (5) может быть представлена в виде ряда Тейлора:

Таким образом, при небольших (uвх<200 мВ) выходное напряжение ШДУ фиг.2 пропорционально входному напряжению uвх. Если R15=0, то uвых=uвх, то есть ШДУ обеспечивает неинвертирующее единичное усиление.

Если входное напряжение подается на второй вход Вх.2, то ШДУ фиг.2 инвертирует фазу сигнала в широком диапазоне частот: uвых=-uвх.

Данные выводы подтверждаются графиками фиг.6.

Для схемы фиг.3 коэффициент усиления по напряжению зависит от сопротивления дополнительных резисторов 18 и 19:

где rэ13=rэ14 - сопротивления эмиттерных переходов транзисторов 13 и 14.

Таким образом, в схеме фиг.3 обеспечивается преобразование входного дифференциального сигнала в выходной недифференциальный сигнал, формирующийся на низкоомном выходе. Это важное свойство схемы фиг.3, которое существенно расширяет области ее практического использования. Действительно, широкое применение СВЧ дифференциальных сигналов в современной микроэлектронике позволяет снизить влияние синфазных помех, нелинейных искажений четного порядка, повысить качество обработки сигналов при низких значениях напряжения питания. Применение дифференциальных сигналов всегда сопровождается необходимостью преобразования их в однофазный сигнал и обратно, так как большинство периферийных устройств могут работать лишь с однофазными сигналами. Заявляемое устройство выполняет эти функции.

БИБЛИОГРАФИЧЕСКИЙ СПИСОК

1. Патент США № 5.521.544, fig.6.

2. Патент США № 6.111,463, fig.1.

3. Патент США № 4.572.975, fig.1.

4. Патент США № 5.550.512, fig.3.

5. Патент США № 5.115.409, fig.1.

6. Патент США № 4.439.696, fig.2.

7. Патент США № 5.883.539, fig.2.

8. Патент США № 4.288.707.

9. Патент США № 5.774.020, fig.1.

10. Патент США № 5.677.646.

11. Патент США № 5.039.952, fig.5.

12. Патент США № 5.734.294, fig.4.

13. Патент США № 5.886.916, fig.1.

14. Патент США № 6.369.618, fig.2.

15. Патентная заявка США № 2002/0053935, fig.4.

16. Патентная заявка США № 2004/0251965, fig.5.

17. Патентная заявка США № 2004/0032298, fig.1.

18. Патент WO 2002/071597.

1. Широкополосный дифференциальный усилитель, содержащий входной дифференциальный каскад (1) с первым (2) и вторым (3) токовыми выходами, связанными с эмиттерами соответствующих первого (4) и второго (5) вспомогательных транзисторов, а также базами первого (6) и второго (7) выходных транзисторов, первый (8) токостабилизирующий двухполюсник, включенный между шиной первого (9) источника питания и объединенными базами первого (4) и второго (5) вспомогательных транзисторов, второй токостабилизирующий двухполюсник (10), включенный между эмиттером второго (7) выходного транзистора и шиной второго (11) источника питания, отличающийся тем, что коллектор первого (6) выходного транзистора соединен с базами первого (4) и второго (5) вспомогательных транзисторов, его эмиттер связан с общей шиной (12) первого (9) и второго (11) источников питания, а коллекторы первого (4), второго (5) вспомогательных транзисторов, а также коллектор второго (7) выходного транзистора связаны с шиной первого (9) источника питания, причем выход широкополосного дифференциального усилителя связан с эмиттером второго (7) выходного транзистора.

2. Широкополосный дифференциальный усилитель по п.1, отличающийся тем, что первый (2) и второй (3) токовые выходы входного дифференциального каскада (1) связаны с эмиттерами соответствующих первого (4) и второго (5) выходных транзисторов через соответствующие первый (18) и второй (19) дополнительные резисторы.