Счетчик импульсов

Иллюстрации

Показать всеИзобретение относится к области цифровой вычислительной техники и автоматики. Техническим результатом является повышение быстродействия за счет сокращения максимального времени распространения сигнала переноса и расширение перечня выполняемых элементарных операций (ЭО) при минимальных затратах оборудования. Счетчик импульсов содержит в каждом разряде один RS-триггер, девять элементов И, четыре элемента ИЛИ, четыре элемента НЕ, вход счетных импульсов, информационный вход, шесть входов управления для выполнения ЭО. 1 ил.

Реферат

Изобретение относится к области цифровой вычислительной техники и автоматики. Известны счетчики импульсов, построенные на основе триггеров со счетным входом (см. И.Н.Букреев, Б.М.Мансуров и В.И.Горячев. Микроэлектронные схемы цифровых устройств. 1973, Сов. радио, стр.136-146, Л1). Основным недостатком счетчиков, выполненных на основе триггеров со счетным входом, является наличие в составе оборудования счетного триггера (СТ), специальных элементов временной задержки счетных импульсов, что снижает быстродействие его работы, усложняет технологию изготовления и повышает требование к параметрам счетных импульсов (крутизна фронта, длительность и другие параметры). Известен также счетчик, выполненный на основе только трех логических элементов (ЛЭ) И, ИЛИ, НЕ, который устраняет недостатки приведенного выше устройства (см. Л1. Стр. 143, рис. 5.7). В каждом разряде счетчик содержит два RS-триггера (основной и вспомогательный) и ЛЭ И, НЕ. Недостатком этого счетчика является наличие двух RS-триггеров в разряде и выполнение только одной элементарной операции счета импульсов. Наиболее близким, принятым за прототип, является счетчик импульсов (далее - объект), выполненный по патенту RU 2284654 С2, каждый разряд которого построен на основе одного RS-триггера, семи элементов И, четырех элементов ИЛИ, пяти элементов НЕ, семи входов управления, информационного входа и выполняет восемь элементарных операций (ЭО); счет, вычитание импульсов, инвертирования кода, прием кода в RS-триггер, сдвиг кода влево и вправо, логическое сложение и логическое умножение кодов, хранящихся в RS-триггерах объекта и поступающих по информационным входам. Однако прототип не выполняет ЭО сложение по модулю два (сравнение) и имеет временную задержку сигнала в цепи сквозного переноса, равную 2τn (τ - временная задержка сигнала на одном элементе И (ИЛИ), n - число разрядов объекта), что следует считать недостатком прототипа.

Предлагаемый объект устраняет отмеченные недостатки. Целью изобретения является повышение быстродействия за счет сокращения максимального времени распространения сигнала переноса и расширение перечня выполняемых ЭО при минимальных затратах оборудования. Для достижения поставленной цели предложен объект, выполненный на логических элементах И, ИЛИ, НЕ и RS-триггерах, отличающийся тем, что содержит в каждом двоичном разряде девять элементов И, четыре элемента ИЛИ, четыре элемента НЕ, один RS-триггер, информационный вход, шесть входов управления и вход счетных импульсов, при этом информационный вход соединен с первым входом первого элемента И, второй вход которого соединен с первым входом управления приемом кода, поступающего по информационному входу, выход первого элемента И через первый и второй элементы ИЛИ соединен с первыми входами шестого и седьмого элементов И, т.е. со счетным входом RS-триггера, вторые входы упомянутых элементов И подключены к входу и выходу второго элемента НЕ, вход которого также соединен с выходом восьмого элемента И, выходы шестого и седьмого элементов И через третий и четвертый элементы НЕ подключены к нулевому и единичному входам RS-триггера, выход шестого элемента И подключен к первому входу четвертого элемента ИЛИ, второй вход этого элемента соединен с единичным выходом RS-триггера, а его выход связан с первым входом восьмого элемента И, второй вход упомянутого элемента И подключен к выходу четвертого элемента НЕ, выход восьмого элемента И соединен с первыми входами девятого и второго элементов И i-го разряда и с входом второго элемента И i+1-го разряда, выход второго элемента НЕ соединен с первым входом третьих элементов И i-го и i+1-го разрядов, выходы второго и третьего элементов И через третий элемент ИЛИ соединены с входом первого элемента НЕ, выход которого соединен с первыми входами четвертых и пятых элементов И i-го и i-1-го разрядов соответственно, вторые входы пятых элементов И всех разрядов связаны с третьим входом управления сдвигом кода триггеров вправо на один разряд за каждый временной такт, вторые входы четвертых элементов И всех разрядов связаны с четвертым входом управления сдвигом кода триггеров влево на один разряд за каждый временной такт, выходы четвертого и пятого элементов И соединены с входами второго элемента ИЛИ; второй вход первого элемента ИЛИ подключен к второму входу управления инвертированием RS-триггера, вход счетных импульсов в первом разряде счетчика подключен к второму входу девятого элемента И и к третьему входу первого элемента ИЛИ, в третьем и четвертом разрядах вход счетных импульсов соединен со вторыми входами девятых элементов И, выход девятого элемента И первого разряда соединен со вторым входом девятого элемента И и третьим входом первого ИЛИ второго разряда, выход девятого элемента И второго разряда соединен с третьим входом первого элемента ИЛИ третьего разряда, третий вход девятого элемента И третьего разряда соединен с третьим входом девятого элемента И четвертого разряда и с выходом второго элемента И второго разряда, выход девятого элемента И третьего разряда соединен с третьим входом первого элемента ИЛИ четвертого разряда, первые входы девятых элементов И второго и третьего разрядов соединены с выходами восьмых элементов И соответственно, первый вход девятого элемента И четвертого разряда подключен к выходу второго элемента И этого же разряда, выход девятого элемента И четвертого разряда является входом счетных импульсов в старшую группу из четырех разрядов и соединен с вторыми входами девятых элементов И пятого, седьмого и восьмого разрядов и с третьим входом первого элемента ИЛИ пятого разряда соответственно, пятый вход управления выполнением операции логического умножения подключен к третьим входам четвертых элементов ИЛИ всех разрядов, шестой вход управления выполнением операции логического сложения подключен к третьим входам восьмых элементов И всех разрядов. Предлагаемый объект обеспечивает сокращение суммарного времени задержки сигнала переноса во всех разрядах с 2nτ у прототипа до nτ/4, т.е. в восемь раза меньше. Это достигается за счет нового построения цепи формирования переноса. В предложенном объекте вход счетных импульсов подключен к третьему входу первого элемента ИЛИ первого разряда группы и к вторым входам девятых элементов И первого, третьего и четвертого разрядов; третьи входы упомянутых элементов И третьего и четвертого разрядов связаны с выходом второго элемента И второго разряда, третий вход девятого элемента И четвертого разряда подключен к выходу второго И этого же разряда, первые входы девятых элементов И первого-третьего разрядов соединены с выходами восьмых элементов И соответственно. При этом оборудование цепи сквозного переноса группы из четырех разрядов увеличивается только на два входа, а время задержки сигнала в упомянутых разрядах сократится в 8 раз (2nτ - для прототипа; nτ/4 - для объекта). Объект позволяет выполнить дополнительно пять ЭО: сложение по модулю два, параллельный прием прямого и обратного кода с информационных входов, прием кода единиц в триггеры всех разрядов, установку в нуль триггеров всех разрядов.

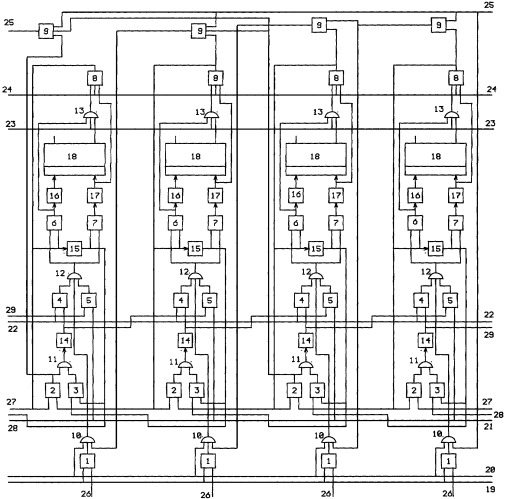

Для пояснения работы предлагаемого объекта на чертеже приведена функциональная схема его четырех двоичных разрядов. На схеме приняты следующие обозначения: элементы И 1-9, элементы ИЛИ 10-13, элементы НЕ 14-17, RS-триггер (Tr) 18, первый вход управления (ВУ) приемом кода с информационного входа (ИВ) 19, второй ВУ инвертированием Tr 18-20, третий ВУ сдвигом кода вправо 21, четвертый ВУ сдвигом кода влево 22, пятый ВУ выполнением операции логического умножения 23, шестой ВУ выполнением операции логического сложения 24, вход счетных импульсов (ВСИ) 25, информационный вход 26, потенциалы управления инвертированием старшего разряда при сдвиге кода влево 27, 28, потенциал управления инвертированием младшего разряда при сдвиге кода вправо 29.

Предложенный объект осуществляется следующим образом. В каждом разряде объекта первые входы И 1 подключены к ИВ 26, вторые входы которого связаны с ВУ 19, выход И 1 через ИЛИ 10, 12 соединен с входами И 6, 7. Вход управления инвертированием RS-триггера 20 соединен со вторым входом ИЛИ 10, третий вход ИЛИ 10 первого разряда подключен к ВСИ 25 и к входам И 9 первого, третьего и четвертого разрядов группы из четырех двоичных разрядов. Вторые входы И 6, 7 соединены с входом и выходом НЕ 15. Выходы упомянутых элементов И через НЕ 16, 17 соединены с нулевым и единичным входом Tr 18. Выход И 6 связан с входом ИЛИ 13, второй его вход соединен с единичным выходом триггера 18, третий вход подключен к ВУ 23. Выход ИЛИ 13 соединен с первым входом И 8, второй и третий входы которого соединены с выходом НЕ 17 и ВУ 24 соответственно. Выход И 8 первого-третьего разрядов группы подключены к первым входам И 9, И 2 i-го разряда и к входам И 2 старших разрядов соответственно. Выходы И 8 первого-четвертого разрядов также соединены с вторыми входами И 6 и входами НЕ 15. Выход И 2 через ИЛИ 11, НЕ 14 соединен с первым входом И 4, второй вход которого связан с ВУ 22. Выход НЕ 14 также соединен с И 5 младшего разряда, второй вход которого соединен с ВУ 21. Выходы И 4, 5 подключены к входам ИЛИ 12. Выход И 2 второго разряда соединен с третьими входами И 9 третьего и четвертого разрядов. Выход И 2 четвертого разряда соединен с первым входом И 9 четвертого разряда группы. Выход И 9 упомянутого разряда является входом счетных импульсов для старшей группы из четырех разрядов. Для выполнения операции циклического сдвига кода вправо и влево выход 29 младшего разряда соединяется с первым входом И 5 самого старшего разряда, выходы 27 и 28 самого старшего разряда объекта соединяются с первым входами И 2, 3 первого разряда. Входы управления 23 и 24 подключены к третьим входам ИЛИ 13 и И 8 соответственно.

Рассмотрим работу объекта при выполнении всего перечня выполняемых операций. В исходном положении (в статике) триггеры объекта установлены в «нуль». На ВУ 19-23, на ИВ 26 и на выходах НЕ 14 отсутствуют высокие потенциалы. На выходах элементов НЕ 15-17 и на ВУ 24 присутствуют высокие (разрешающие) потенциалы.

1. Операция счета импульсов. Операция счета каждого импульса выполняется за два временных такта ВТ 1 и ВТ 2. По ВТ1 на вход 25 поступает первый счетный импульс (СИ). Счетный импульс в первом разряде по цепи вход 25, ИЛИ 10, 12, поступает на входы И 6, 7. Т.к. на первом входе И 7 присутствует высокий потенциал, поступающий с выхода НЕ 15, то СИ через И 7, НЕ 17 поступает на единичный вход Tr 18, устанавливает его в единицу и запрещает работу И 8 на время, равное длительности СИ. После окончания действия СИ высокие потенциалы с единичного выхода Тr 18 и НЕ 17 выработают высокий потенциал на выходе И 8, который поступит на входы И 6, НЕ 15 первого разряда и разрешит следующему СИ поступить на нулевой вход Tr 18 и установить его в «нуль». При этом высокий потенциал с И 8 поступает на вход И 9 первого разряда. (Заметим, что во время СИ, если в триггерах всех разрядов объекта хранится код единицы, может распространяться потенциал сигнала переноса (ПСП) из четвертого разряда до последнего разряда счетчика. Это время в предлагаемом объекте равно nτ/4. В прототипе задержка ПСП равна 2nτ, т.е. в восемь раз больше.) Второй СИ по цепи вход 25, ИЛИ 10, 12, И 6, НЕ 16 поступит на нулевой вход Тr 18 первого разряда и установит его в нуль. Импульс с выхода И 6 через ИЛИ 13 будет «поддерживать» высокий потенциал с выходом И 8 до прекращения СИ. Одновременно импульс с выхода И 9 первого разряда по цепи ИЛИ 10, 12, И 7, НЕ 17 поступит на единичный вход Tr 18 второго разряда, установит его в единицу и будет запрещать работу И 8 этого разряда на время длительности СИ. Третий СИ установит Tr 18 первого разряда в единицу. По истечении времени, равного длительности паузы между СИ, на вход И 9 первого разряда поступит четвертый СИ. Теперь на входах и выходах И 9 первого и второго разрядов будут присутствовать высокие потенциалы, которые обеспечат условия установки в единицу Тr 18 третьего разряда, а Tr 18 первого и второго разрядов в нуль. При этом условия распространения потенциала переноса не будут меняться, т.к. импульсы с выходов И 8 первого и второго разрядов через ИЛИ 13 будут «поддерживать» условия выработки переноса в этих разрядах. После седьмого СИ Tr 18 первого-третьего разрядов будут установлены в единицу. С выхода И 2 второго разряда на третий вход И 9 третьего и четвертого разряда будет поступать высокий потенциал. Восьмой СИ установит Tr 18 первого-третьего разрядов в нуль, а Tr 18 четвертого разряда - в единицу. После пятнадцатого СИ все Tr 18 первого-четвертого разрядов будут хранить код единицы. С выходов И 2 второго и четвертого разрядов на первый и третий входы И 9 поступят высокие потенциалы. Шестнадцатый СИ установит Tr 18 первого-четвертого разрядов в нуль. С выхода И 9 четвертого разряда будет вырабатываться сигнал переноса, т.е. сигнал счетного импульса в старшую группу из четырех разрядов. Отметим, что рассмотренная операция (базовая операция) осуществляется только на основе одного RS-триггера в каждом разряде, а временная задержка сигнала переноса четырех разрядов определяется одним элементом И 9 четвертого разряда. Это обеспечивает повышение быстродействия работы объекта при минимальных затратах оборудования для построения цепи сквозного переноса.

2. ЭО инвертирования кода. Положим, в двух разрядах счетчика хранится код «10». Исполнительный импульс операции инвертирования подается на ВУ 20 и по цепи ИЛИ 10, 12 поступит на входы И 6, 7. В первом разряде Tr 18 хранит код нуля, т.е. на первом входе И 7 будет высокий потенциал. Исполнительный импульс по цепи ВУ 20, ИЛИ 10, 12, И 7, НЕ 17 поступит на единичный вход Tr 18 вход и установит его в единицу. Во втором разряде в Tr 18 хранится код единицы, т.е. на выходе И 8 будет высокий потенциал, разрешающий прохождение импульса с ВУ 20 по цепи ИЛИ 10, 12, И 6, НЕ 16 на нулевой вход Tr 18 и установку его в нуль. Таким образом, в триггерах первого и второго разрядов будет храниться код «01», т.е. инверсный код. Для выполнения этой операции требуется увеличить оборудование каждого разряда только на один вход элемента ИЛИ 10.

3. Операция вычитание импульсов. Операция выполняется аналогично операции сложения. Отличие состоит в том, что до начала и после ее выполнения необходимо выполнить операцию инвертирования кодов, хранящихся в Tr 18. Операция не требует дополнительного оборудования.

4. ЭО сдвига кода влево (в сторону старших разрядов). Сдвиг кода на один разряд влево выполняется за два временных такта. Тактами являются импульс сдвига и пауза между импульсами. Максимальное время выполнения операции 2nτ. Полагаем, что Ти=Тп. Допустим, в исходном положении второй разряд счетчика хранит код единицы. Во всех остальных разрядах Tr 18 хранят код нуля. Во втором разряде на входах И 2, 3 нет совпадения высоких потенциалов, т.е. . С выхода НЕ 14 на вход И 4 поступает высокий потенциал. Признаком выполнения операции сдвига кодов влево является исполнительный импульс, поступивший на ВУ 22. В втором разряде, в котором хранится код единицы, потенциал с И 8 поступает на вход И 6. Исполнительный импульс сдвига, поступивший по ВУ 22 и далее по цепи элементов И 4, ИЛИ 12 И 6, НЕ 16, поступает на нулевой вход триггера 18 и устанавливает его в нуль. Одновременно этот же импульс по цепи И 6 ИЛИ 13 будет "поддерживать" высокий потенциал на первом входе И 8. В третьем разряде также нет совпадения высоких потенциалов на входах И 2, 3. На выходе НЕ 14 - высокий потенциал. Исполнительный импульс проходит на единичный вход Tr 18 и устанавливает его в единицу. Таким образом, код единицы будет сдвинут на один разряд влево. Операция будет выполняться до тех пор, пока на ВУ 22 будут поступать импульсы сдвига. При этом, если выход И 8 самого старшего разряда будет соединен с входом ИЗ самого младшего разряда, то будет выполняться циклический сдвиг кода. Это позволяет использовать объект как распределитель n-канальных импульсов.

5. Эо сдвига кода вправо. Операция выполняется аналогично выполнению операции сдвига влево. Отличие состоит в том, что исполнительный импульс (ИИ) поступает на ВУ 21. Если коды i-го и i-i-го разрядов не равны друг другу, то Tr 18 младшего разряда инвертируются.

6. ЭО логического сложения. Выполняется за два временных такта. Для выполнения этой операции с ВУ 24 снимается высокий потенциал, а на ВУ 19 поступает ИИ, разрешающий прием кода с информационного входа 26. На выходе НЕ 15 появляется высокой потенциал, разрешающий прохождение импульса на единичный вход Tr 18. Если по информационному входу 26 на И 1 поступил потенциал, соответствующий единице второго слагаемого i-того разряда, то ИИ по цепи элементов И 1, ИЛИ 10, 12, И 7, НЕ 17 поступит на единичный вход Tr 18 и установит его в единицу. Если на ВУ 26 отсутствует высокий потенциал, то Tr 18 не изменит свое состояние. На этом операция логического сложения завершается. Второй временной такт используется для подготовки объекта к выполнению последующей операции. Для выполнения операции требуется дополнительно только один вход И 8.

7. ЭО логического умножения. Выполняется за два временных такта. На время выполнения операции на ВУ 23 подается высокий потенциал, разрешающий прохождение ИИ на нулевой вход Tr 18. На ВУ 19 поступает высокий потенциал разрешения приема с ИВ 26. Для выполнения этой операции на ИВ 26 поступает инверсное значение кода i-го разряда. При наличии высокого потенциала на ИВ 26, соответствующего нулю второго сомножителя i-го разряда, высокий потенциал по цепи ВУ 26, И 1, ИЛИ 10, 12, И 6, НЕ 16 поступает на нулевой вход Tr 18 и устанавливает его в нуль. На этом операция логического умножения завершается. Второй временной такт отводится для подготовки объекта к выполнению последующей операции.

8. ЭО приема кода. Устройство позволяет выполнить три модификации приема кода: прием прямого кода с информационного входа с предварительной установкой Tr 18 в нуль; прием кода единиц во все разряды одновременно и прием инверсного кода с информационного входа с предварительной установкой всех триггеров в единицу. Первая модификация приема кода выполняется при поступлении на ИВ 26 высокого потенциала, соответствующего коду единицы. При этом сигнал проходит по цепи элементов И 1, ИЛИ 10, 12, И 7, НЕ 7, поступает на единичный вход Tr 18 и устанавливает его в единицу. Прием всех единиц в триггеры 18 (вторая модификация) выполняется за счет снятия высокого потенциала с ВУ 24 и поступления исполнительного импульса на ВУ 20. Третья модификация приема кода в триггеры с информационных входов выполняется за четыре временных такта. По первому такту все Tr 18 устанавливаются в единицу, второй такт используется для подготовки объекта к выполнению последующих операций, по третьему такту выполняют прием кода с информационного входа по счетному входу Tr 18. При этом на ВУ 19 поступает ИИ приема кода. Если на ИВ 26 имеет место высокий потенциал, то ИИ проходит по цепи элементов И 1, ИЛИ 10, 12, И 6, 7, т.е. на счетный вход Tr 18, и инвертирует его. Таким образом, Tr 18 будет хранить инверсное значение кода, поступившего по информационному входу.

9. ЭО сложения по модулю два. Выполняется за два временных такта и заключается в приеме кода с ИВ 26 по счетному входу Tr 18.

10. ЭО установки нуля всех триггеров. Для выполнения этой ЭО на ВУ 23 и ВУ 20 поступают управляющий потенциал и ИИ. Исполнительный импульс по цепи элементов ИЛИ 10, 12, И 6, НЕ 16 поступает на нулевой вход Tr 18 всех разрядов и установит их в нуль. Для выполнения этой ЭО не требуется дополнительного оборудования.

Таким образом, предлагаемый счетчик импульсов обеспечивает повышение быстродействия выполнения операций счета импульсов за счет сокращения суммарного времени задержек сигнала переноса по сравнению с прототипом в восемь раз и расширяет перечень выполняемых операций при минимальных затратах оборудования.

Счетчик импульсов, выполненный на логических элементах И, ИЛИ, НЕ и RS-триггерах, отличающийся тем, что содержит в каждом двоичном разряде девять элементов И, четыре элемента ИЛИ, четыре элемента НЕ, один RS-триггер, информационный вход, шесть входов управления и вход счетных импульсов, при этом информационный вход соединен с первым входом первого элемента И, второй вход которого соединен с первым входом управления приемом кода, поступающего по информационному входу, выход первого элемента И через первый и второй элементы ИЛИ соединен с первыми входами шестого и седьмого элементов И, т.е. со счетным входом RS-триггера, вторые входы упомянутых элементов И подключены к входу и выходу второго элемента НЕ, вход которого также соединен с выходом восьмого элемента И, выходы шестого и седьмого элементов И через третий и четвертый элементы НЕ подключены к нулевому и единичному входам RS-триггера, выход шестого элемента И подключен к первому входу четвертого элемента ИЛИ, второй вход этого элемента соединен с единичным выходом RS-триггера, а его выход связан с первым входом восьмого элемента И, второй вход упомянутого элемента И подключен к выходу четвертого элемента НЕ, выход восьмого элемента И соединен с первыми входами девятого и второго элементов И i-го разряда и с входом второго элемента И i+1-го разряда, выход второго элемента НЕ соединен с первым входом третьих элементов И i-го и i+1-го разрядов, выходы второго и третьего элементов И через третий элемент ИЛИ соединены с входом первого элемента НЕ, выход которого соединен с первыми входами четвертых и пятых элементов И i-го и i-1-го разрядов соответственно, вторые входы пятых элементов И всех разрядов связаны с третьим входом управления сдвигом кода триггеров вправо на один разряд за каждый временной такт, вторые входы четвертых элементов И всех разрядов связаны с четвертым входом управления сдвигом кода триггеров влево на один разряд за каждый временной такт, выходы четвертого и пятого элементов И соединены с входами второго элемента ИЛИ; второй вход первого элемента ИЛИ подключен к второму входу управления инвертированием RS-триггера, вход счетных импульсов в первом разряде счетчика подключен к второму входу девятого элемента И и к третьему входу первого элемента ИЛИ, в третьем и четвертом разрядах вход счетных импульсов соединен с вторыми входами девятых элементов И, выход девятого элемента И первого разряда соединен с вторым входом девятого элемента И и третьим входом первого ИЛИ второго разряда, выход девятого элемента И второго разряда соединен с третьим входом первого элемента ИЛИ третьего разряда, третий вход девятого элемента И третьего разряда соединен с третьим входом девятого элемента И четвертого разряда и с выходом второго элемента И второго разряда, выход девятого элемента И третьего разряда соединен с третьим входом первого элемента ИЛИ четвертого разряда, первые входы девятых элементов И второго и третьего разрядов соединены с выходами восьмых элементов И соответственно, первый вход девятого элемента И четвертого разряда подключен к выходу второго элемента И этого же разряда, выход девятого элемента И четвертого разряда является входом счетных импульсов в старшую группу из четырех разрядов, и соединен с вторыми входами девятых элементов И пятого, седьмого и восьмого разрядом и с третьим входом первого элемента ИЛИ пятого разряда соответственно, пятый вход управления выполнением операции логического умножения подключен к третьим входам четвертых элементов ИЛИ всех разрядов, шестой вход управления выполнением операции логического сложения подключен к третьим входам восьмых элементов И всех разрядов.