Дифференциальный усилитель с повышенным коэффициентом усиления по напряжению

Иллюстрации

Показать всеИзобретение относится к области радиотехники и связи и может быть использовано в качестве устройства усиления аналоговых сигналов, в структуре аналоговых микросхем различного функционального назначения (например, SiGe-операционных усилителях, компараторах). Технический результат: повышение на 1-2 порядка коэффициента усиления по напряжению при использовании сравнительно низкоомных двухполюсников нагрузки (например, 50 Ом). Дифференциальный усилитель содержит входной дифференциальный каскад (ДК) (1) с первым (2) и вторым (3) токовыми выходами, первый (4) токостабилизирующий двухполюсник (ТД), связанный с первым (2) токовым выходом входного ДК (1) и базой первого (5) выходного транзистора (Т), эмиттер которого соединен со вторым ТД (6) и первой (7) цепью нагрузки, третий ТД (8), связанный со вторым (3) токовым выходом входного ДК (1) и базой второго (9) выходного Т, эмиттер которого соединен с четвертым ТД (10) и второй (11) цепью нагрузки. В схему введено дополнительное токовое зеркало (12), базовый вход которого соединен с первым (2) токовым выходом входного ДК (1), выход подключен ко второму (3) токовому выходу входного ДК (1) и базе дополнительного Т (13), а общий эмиттерный выход соединен с эмиттером дополнительного Т (13) и дополнительным ТД (14). 1 з.п. ф-лы, 6 ил.

Реферат

Изобретение относится к области радиотехники и связи и может быть использовано в качестве устройства усиления аналоговых сигналов, в структуре аналоговых микросхем различного функционального назначения (например, SiGe - операционных усилителях (ОУ), компараторах).

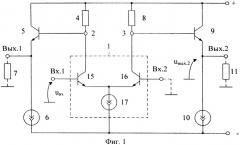

В современной микроэлектронике широко применяются простейшие двухкаскадные дифференциальные усилители (ДУ) (фиг.1), которые используются в качестве элементов эмиттерно-связанной логики, драйверов линий связи, элементарных операционных усилителей и фильтров. Коэффициент усиления по напряжению таких ДУ (Ку) зависит от сопротивлений токостабилизирующих двухполюсников в коллекторной цепи входных транзисторов, а также сопротивлений цепей нагрузки Rн.

При использовании SiGe технологических процессов напряжение питания ДУ не должно превышать ±2 В, что накладывает существенные ограничения на способы реализации двухполюсников 4 и 8. Так, при их реализации на полевых транзисторах (ПТ) эквивалентные сопротивления этих двухполюсников r4 (r8) получаются небольшими в связи с работой ПТ в «триодной» области выходных характеристик. Это ограничивает коэффициент усиления Ку на уровне 10÷40. Действительно, для схемы ДУ фиг.1

где

r8 - эквивалентное сопротивление двухполюсника 8;

β9 - коэффициент усиления по току базы транзистора 9;

R11=Rн - сопротивление цепи нагрузки 11.

Если использовать в качестве двухполюсников r8 (r3) резисторы, то при малом напряжении питания ()

где φт=26 мВ - температурный потенциал;

UR - статическое падение напряжения на резисторе 8.

В большинстве случаев этого недостаточно.

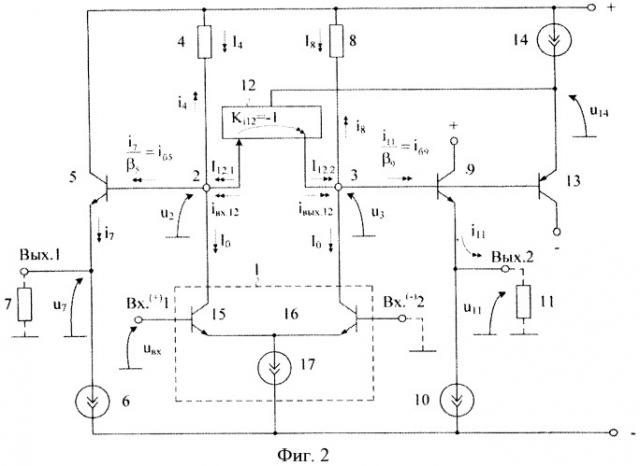

Наиболее близким по технической сущности к заявляемому устройству является ДУ (фиг.1), рассмотренный в патенте США №4365207, fig.2, фирмы Hitachi. Он содержит входной дифференциальный каскад 1 с первым 2 и вторым 3 токовыми выходами, первый 4 токостабилизирующий двухполюсник, связанный с первым 2 токовым выходом входного дифференциального каскада 1 и базой первого 5 выходного транзистора, эмиттер которого соединен со вторым 6 токостабилизирующим двухполюсником и первой 7 цепью нагрузки, третий 8 токостабилизирующий двухполюсник, связанный со вторым 3 токовым выходом входного дифференциального каскада 1 и базой второго 9 выходного транзистора, эмиттер которого соединен с четвертым 10 токостабилизирующим двухполюсником и второй 11 цепью нагрузки.

Существенный недостаток известного ДУ состоит в том, что при реализации его цепей нагрузки в виде низкоомного резистора (например, 50,0 Ом) его коэффициент усиления по напряжению получается небольшим (10÷20).

Основная задача предлагаемого изобретения состоит в повышении на один - два порядка коэффициента усиления по напряжению при использовании сравнительно низкоомных цепей нагрузки (например, R11=50 Ом).

Поставленная задача достигается тем, что в дифференциальном усилителе (фиг.1), содержащем входной дифференциальный каскад 1 с первым 2 и вторым 3 токовыми выходами, первый 4 токостабилизирующий двухполюсник, связанный с первым 2 токовым выходом входного дифференциального каскада 1 и базой первого 5 выходного транзистора, эмиттер которого соединен со вторым 6 токостабилизирующим двухполюсником и первой 7 цепью нагрузки, третий 8 токостабилизирующий двухполюсник, связанный со вторым 3 токовым выходом входного дифференциального каскада 1 и базой второго 9 выходного транзистора, эмиттер которого соединен с четвертым 10 токостабилизирующим двухполюсником и второй 11 цепью нагрузки, предусмотрены новые элементы и связи - в схему введено дополнительное токовое зеркало 12, базовый вход которого соединен с первым 2 токовым выходом входного дифференциального каскада 1, выход подключен ко второму 3 токовому выходу входного дифференциального каскада 1 и базе дополнительного транзистора 13, а общий эмиттерный выход соединен с эмиттером дополнительного транзистора 13 и дополнительным токостабилизирующим двухполюсником 14.

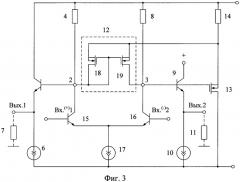

Схема заявляемого устройства, соответствующего п.1 и 2 формулы изобретения, показана на фиг.2 и 3. Причем на чертеже фиг.3 токовое зеркало 12 выполнено на полевых транзисторах.

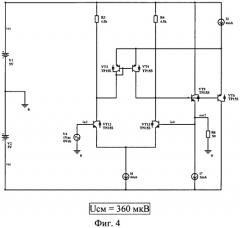

На фиг.4 и фиг.5 показаны схема ДУ фиг.2 без двухполюсника нагрузки 7 и схема заявляемого ДУ (фиг.5) в среде компьютерного моделирования PSpice на моделях интегральных транзисторов ФГУП НПП «Пульсар», а на чертеже фиг.6 - частотная зависимость коэффициентов усиления по напряжению сравниваемых схем (фиг.4 и фиг.5). Данные графики показывают, что, несмотря на применение низкоомных двухполюсников нагрузки (RH=R7=R11=50 Ом), коэффициент усиления по напряжению предлагаемого ДУ (фиг.5) улучшается на два порядка в сравнении с Ку ДУ (фиг.4). Это важное достоинство предлагаемого ДУ при его реализации в рамках технологического процесса SGB25H2.

Дифференциальный усилитель с повышенным коэффициентом усиления по напряжению (фиг.2) содержит входной дифференциальный каскад 1 с первым 2 и вторым 3 токовыми выходами, первый 4 токостабилизирующий двухполюсник, связанный с первым 2 токовым выходом входного дифференциального каскада 1 и базой первого 5 выходного транзистора, эмиттер которого соединен со вторым 6 токостабилизирующим двухполюсником и первой 7 цепью нагрузки, третий 8 токостабилизирующий двухполюсник, связанный со вторым 3 токовым выходом входного дифференциального каскада 1 и базой второго 9 выходного транзистора, эмиттер которого соединен с четвертым 10 токостабилизирующим двухполюсником и второй 11 цепью нагрузки. В схему введено дополнительное токовое зеркало 12, базовый вход которого соединен с первым 2 токовым выходом входного дифференциального каскада 1, выход подключен ко второму 3 токовому выходу входного дифференциального каскада 1 и базе дополнительного транзистора 13, а общий эмиттерный выход соединен с эмиттером дополнительного транзистора 13 и дополнительным токостабилизирующим двухполюсником 14.

На фиг.2 входной дифференциальный каскад 1 реализован на основе транзисторов 15, 16 и двухполюснике 17. Токовое зеркало 12 в схеме фиг.3 выполнено на полевых транзисторах 18 и 19.

На фиг.2 и фиг.3 в соответствии с п.2 формулы изобретения сопротивления первого 4 и третьего 8 токостабилизирующих двухполюсников, а также первой 7 и второй 11 цепей нагрузки удовлетворяют условию

r4||β5R7≈r8||β9R11,

где β5, β9 - коэффициенты усиления по току базы первого 5 и второго 9 выходных транзисторов.

Рассмотрим работу предлагаемого устройства фиг.2.

Если на вход Вх.1 подается положительное напряжение uвх, то это вызывает увеличение напряжения u3 в узле 3 и, следовательно, напряжения на выходе ДУ Вых.2 и также напряжений u14, u2 и u7

Поэтому входной (iвх.12) и выходной (iвых.12) токи токового зеркала 12

где Кi12=1 - коэффициент передачи по току токового зеркала 12;

r4, R7 - сопротивления двухполюсника 4 и цепи нагрузки 7.

Разностный ток ip, определяющий эквивалентное сопротивление в узле 3 (rэкв.3)

После преобразований последней формулы находим, что эквивалентное сопротивление в узле 3

Если схема ДУ симметрична (r8=r4, β9=β5, R7=R11), то эквивалентное сопротивление в узле 3 увеличивается: rэкв.3→∞. Как следствие, существенно растет коэффициент усиления по напряжению ДУ

За счет введения новых связей ДУ (фиг.2) имеет более чем на два порядка больший коэффициент усиления по напряжению в сравнении со схемами фиг.1 и фиг.4.

Замечательная особенность заявляемого ДУ - малое напряжение смещения нуля (Uсм=3,4 мкВ, фиг.5).

Коэффициент усиления по напряжению заявляемого ДУ (фиг.2) повышается также за счет повышения крутизны усиления входного дифференциального каскада 1. В схеме фиг.2 статическое напряжение на двухполюсниках 4, 8, а также статические токи других элементов схемы связаны соотношениями:

где I12.1=I12.2 - входной и выходной статические токи токового зеркала 12.

Это позволяет выбрать эмиттерные токи транзисторов 15 и 16 на более высоком уровне, чем в схеме фиг.1 (не уменьшая сопротивлений резисторов 4 и 8). В итоге уменьшается знаменатель формулы для Ку (9), так как

В ДУ-прототипе (фиг.1) увеличение эмиттерных токов входных транзисторов 15 и 16 невозможно без уменьшения сопротивлений резисторов 4 и 8. Как следствие, Ку схемы (фиг.1) остается малым.

Таким образом, предлагаемое устройство имеет существенные преимущества по сравнению с прототипом.

Источники информации

1. Патент США №4536717, fig.1.

2. Патент США №4691174, fig.1.

3. Патент США №4714896, fig.3.

4. Патент США №4354161, fig.4.

5. Патент США №4365207, fig.1.

6. Патент США №3783307, fig.1.

7. Патент Японии JP 51-112253.

8. Патент СА 02072436, fig.2.

9. Патент США №5262688.

10. Патент Японии 54-102949, кл. 98/5 А21.

11. Патент США №4847519, fig.2.

12. Патент США №4689579.

13. Патент США №6396346.

14. Патентная заявка США 2006/0012432, fig.4A.

15. Патент США №4468628.

1. Дифференциальный усилитель с повышенным коэффициентом усиления по напряжению, содержащий входной дифференциальный каскад (1) с первым (2) и вторым (3) токовыми выходами, первый (4) токостабилизирующий двухполюсник, связанный с первым (2) токовым выходом входного дифференциального каскада (1) и базой первого (5) выходного транзистора, эмиттер которого соединен со вторым (6) токостабилизирующим двухполюсником и первой (7) цепью нагрузки, третий (8) токостабилизирующий двухполюсник, связанный со вторым (3) токовым выходом входного дифференциального каскада (1) и базой второго (9) выходного транзистора, эмиттер которого соединен с четвертым (10) токостабилизирующим двухполюсником и второй (11) цепью нагрузки, отличающийся тем, что в схему введено дополнительное токовое зеркало (12), базовый вход которого соединен с первым (2) токовым выходом входного дифференциального каскада (1), выход подключен ко второму (3) токовому выходу входного дифференциального каскада (1) и базе дополнительного транзистора (13), а общий эмиттерный выход соединен с эмиттером дополнительного транзистора (13) и дополнительным токостабилизирующим двухполюсником (14).

2. Дифференциальный усилитель с повышенным коэффициентом усиления по напряжению по п.1, отличающийся тем, что сопротивления первого (4) и третьего (8) токостабилизирующих двухполюсников, а также первой (7) и второй (11) цепей нагрузки удовлетворяют условиюr4||β5R7≈r8||β9R11,где β5, β9 - коэффициенты усиления по току базы первого (5) и второго (9) выходных транзисторов.