Усилитель переменного тока с парафазным выходом

Иллюстрации

Показать всеИзобретение относится к области радиотехники и связи и может быть использовано в качестве устройства усиления аналоговых сигналов, в структуре аналоговых микросхем различного функционального назначения (например, СВЧ-усилителях, фазорасщепителях сигналов и т.п.). Технический результат: повышение эффективности использования напряжения питания. Конкретно это выражается в получении более высокого Kу при одинаковом с прототипом напряжении питания и использовании в качестве двухполюсников нагрузки резисторов. Усилитель переменного тока с парафазным выходом содержит первый (1) и второй (2) входные транзисторы с объединенными эмиттерами, первый (3) и второй (4) двухполюсники цепи нагрузки, включенные между первой шиной (5) источника питания и соответствующими коллекторами первого (1) и второго (2) входных транзисторов, источник сигнала (6), связанный но переменному току с базой первого входного транзистора (1), вторую шину (7) источника питания. В схему введены первый (8) и второй (9) дополнительные транзисторы, эмиттеры которых объединены с эмиттерами первого (1) и второго (2) входных транзисторов и подключены ко второй шине (7) источника питания, база первого дополнительного транзистора (8) соединена с базой первого входного транзистора (1), база второго дополнительного транзистора (9) подключена к базе второго входного транзистора (2), коллекторы первого (8) и второго (9) дополнительных транзисторов объединены и через дополнительный двухполюсник (10) связаны с первой шиной (5) источника питания, причем объединенные коллекторы первого (8) и второго (9) дополнительных транзисторов связаны соответствующими базами первого (1) и второго (2) входных транзисторов через соответствующие первый (11) и второй (12) дополнительные неинвертирующие усилители. 3 з.п. ф-лы, 6 ил.

Реферат

Изобретение относится к области радиотехники и связи и может быть использовано в качестве устройства усиления аналоговых сигналов, в структуре аналоговых микросхем различного функционального назначения (например, СВЧ-усилителях, фазорасщипетелях сигналов и т.п.).

Широкое применение СВЧ дифференциальных сигналов в современной микроэлектронике позволяет снизить влияние синфазных помех, нелинейных искажений четного порядка, повысить качество обработки сигналов при низких значениях напряжения питания. Применение дифференциальных сигналов часто сопровождается необходимостью преобразования их в однофазный сигнал и обратно, так как большинство периферийных устройств могут работать лишь с однофазными сигналами. Для выполнения таких преобразований служат специальные симметрирующие устройства, так называемые «балуны» (balanced to unbalanced). Балуны наиболее часто применяются при построении усилителей мощности, смесителей и аналоговых перемножителей. Заявляемое устройство может быть отнесено к данному классу усилительных каскадов, которые применяются не только в качестве фазорасщепителей сигналов, но и для их усиления.

В настоящее время в ВЧ и СВЧ электронике широко применяются транзисторные усилители переменного тока с парафазным выходом, реализованные на базе классического дифференциального каскада с подключением источника сигнала непосредственно к базе входного транзистора через разделительный конденсатор [1-17].

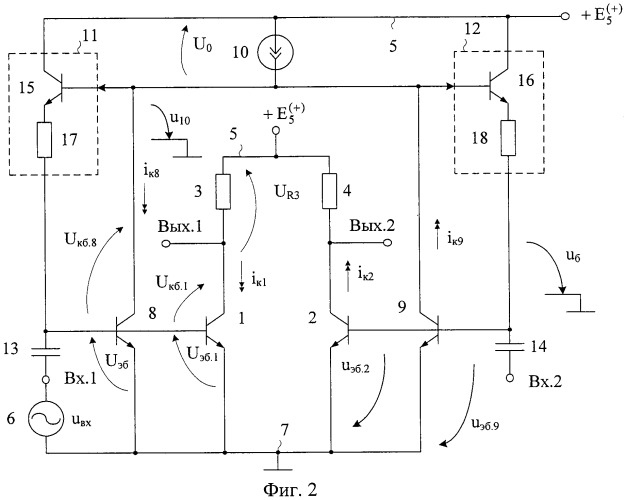

Наиболее близким по технической сущности к заявляемому устройству является усилитель переменного тока фиг.1, рассмотренный в патентной заявке США №2009/0219094. Эта же структура присутствует в патентах JP 2003037438, US 6.265.908, патентной заявке US 2008/0122538 и др.

Существенный недостаток известного усилителя переменного тока (УпТ) состоит в том, что при малых напряжениях питания его коэффициент усиления по напряжению получается небольшим. Это связано с неэффективным использованием напряжений его двух источников питания, обусловленным особенностями архитектуры УпТ-прототипа. Действительно, для обеспечения работоспособности УпТ-прототипа необходимо иметь два источника питания - и . Причем непосредственно «не участвует» в усилении сигналов, так как служит только для обеспечения статического режима по току транзисторов. С другой стороны, напряжение , существенно влияющее на численные значения коэффициента усиления по напряжению (Kу), определяет также численные значения амплитуд положительного и отрицательного выходного напряжения УпТ, так как

, , ,

где Uкб.1 - статическое напряжение коллектор-база транзистора 1;

UR3 - статическое напряжение на двухполюснике (резисторе) нагрузки 3.

Основная задача предлагаемого изобретения состоит в повышении эффективности использования напряжения питания. Конкретно это выражается в получении более высокого Kу при одинаковом с прототипом напряжении питания и использовании в качестве двухполюсников нагрузки резисторов.

Поставленная задача достигается тем, что в усилителе переменного тока с парафазным выходом фиг.1, содержащем первый 1 и второй 2 входные транзисторы с объединенными эмиттерами, первый 3 и второй 4 двухполюсники цепи нагрузки, включенные между первой шиной 5 источника питания и соответствующими коллекторами первого 1 и второго 2 входных транзисторов, источник сигнала 6, связанный по переменному току с базой первого входного транзистора 1, вторую шину 7 источника питания, предусмотрены новые элементы и связи - в схему введены первый 8 и второй 9 дополнительные транзисторы, эмиттеры которых объединены с эмиттерами первого 1 и второго 2 входных транзисторов и подключены ко второй шине 7 источника питания, база первого дополнительного транзистора 8 соединена с базой первого входного транзистора 1, база второго дополнительного транзистора 9 подключена к базе второго входного транзистора 2, коллекторы первого 8 и второго 9 дополнительных транзисторов объединены и через дополнительный двухполюсник 10 связаны с первой шиной 5 источника питания, причем объединенные коллекторы первого 8 и второго 9 дополнительных транзисторов связаны соответствующими базами первого 1 и второго 2 входных транзисторов через соответствующие первый 11 и второй 12 дополнительные неинвертирующие усилители.

На фиг.1 представлена схема усилителя переменного тока - прототип.

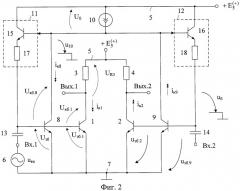

На фиг.2 представлена схема заявляемого УпТ в соответствии с п.1, п.2 и и.3 формулы изобретения.

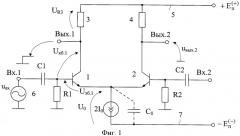

На фиг.3 приведена схема УпТ, соответствующая п.4 формулы изобретения.

На фиг.4 показана схема фиг.2 в среде компьютерного моделирования Cadence на моделях интегральных транзисторов IHP, а на фиг.5 и фиг.6 - зависимость коэффициентов усиления для дифференциального выхода (фиг.5), а также для первого (out1) и второго (out2) выходов (фиг.6) от частоты.

Усилитель переменного тока с парафазным выходом фиг.2 содержит первый 1 и второй 2 входные транзисторы с объединенными эмиттерами, первый 3 и второй 4 двухполюсники цепи нагрузки, включенные между первой 5 шиной источника питания и соответствующими коллекторами первого 1 и второго 2 входных транзисторов, источник сигнала 6, связанный по переменному току с базой первого входного транзистора 1, вторую шину 7 источника питания. В схему введены первый 8 и второй 9 дополнительные транзисторы, эмиттеры которых объединены с эмиттерами первого 1 и второго 2 входных транзисторов и подключены ко второй шине 7 источника питания, база первого дополнительного транзистора 8 соединена с базой первого входного транзистора 1, база второго дополнительного транзистора 9 подключена к базе второго входного транзистора 2, коллекторы первого 8 и второго 9 дополнительных транзисторов объединены и через дополнительный двухполюсник 10 связаны с первой шиной 5 источника питания, причем объединенные коллекторы первого 8 и второго 9 дополнительных транзисторов связаны соответствующими базами первого 1 и второго 2 входных транзисторов через соответствующие первый 11 и второй 12 дополнительные неинвертирующие усилители. Источник входного сигнала 6 соединен с базой первого входного транзистора 1 через первый разделительный конденсатор 13. Аналогично второй источник сигнала может подключаться к схеме через второй разделительный конденсатор 14.

На фиг.2 в соответствии с п.2 формулы изобретения в качестве первого 11 и второго 12 дополнительных неинвертирующих усилителей используются эмиттерные повторители на первом 15 и втором 16 вспомогательных транзисторах.

На фиг.2 в соответствии с п.3 формулы изобретения в эмиттерные цепи первого 15 и второго 16 вспомогательных транзисторов введены первый 17 и второй 18 вспомогательные резисторы.

На фиг.3 в соответствии с п.4 формулы изобретения в качестве первого 11 и второго 12 дополнительных неинвертирующих усилителей применяются транзисторные каскады по схеме с общей базой.

Рассмотрим работу УпТ фиг.2.

В заявляемом УпТ напряжение питания используется более эффективно, чем в прототипе. Во-первых, в схеме исключен второй источник напряжения питания , устанавливающий статический режим общей эмиттерной цепи входных транзисторов 1 и 2. Непосредственное подключение эмиттеров входных транзисторов 1 и 2 ко второй шине 7 источника питания при сохранении УпТ свойств фазорасщепителя по первому (Вых.1) и второму (Вых.2) выходам позволяет при одинаковых величинах напряжения питания у сравниваемых схем получить в заявляемом устройстве более высокое значение Kу. Действительно для УпТ-прототипа фиг.1 и заявляемого устройства фиг.2 коэффициенты усиления (, ) по напряжению:

где , - напряжение положительного и отрицательного источников питания;

U0≈0,7 B - минимально возможное напряжение на дополнительном двухполюснике 10 при его реализации на биполярном транзисторе;

Uэб.1≈0,7 В - напряжение эмиттер-база входного транзистора 1 в статическом режиме;

- напряжение коллектор-база транзистора 1 в статическом режиме;

- амплитуда отрицательной полуволны выходного напряжения;

φт≈26 мВ - температурный потенциал.

Если предположить, что , то при выигрыш по Kу, как это следует из (1) и (2), достигает величины Nу≥2,5.

Статический режим транзисторов 1 и 2 схемы фиг.2 устанавливается дополнительным двухполюсником 10 (I10):

Рассмотрим далее работу схемы фиг.2 при подаче на левый вход (Вх.1) положительной полуволны входного сигнала uвх.. Изменение uвх приводит к увеличению эмиттерных токов транзисторов 1, 8:

где rэi - сопротивление эмиттерных переходов транзисторов 1 и 8.

Как следствие, уменьшается напряжение на дополнительном двухполюснике 10, которое через дополнительный неинвертирующий усилитель 12 с единичным коэффициентом передается на базу транзисторов 2 и 9:

Напряжение запирает транзисторы 2 и 9 так, что приращения токов iк9+iк8=0, т.е. в схеме фиг.2:

Таким образом, в схеме фиг.2 токи коллекторов транзисторов 1 и 2, а также 8 и 9 противофазны, но равны друг другу: iк1≈iк2, iк8≈iк9. Следовательно, противофазны и выходные напряжения uвых.1 и uвых.2 для выходов Вых.1 и Вых.2.

Данные теоретические выводы соответствуют результатам компьютерного моделирования схемы фиг.4, представленным графиками фиг.5, фиг.6.

В усилителе переменного тока фиг.3, который реализуется в базисе элементов техпроцесса SGB25H2, передача приращения напряжения u10 в базовую цепь транзисторов 2 и 9 обеспечивается более высокочастотным, чем в схеме фиг.2, каналом на транзисторе по схеме с общей базой.

Таким образом, заявляемое устройство выполняет функции СВЧ-усилителя (Kу>40 дБ), обеспечивающего также преобразование в диапазоне частот до 2÷2,5 ГГц однофазного сигнала в два противофазных. Данная функция в усилителе-прототипе не реализуется.

Источники информации

1. Патент США №4.005.371, fig.3.

2. Патентная заявка США №2008/0265992, fig.2.

3. Патент JP №2003037458.

4. Патент США №6.265.908, fig.1.

5. Патент США №4.885.550.

6. Патентная заявка WO 2005/039045.

7. Патентная заявка США №2007/0205829, fig.3B.

8. Патентная заявка США №2005/0200412, fig.1.

9. Патентная заявка США №2008/0122538, fig.2.

10. Патентная заявка США №2005/0206450, fig.2.

11. Патентная заявка США №2008/0231362, fig.2.

12. Патентная заявка США №2009/0219094, fig.1.

13. Патент США №3.843.935, fig.2.

14. Патент JP №52-139346, кл. 98(5) A31.

15. Патент JP №53-38246, кл. 98(5) A31 H03F 3/45.

16. Патентная заявка США №2005/0233714, fig.2.

17. Патент JP 55078612.

1. Усилитель переменного тока с парафазным выходом, содержащий первый (1) и второй (2) входные транзисторы с объединенными эмиттерами, первый (3) и второй (4) двухполюсники цепи нагрузки, включенные между первой (5) шиной источника питания и соответствующими коллекторами первого (1) и второго (2) входных транзисторов, источник сигнала (6), связанный по переменному току с базой первого (1) входного транзистора, вторую (7) шину источника питания, отличающийся тем, что в схему введены первый (8) и второй (9) дополнительные транзисторы, эмиттеры которых объединены с эмиттерами первого (1) и второго (2) входных транзисторов и подключены ко второй (7) шине источника питания, база первого (8) дополнительного транзистора соединена с базой первого (1) входного транзистора, база второго (9) дополнительного транзистора подключена к базе второго (2) входного транзистора, коллекторы первого (8) и второго (9) дополнительных транзисторов объединены и через дополнительный двухполюсник (10), устанавливающий статический режим первого (1) и второго (2) входных транзисторов, связаны с первой (5) шиной источника питания, причем объединенные коллекторы первого (8) и второго (9) дополнительных транзисторов связаны соответствующими базами первого (1) и второго (2) входных транзисторов через соответствующие первый (11) и второй (12) дополнительные неинвертирующие усилители.

2. Усилитель по п.1, отличающийся тем, что первый (11) и второй (12) дополнительные неинвертирующие усилители являются эмиттерными повторителями на первом (15) и втором (16) вспомогательных транзисторах.

3. Усилитель по п.2, отличающийся тем, что в эмиттерные цепи первого (15) и второго (16) вспомогательных транзисторов введены первый (17) и второй (18) вспомогательные резисторы.

4. Усилитель по п.1, отличающийся тем, что первый (11) и второй (12) дополнительные неинвертирующие усилители выполнены на транзисторных каскадах по схеме с общей базой.