Мультиплексор

Иллюстрации

Показать всеИзобретение относится к области связи для уменьшения количества каналов. Технический результат: улучшение качества соединения компонентов, смонтированных на печатной плате, за счет уменьшения перекрестных наводок между каналами, уменьшение размеров корпуса и печатной платы. Устройство мультиплексирования (УМ) (1), имеющее М высокочастотных входных каналов (2) и N высокочастотных выходных каналов (3). УМ (1) содержит N направляющих управляющих входов (4); детектор (10), выполненный с возможностью приема управляющих сигналов на управляющем входе (4) или на каждом управляющем входе (4), при этом управляющие сигналы указывают требуемое соединение между входными каналами (2) УМ (1) и выходными каналами (3); и декодер (11), выполненный с возможностью декодирования управляющих сигналов и генерирования переключающих управляющих сигналов (8) для выборочного соединения входных каналов (2) с выходными каналами (3) в ответ на декодированные управляющие сигналы. УМ (1) интегрирован в одну интегральную микросхему. Система мультиплексирования содержит пару таких УМ (1), смонтированных на печатной плате. УМ (1) расположены на противоположных сторонах печатной платы, причем одно УМ (1) повернуто на 180 градусов вокруг диагональной оси (20) относительно другого УМ (1). 2 н. и 21 з.п. ф-лы, 3 ил., 6 табл.

Реферат

Область техники, к которой относится изобретение

Настоящее изобретение относится к мультиплексору. В частности, но не исключительно, настоящее изобретение относится к высокочастотному мультиплексору, выполненному с возможностью выборочно соединять один или более входных каналов с одним или более выходными каналами.

Уровень техники

Мультиплексор осуществляет выборочное соединение входных каналов с выходными каналами в ответ на один или более управляющих сигналов. Например, мультиплексор 4:2 осуществляет выборочное подключение 4 входных каналов к 2 выходным каналам в ответ на управляющие сигналы, подаваемые на мультиплексор. Управляющие сигналы обычно подаются на мультиплексор с внешней схемы. Может присутствовать любое количество входных каналов и выходных каналов. Мультиплексор может быть выполнен с возможностью выборочного соединения нескольких входных каналов с меньшим числом выходных каналов. Альтернативно, мультиплексор может быть выполнен с возможностью выборочного соединения одного или более входного канала с большим числом выходных каналов.

Мультиплексоры обычно используются в компьютерах и другом электронном оборудовании, чтобы направлять (маршрутизировать) сигналы между различными компонентами, например, по шине данных, для уменьшения количества необходимых соединений. Мультиплексоры также обычно используются в сетях связи для уменьшения количества каналов, требуемых для связи на дальние расстояния, и, таким образом, обеспечивают снижение затрат.

В мультиплексоре желательна возможность подключения любого выбранного входного канала к любому выбранному выходному каналу. Для мультиплексоров, которые применяются для передачи высокочастотных сигналов, с увеличением частоты становится сложнее поддерживать изоляцию между каналами. Если каналы недостаточно изолированы, между каналами может происходить перекрестная наводка. Хорошая изоляция становится особенно сложно достижимой на частотах свыше 100 МГц, поскольку с увеличением частоты перекрестная наводка становится все более всеобъемлющей.

Известные высокочастотные мультиплексоры обычно содержат несколько отдельных компонентов, смонтированных на печатной плате. По существу, это может привести к проблемам при соединении компонентов, из-за того, что пути сигналов между компонентами проходят вблизи или через друг друга. Это становится все более проблематично по мере увеличения количества каналов для сигналов.

Раскрытие изобретения

Цель данного изобретения состоит в устранении или смягчении одной или большего количества описанных проблем существующего уровня техники.

Согласно первому аспекту настоящего изобретения, предлагается мультиплексор, который имеет М высокочастотных входных каналов и N высокочастотных выходных каналов, содержащий N направляющих управляющих входов; детектор, выполненный с возможностью получения управляющих сигналов на управляющем входе или на каждом из управляющих входов, при этом управляющие сигналы указывают требуемое соединение между входными каналами мультиплексора и выходными каналами мультиплексора; и декодер, выполненный с возможностью декодирования принятых управляющих сигналов и генерирования переключающих управляющих сигналов для выборочного соединения входных каналов с выходными каналами в ответ на декодированные управляющие сигналы; при этом мультиплексор интегрирован в одну интегральную микросхему.

Преимуществом вариантов осуществления настоящего изобретения является то, что посредством интегрирования детектора и декодера в одну интегральную микросхему (один чип) уменьшается проблема перекрестных наводок между каналами. Это происходит по той причине, что упрощаются требования к маршрутизации каналов на печатной плате, на которой размещается мультиплексор. Посредством интегрирования всей функции детектора/декодера с одним управляющим выводом на канал уменьшается сложность проектирования печатной платы, благодаря чему снижаются затраты. Дополнительно, это ведет к уменьшению количества контактов, которые должны присутствовать на мультиплексоре, уменьшая интегральную схему, размер корпуса и платы, благодаря чему также снижаются затраты.

Предпочтительно, мультиплексор выполнен с возможностью приема входных сигналов на входных каналах на частоте до 3 ГГц и выдачи выходных сигналов на частоте до 3 ГГц.

Предпочтительно, мультиплексор выполнен в корпусе таким образом, что входные каналы и выходные каналы расположены симметрично относительно диагональной оси корпуса. Это выгодно облегчает монтаж двух мультиплексоров один над другим на обеих сторонах печатной платы. Один мультиплексор может быть повернут на 180° вокруг диагональной оси.

Предпочтительно, каждый входной канал соединен с переключателем входного буфера, при этом каждый переключатель входного буфера выполнен с возможностью соединения своего соответствующего входного канала с одним или большим количеством выходных каналов в ответ на переключающие управляющие сигналы.

Переключатели входного буфера могут быть выполнены с возможностью отсоединения входного канала от выходных каналов и функционирования в энергосберегающем режиме в ответ на соответствующий переключающий управляющий сигнал. Каждый переключатель входного буфера может быть выполнен с возможностью усиления входных сигналов на входном канале в случае, когда переключатель находится не в энергосберегающем режиме. Предпочтительно, каждый переключатель входного буфера выполнен с возможностью обеспечения входного импеданса, согласованного с импедансом входного канала, для входного канала.

Предпочтительно, мультиплексор также содержит интерфейс, выполненный с возможностью приема переключающих управляющих сигналов от декодера и генерирования соответствующих уровней аналогового напряжения для приведения в действие транзисторов в каждом переключателе входного буфера.

Предпочтительно, мультиплексор также содержит логический управляющий вход, при этом мультиплексор выполнен с возможностью изменения выборочного соединения входных каналов с выходными каналами в зависимости от логического управляющего сигнала, принимаемого на логическом управляющем входе. Изменение состояния логического управляющего сигнала может инвертировать порядок соединения входных каналов с выходными каналами.

Количество входных каналов может быть четным. Количество выходных каналов может быть четным. Может иметься четыре входных канала и два выходных канала.

Управляющие сигналы могут содержать уровень напряжения постоянного тока. Детектор может быть выполнен с возможностью обнаружения, находится ли уровень напряжения постоянного тока выше или ниже порогового напряжения. Детектор может быть выполнен с возможностью сравнения уровня напряжения постоянного тока с рядом пороговых значений.

Управляющие сигналы могут содержать сигнал напряжения переменного тока. Детектор может быть выполнен с возможностью обнаружения, имеет ли сигнал переменного тока на предварительно заданной частоте амплитуду большую или меньшую пороговой амплитуды. Предварительно заданная частота может являться предварительно заданной полосой частот. Управляющие сигналы могут содержать несколько сигналов переменного тока.

Предпочтительно, мультиплексор также содержит N выходных каскадов, каждый выходной каскад приводит в действие соответствующий выходной канал. Каждый входной канал может быть соединен с каждым выходным каскадом, а каждый выходной каскад выполнен с возможностью приведения в действие соответствующего выходного канала с помощью входного сигнала, принятого на одном входном канале.

Выходной каскад или каждый выходной каскад может содержать по меньшей мере один выходной транзистор, при этом ток, протекающий внутри выходного транзистора или каждого выходного транзистора, управляется низкочастотным контуром обратной связи путем сравнения тока в каждом выходном транзисторе с опорным током.

Предпочтительно, каждый выходной каскад выполнен с возможностью обеспечения выходного импеданса, согласованного с импедансом выходного канала, для выходного канала.

Согласно второму аспекту настоящего изобретения предлагается система мультиплексоров, содержащая пару мультиплексоров, охарактеризованных в пункте 3 формулы изобретения, смонтированных на печатной плате, при этом мультиплексоры расположены на противоположных сторонах печатной платы, а один мультиплексор повернут на 180 градусов вокруг диагональной оси относительно другого мультиплексора.

Входы пары мультиплексоров могут быть соединены друг с другом через печатную плату, образуя мультиплексор с М входами и 2N выходами.

Краткое описание чертежей

Настоящее изобретение будет описано далее, исключительно на примерах, со ссылкой на прилагаемые чертежи, на которых:

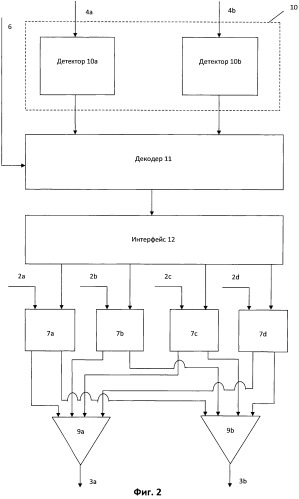

на фиг.1 схематично показан мультиплексор в соответствии с вариантом осуществления настоящего изобретения;

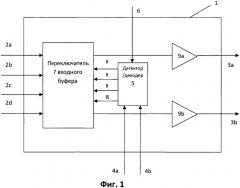

на фиг.2 схематически показана часть мультиплексора по фиг.1; и

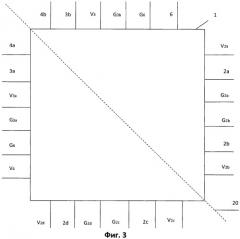

на фиг.3 схематически показан корпус интегральной микросхемы для мультиплексора по фиг.1.

Осуществление изобретения

Критическим параметром в проектировании высокочастотного мультиплексора является изоляция между входными и выходными каналами. Перекрестные наводки между каналами могут происходить в результате взаимодействий, возникающих в интегральных схемах, в корпусе, в котором размещена интегрированная схема, и из-за того, каким образом корпус смонтирован на печатной плате. Для мультиплексоров в соответствии с вариантами осуществления по настоящему изобретению изоляция между входными и выходными каналами максимальна. В частности, это достигается принятием во внимание того факта, что топология интегральной схемы и выбор корпуса и распределения контактов образуют важную часть проектирования интегральной схемы и должны быть смоделированы как единая система вплоть до частот, где высокочастотная нестабильность не представляет опасности. Мультиплексоры в соответствии с вариантом осуществления настоящего изобретения выполняются с возможностью работы на частоте вплоть до 3 ГГц. Таким образом, моделирование мультиплексора вплоть до частоты порядка 5 ГГц гарантирует, что мультиплексор соответствует требуемым параметрам устройства и обеспечивает стабильность на высоких частотах. Другие важные параметры включают неравномерность амплитудно-частотной характеристики полосы частот, входной и выходной импеданс, поведение при шуме и искажениях. Эти параметры могут быть оптимизированы путем выполнения мультиплексора в соответствии с представленной моделью мультиплексора.

На фиг.1 показан высокочастотный мультиплексор 4:2 в соответствии с одним из вариантов осуществления настоящего изобретения, выполненный как одна интегральная микросхема. Мультиплексор 1 имеет четыре высокочастотных входа 2 (обозначенных, соответственно, 2а-2d) и два высокочастотных выхода 3 (обозначенных, соответственно, 3a и 3b). Мультиплексор 1 имеет два направляющих управляющих входа 4 (обозначенных, соответственно, 4а и 4b). Направляющие управляющие входы 4 подают управляющие сигналы на детектор/декодер 5. Детектор/декодер 5 также имеет логический управляющий вход 6. Логический управляющий вход 6 позволяет осуществить логическую инверсию последовательности высокочастотных входов 2, как поясняется ниже.

Детектор/декодер 5 выполнен с возможностью обнаружения управляющих сигналов, принимаемых на направляющих управляющих входах 4 в виде одной или нескольких частот переменного тока и/или уровня постоянного тока. Эти управляющие сигналы подаются на мультиплексор 1 с внешней схемы (не показана), которая управляет мультиплексором. В варианте осуществления изобретения, показанном на фиг.1, управляющие сигналы подаются на направляющие управляющие входы 4 как уровень постоянного тока и/или как частота переменного тока.

Например, детектор/декодер 5 может для каждого контакта обнаруживать единственный уровень постоянного тока и единственный уровень переменного тока. Если обнаруженный уровень постоянного тока меньше или равен 14 В, то это соответствует логическому низкому сигналу. Если уровень постоянного тока больше или равен 15 В, это соответствует логическому высокому сигналу. Сигнал переменного тока может измеряться в полосе пропускания порядка 22 кГц. Если размах амплитуды сигнала переменного тока больше или равен 300 мВ, то это соответствует логическому высокому сигналу. Если размах амплитуды переменного тока меньше или равен 100 мВ, то это соответствует логическому низкому сигналу.

Специалистам понятно, что декодер/детектор 5 может быть выполнен с возможностью одновременного обнаружения сигналов переменного тока на других частотах или около других частот. Детектор/декодер 5 может также быть выполнен с возможностью различать диапазон уровней напряжения постоянного тока, соответствующих различным входным значениям. Сигналы переменного тока и постоянного тока, которые детектор/декодер 5 способен обнаруживать, могут меняться со временем.

Таким образом, детектор/декодер способен получать многобитные управляющие сигналы, на основании отсутствия или наличии нескольких сигналов постоянного или переменного тока на каждом направляющем управляющем входе 4.

Сигналы постоянного или переменного тока, подаваемые на каждый направляющий управляющий вход 4, могут в альтернативном варианте называться поляризационным и тоновым сигналами соответственно. Высокочастотные входы 2 принимаются переключателем 7 входного буфера. Переключатель 7 входного буфера управляется переключающими управляющими сигналами 8, подаваемыми детектором/декодером 5 в ответ на управляющие сигналы, получаемые на направляющих управляющих входах 4. Переключающие управляющие сигналы 8 выборочно переключают высокочастотные входы на два выходных каскада 9 (обозначенных, соответственно, 9а и 9b). Переключатель 7 входного буфера также осуществляет предварительное усиление входных высокочастотных сигналов. Выходные каскады 9 подают выходные сигналы на высокочастотные выходы 3.

Для одного высокочастотного выходного канала 3 необходим только один направляющий управляющий вход 4, хотя могут присутствовать дополнительные направляющие управляющие входы. Причина этого заключается в том, что каждый направляющий управляющий вход 4 проводит несколько управляющих сигналов в виде компонент постоянного и переменного тока. Функциональность детектора/декодера специфична для предназначенного применения мультиплексора. Примерный вариант осуществления изобретения на фиг.1 может быть легко расширен до любого количества входов и выходов. Это возможно потому, что управляющие сигналы подаются на каждый направляющий управляющий вход 4 извне. Декодер может быть легко модифицирован для адаптирования к другим комбинациям входов и выходов.

Также могут быть использованы другие способы передачи сигналов переменного тока, которые требуют модификации детектора/декодера 5. Настоящее изобретение не ограничено каким-либо конкретным способом передачи сигналов. Конфигурация направляющих управляющих входов и сигналов на фиг.1 является просто примером.

Интеграция детектора/декодера 5 с единственным направляющим управляющим входом 4 на каждый выходной канал 3 уменьшает сложность конструкции и стоимость печатной платы, поскольку не требуется внешних компонентов, что экономит пространство на плате и уменьшает стоимость компонентов.

Выходные каскады 9 обеспечивают дальнейшее усиление высокочастотных выходных сигналов, а также функциональность возбудителя линии, так что при обычном использовании не требуется дополнительного высокочастотного возбудителя линии, внешнего по отношению к мультиплексору 1. Это устраняет необходимость в дополнительных усилителях на печатной плате, и тем самым уменьшает сложность и стоимость систем, использующих мультиплексор 1.

Далее на фиг.2 компоненты мультиплексора показаны более детально. Детектор/декодер 5 с фиг.1 разбит на каскад 10 детектора и декодер 11. Каскад 10 детектора содержит два отдельных детектора 10а и 10b, каждому из которых в качестве входа служит один из направляющих управляющих входов 4а и 4b. Детекторы 10а, 10b обнаруживают управляющие сигналы на направляющих управляющих входах 4а и 4b, соответственно, и передают обнаруженные управляющие сигналы в декодер 11.

Каждый детектор 10а, 10b принимает как вход комбинированные уровень напряжения и сигнал переменного тока. Каждый детектор независимо проверяет, выше или ниже уровень постоянного тока относительно порога, индивидуального для данного приложения (например, 14 В), и проверяет, превышает ли сигнал переменного тока определенную амплитуду, и находится ли он в рамках допустимого диапазона частот (например, размах амплитуды больше или равен 300 мВ на частоте 22 кГц). Детекторы также оснащены входными фильтрами, предназначенными для отклонения других мешающих сигналов, которые могут присутствовать.

Обнаруженные управляющие сигналы, передаваемые в декодер 11 с детекторов 10, представляют собой цифровые сигналы и могут присутствовать на нескольких управляющих линиях. Декодер 11 декодирует управляющие сигналы для генерации желаемой таблицы истинности. Декодер 11 имеет еще один вход, логический управляющий вход 6. Логический управляющий вход служит для инверсии таблицы истинности для каждого выходного канала 3, так, чтобы входной канал 2, выбранный для каждого выходного канала, менялся, при изменении логического состояния логического управляющего входа. Таблица истинности для мультиплексора 4:2 с фиг.1 и фиг.2 показана ниже:

| Таблица истинности, выходной канал 3а | |||

| Переменный ток, 4а | Постоянный ток, 4а | Логический управляющий вход 6 | Выбранный входной канал |

| 1 | 0 | 0 | 2а |

| 0 | 0 | 0 | 2b |

| 0 | 1 | 0 | 2с |

| 1 | 1 | 0 | 2d |

| 1 | 0 | 1 | 2d |

| 0 | 0 | 1 | 2с |

| 0 | 1 | 1 | 2b |

| 1 | 1 | 1 | 2а |

| Таблица истинности, выходной канал 3b | |||

| Переменный ток, 4b | Постоянный ток, 4b | Логический управляющий вход 6 | Выбранный входной канал |

| 1 | 0 | 0 | 2а |

| 0 | 0 | 0 | 2b |

| 0 | 1 | 0 | 2с |

| 1 | 1 | 0 | 2d |

| 1 | 0 | 1 | 2d |

| 0 | 0 | 1 | 2с |

| 0 | 1 | 1 | 2b |

| 1 | 1 | 1 | 2а |

Декодированные сигналы передаются в интерфейс 12. Интерфейс 12 преобразует цифровые декодированные сигналы в соответствующие аналоговые уровни, чтобы приводить в действие аналоговые переключатели в переключателе 7 входного буфера. Требуемые для этого аналоговые напряжения для переключателя 7 входного буфера индивидуальны для конкретных приложений.

Переключатель 7 входного буфера, показанный как один компонент на фиг.1, фактически содержит отдельные переключатели входного буфера (обозначенные, соответственно 7а-7d) для каждого высокочастотного входа 2а-2d. Согласно переключающим управляющим сигналам 8, передаваемым интерфейсом в каждый переключатель входного буфера, переключатели входного буфера могут передавать высокочастотные входные сигналы на любой выходной каскад 9а или 9b или на оба выходных каскада. Переключающие управляющие сигналы 8 могут быть переданы в каждый переключатель 7 входного буфера по нескольким управляющим линиям.

Мультиплексор 1 оснащен схемами защиты от электростатического разряда для предотвращения возможного повреждения внутренних компонентов. Схемы защиты от электростатического разряда подключены к каждому из входных каналов 2, выходных каналов 3, направляющих управляющих входов 4 и логическому управляющему входу 6.

Переключатели 7 входного буфера выполнены так, что они соединяют сигнал на соответствующем высокочастотном входе 2 с первым выходным каскадом 9а, вторым выходным каскадом 9b, либо же ни с одним из выходных каскадов, как определяется управляющими сигналами с интерфейса 12. Когда переключателю входного буфера задано не передавать свой вход в выходной каскад, он может быть переведен в энергосберегающий режим. В энергосберегающем режиме неиспользуемые части схемы в переключателе входного буфера переключаются в неактивное состояние нулевого потребления энергии. Тем самым выключаются нормальный входной каскад и переключаемые выходные каскады переключателя 7 входного буфера, и включается резервный активный входной каскад низкой мощности, который поддерживает требуемое согласование импедансов для входного канала 2.

Когда переключатель 7 входного буфера должен направлять свой входной сигнал в выходной каскад 9, тогда внутренний предусилитель обеспечивает соответствующий согласованный входной импеданс для входного канала и усиливает высокочастотный сигнал с допустимой шумовой характеристикой. В варианте осуществления настоящего изобретения, показанном на фиг.1 и фиг.2, шумовая характеристика может быть менее или равна 15 дБ. Входной импеданс каждого переключателя 7 входного буфера выбран так, чтобы соответствовать характеристикам подключенного высокочастотного входного канала 2 (номинально 50 Ом).

Усиленный входной сигнал подается в два переключаемых буферных каскада (внутренних по отношению к переключателям 7 входного буфера), оба, один, или же ни один из которых может быть активирован, в зависимости от переключающих управляющих сигналов 8, получаемых с интерфейса 12. Каждый переключаемый буферный каскад имеет выход, соединенный с одним из выходных каскадов 9, так что каждый выходной каскад 9 имеет вход, подключенный к каждому из переключателей 7 входного буфера. Если вход переключателя 7 входного буфера не должен быть направлен в один или оба выходных каскада 9, то сигнал блокируется одним или обоими переключаемыми буферными каскадами.

Переключатели входного буфера управляются переключающими управляющими сигналами 8, принимаемыми с интерфейса 12, и поэтому, в конечном счете, управляются управляющими сигналами, обнаруженными детекторами 10.

Высокочастотные функциональные средства мультиплексора 1 выполнены симметрично относительно диагонали корпуса. Мультиплексор 1 выполняется так, чтобы пара мультиплексоров могла быть смонтирована вертикально один над другим на каждой стороне печатной платы, образуя систему малого форм-фактора для двух мультиплексоров 4:2. Опционально входы 2 могут быть электрически соединены через плату. Когда входы 2 соединены таким образом, образуется мультиплексор 4:4, имеющий ту же самую таблицу истинности, что и два устройства по отдельности. Когда они не соединены, имеются два независимых мультиплексора 4:2.

Симметрия корпуса выбрана относительно диагонали, так что для мультиплексора 4:2 два выхода могут быть расположены на соседних сторонах четырехугольного корпуса, а четыре входа могут быть расположены на другой паре соседних сторон. Вклад в изоляцию корпуса в этом случае максимален, поскольку входы и выходы разнесены как можно дальше от друга. Выгодным образом, монтирование мультиплексоров друг над другом таким образом обеспечивает простую и эффективную топологию платы. Таблица истинности для всех четырех выходных каналов мультиплексоров такая же, как показана выше для двух мультиплексоров. Поскольку устройства на противоположных сторонах печатной платы перевернуты относительно друг друга, та же последовательность входов восстанавливается выбором противоположных логических состояний для логических управляющих входов 6. Таблица истинности (где 3х_1, 4х_1 и 3х_2, 4х_2 относятся, соответственно, к противоположным сторонам печатной платы) тогда может быть такой:

| Таблица истинности, выходной канал 3а_1 | |||

| Переменный ток, 4а_1 | Постоянный ток, 4а_1 | Логический управляющий вход 6 | Выбранный входной канал |

| 1 | 0 | 0 | 2а |

| 0 | 0 | 0 | 2b |

| 0 | 1 | 0 | 2с |

| 1 | 1 | 0 | 2d |

| Таблица истинности, выходной канал 3а_2 | |||

| Переменный ток, 4а_2 | Постоянный ток, 4а_2 | Логический управляющий вход 6 | Выбранный входной канал |

| 1 | 0 | 1 | 2а |

| 0 | 0 | 1 | 2b |

| 0 | 1 | 1 | 2с |

| 1 | 1 | 1 | 2d |

| Таблица истинности, выходной канал 3b_1 | |||

| Переменный ток, 4b_1 | Постоянный ток, 4b_1 | Логический управляющий вход 6 | Выбранный входной канал |

| 1 | 0 | 0 | 2а |

| 0 | 0 | 0 | 2b |

| 0 | 1 | 0 | 2с |

| 1 | 1 | 0 | 2d |

| Таблица истинности, выходной канал 3b_2 | |||

| Переменный ток, 4b_2 | Постоянный ток, 4b_2 | Логический управляющий вход 6 | Выбранный входной канал |

| 1 | 0 | 1 | 2а |

| 0 | 0 | 1 | 2b |

| 0 | 1 | 1 | 2с |

| 1 | 1 | 1 | 2d |

Выходы не обязательно должны быть симметрично расположены, так как они используются независимо друг от друга. В настоящем примере, поскольку имеется два выхода, они симметричны в оптимальном расположении контактов.

Выходные каскады 9 всегда активны. То есть каждый выходной каскад 9 всегда приводится в действие выбранным переключателем 7 входного буфера. Каждый выходной каскад принимает сигнал от одного активного из четырех переключателей 7 входного буфера и приводит в действие выходную нагрузку, подключенную к выходному каналу 3 с соответствующим согласованным выходным импедансом (в настоящем примере номиналом 75 Ом) и низким искажением (в настоящем примере типично искажение третьего порядка (IP3) около 16 дБм).

Ток в выходных транзисторах внутри выходных каскадов 9 управляется низкочастотным контуром обратной связи. Низкочастотный контур обратной связи усиливает реальный ток до желаемого уровня путем сравнения с опорным током. Это позволяет работать с относительно малорегулируемым напряжением питания. Производительность выходных каскадов в полосе пропускания определяется отрицательной обратной связью, которая также обеспечивает управляемый входной импеданс для каждого выходного каскада 9 на стороне выхода переключателей 7 входного буфера. Это уменьшает взаимозависимость переключателей 7 входного буфера и выходных каскадов 9.

Далее на фиг.3 схематически показано расположение входных и выходных контактов корпуса для реализации мультиплексора, показанного на фиг.1 и 2. Соответствующие входы и выходы обозначены теми же самыми ссылочными номерами. Входы и выходы расположены симметрично относительно диагональной оси 20 мультиплексора 1. Это сделано для того, чтобы гарантировать возможность монтирования двух мультиплексоров друг над другом на противоположных сторонах печатной платы путем переворота одного из мультиплексоров на 180 градусов вокруг диагональной оси 20. При этом входы 2 и выходы 3 выстраиваются верно, так что при необходимости входы могут быть соединены через печатную плату. Посредством обеспечения того, что логический управляющий вход 6 на первом мультиплексоре находится в другом логическом состоянии относительно логического управляющего входа на втором мультиплексоре, входы, которые направляются на выходы, на одном из мультиплексоров инвертированы. Это означает, что входы могут быть соединены вместе, и при этом по-прежнему можно обеспечить правильное функционирование каждого из мультиплексоров.

По правой стороне и нижней стороне мультиплексора 1 находятся входные каналы 2a-2d. Присутствуют соответствующие заземление и питание (обозначенные соответственно G2a и V2a, например), связанные с каждым входным каналом 2. Эти соединения питания и заземления обеспечивают подачу энергии на каждый из переключателей 7 входного буфера, связанных с каждым входным каналом 2. Управляющие входы 4а и 4b находятся на левой стороне и верхней стороне соответственно, отраженные зеркально относительно диагональной оси 20. Логический управляющий вход 6 изображен на верхней стороне. Питание V6 с левой стороны и заземление G6 обеспечивают питание на детекторе 10, декодере 11 и интерфейсе 12. Выходные каналы 3a, 3b и соответствующие заземление и питание (обозначенные, соответственно, G3a и V3a, например), находятся на левой стороне и верхней стороне, соответственно, также зеркально отраженные относительно диагональной оси 20.

Хотя в варианте осуществления изобретения, описанном выше, мультиплексор описан как мультиплексор 4:2, специалисту будет очевидно, что может иметься любое количество входов и выходов. Для вариантов осуществления настоящего изобретения, в которых два мультиплексора монтируются вертикально друг над другом с соединенными входами (одно устройство с инвертированными входами), входы должны быть расположены симметрично и поэтому должны быть кратны двум. В других отношениях количество входов и выходов ограничены только соображениями конструкции.

Другие модификации и применения настоящего изобретения будут очевидны специалистам из изложенных идей изобретения, не выходя за рамки прилагаемой формулы изобретения.

1. Устройство мультиплексирования, имеющее М высокочастотных входных каналов и N высокочастотных выходных каналов, содержащее:N направляющих управляющих входов;детектор, выполненный с возможностью приема управляющих сигналов на управляющем входе или на каждом из управляющих входов, при этом управляющие сигналы указывают требуемое соединение между входными каналами устройства мультиплексирования и выходными каналами устройства мультиплексирования; идекодер, выполненный с возможностью декодирования принятых управляющих сигналов и генерирования переключающих управляющих сигналов для выборочного соединения входных каналов с выходными каналами в ответ на декодированные управляющие сигналы;при этом устройство мультиплексирования интегрировано в одну интегральную микросхему, отличающееся тем, чтокаждый входной сигнал соединен с переключателем входного буфера, при этом каждый переключатель входного буфера выполнен с возможностью соединения своего соответствующего входного канала с одним или большим количеством выходных каналов в ответ на переключающие управляющие сигналы,переключатели входного буфера выполнены с возможностью отсоединения входного канала от выходных каналов и функционирования в энергосберегающем режиме в ответ на соответствующий переключающий управляющий сигнал, икаждый переключатель входного буфера выполнен с возможностью усиления входных сигналов на входном канале в случае, когда указанный переключатель находится не в энергосберегающем режиме.

2. Устройство по п.1, отличающееся тем, что выполнено с возможностью приема входных сигналов на входных каналах на частоте до 3 ГГц и выдачи выходных сигналов на частоте до 3 ГГц.

3. Устройство по п.1, отличающееся тем, что выполнено в корпусе, таким образом, что входные каналы и выходные каналы расположены симметрично по отношению друг к другу относительно диагональной оси корпуса, при этом входные каналы расположены по одну сторону диагональной оси, а выходные каналы расположены по другую сторону диагональной оси.

4. Устройство по п.1, отличающееся тем, что каждый переключатель входного буфера выполнен с возможностью обеспечения входного импеданса, согласованного с импедансом входного канала, для входного канала.

5. Устройство по п.1, отличающееся тем, что дополнительно содержит интерфейс, выполненный с возможностью приема переключающих управляющих сигналов от декодера и генерирования соответствующих уровней аналогового напряжения для приведения в действие транзисторов в каждом переключателе входного буфера.

6. Устройство по п.1, отличающееся тем, что дополнительно содержит логический управляющий вход, при этом устройство мультиплексирования выполнено с возможностью изменения выборочного соединения входных каналов с выходными каналами в зависимости от логического управляющего сигнала, принимаемого на логическом управляющем входе.

7. Устройство по п.6, отличающееся тем, что изменение состояния логического управляющего сигнала инвертирует порядок соединения входных каналов с выходными каналами.

8. Устройство по п.1, отличающееся тем, что количество входных каналов четно.

9. Устройство по п.1, отличающееся тем, что количество выходных каналов четно.

10. Устройство по п.1, отличающееся тем, что имеется четыре входных канала и два выходных канала.

11. Устройство по п.1, отличающееся тем, что управляющие сигналы содержат уровень напряжения постоянного тока.

12. Устройство по п.11, отличающееся тем, что детектор выполнен с возможностью обнаружения, находится ли уровень напряжения постоянного тока выше или ниже порогового напряжения.

13. Устройство по п.11, отличающееся тем, что детектор выполнен с возможностью сравнения уровня напряжения постоянного тока с рядом пороговых значений.

14. Устройство по п.1, отличающееся тем, что управляющие сигналы содержат сигнал напряжения переменного тока.

15. Устройство по п.14, отличающееся тем, что детектор выполнен с возможностью обнаружения, имеет ли сигнал переменного тока на предварительно заданной частоте амплитуду, большую или меньшую пороговой амплитуды.

16. Устройство по п.15, отличающееся тем, что предварительно заданная частота является предварительно заданной полосой частот.

17. Устройство по п.14, отличающееся тем, что управляющие сигналы содержат несколько сигналов переменного тока.

18. Устройство по п.1, отличающееся тем, что дополнительно содержит N выходных каскадов, причем каждый выходной каскад приводит в действие соответствующий выходной канал.

19. Устройство по п.18, отличающееся тем, что каждый входной канал соединен с каждым выходным каскадом, а каждый выходной каскад выполнен с возможностью приведения в действие соответствующего выходного канала с помощью входного сигнала, принятого на одном входном канале.

20. Устройство по п.18, отличающееся тем, что выходной каскад или каждый выходной каскад содержит, по меньшей мере, один выходной транзистор, при этом ток, протекающий внутри выходного транзистора или каждого выходного транзистора, управляется низкочастотным контуром обратной связи путем сравнения тока в каждом выходном транзисторе с опорным током.

21. Устройство по п.18, отличающееся тем, что каждый выходной каскад выполнен с возможностью обеспечения выходного импеданса, согласованного с импедансом выходного канала, для выходного канала.

22. Система мультиплексирования, содержащая пару устройств мультиплексирования в корпусах, охарактеризованных в п.3, смонтированных на печатной плате, при этом корпуса устройств мультиплексирования расположены на противоположных сторонах печатной платы и один корпус устройства мультиплексирования повернут на 180° вокруг диагональной оси относительно другого корпуса устройства мультиплексирования.

23. Система по п.22, отличающаяся тем, что входы пары устройств мультиплексирования в корпусах соединены друг с другом через печатную плату, образуя систему мультиплексирования с М входами и 2N выходами.