Нейросетевой преобразователь кода в частоту

Иллюстрации

Показать всеИзобретение относится к автоматике и вычислительной технике, в частности к устройствам нелинейного преобразования кода в частоту, и может быть использовано в вычислительных и управляющих комплексах в качестве нелинейного преобразователя кода в частоту, совмещающего функцию преобразования формы представления информации с ее математической переработкой по нелинейной зависимости. Техническим результатом является расширение функциональных возможностей устройства за счет использования искусственной нейронной сети и блока ее обучения, обеспечивающих реализацию требуемой нелинейной зависимости выходной частоты от входного кода. Устройство содержит два сумматора, два элемента ИЛИ, два элемента задержки, счетчик, дешифратор, память кодов, четыре элемента И, блок памяти весовых коэффициентов, блок обучения. 1 ил., 1 табл.

Реферат

Изобретение относится к автоматике и вычислительной технике, в частности к устройствам нелинейного преобразования кода в частоту, и может быть использовано в вычислительных и управляющих комплексах в качестве нелинейного преобразователя кода в частоту, совмещающего функцию преобразования формы представления информации с ее математической переработкой по нелинейной зависимости.

Наиболее близким по совокупности признаков и по технической сущности к заявляемому устройству является функциональный преобразователь "код-частота" (авторское свидетельство СССР №754407, МПК G06F 5/04, 1980), который обеспечивает формирование выходной частоты, пропорциональной входному коду; содержащий счетчик, дешифратор, память кодов, два сумматора, два элемента "ИЛИ", четыре элемента "И", два элемента задержки; группа выходов счетчика соединена через дешифратор со входами памяти кодов, выходы памяти кодов соединены через первый и второй элементы "И" с первыми входами первого и второго элементов "ИЛИ" соответственно, вторые входы которых соединены через третий и четвертый элементы "И" соответственно с первым входом устройства, второй вход которого соединен с входом первого элемента "И" и через первый элемент задержки с входом третьего элемента "И", выход первого элемента "ИЛИ" через последовательно соединенные первый и второй сумматор и счетчик соединен с выходом устройства, выход второго сумматора соединен со входом второго элемента "И" и через второй элемент задержки со входом четвертого элемента "И", выход второго элемента "ИЛИ" соединен со входом второго сумматора.

Недостатками прототипа являются его ограниченные функциональные возможности, а именно схемно-конструктивно не предусмотрены возможность использования преобразователя для реализации широкого ряда функциональных зависимостей выходной частоты от входного кода и возможность обучения устройства на реализацию требуемой зависимости выходной частоты от входного кода, так как он предназначен только для нелинейного преобразования входного кода в выходную частоту с реализацией зависимости преобразования определенного вида.

Технический результат предлагаемого изобретения направлен на расширение функциональных возможностей, а именно на реализацию различных функциональных зависимостей выходной частоты от входного кода, достигаемую за счет использования искусственной нейронной сети и блока ее обучения, обеспечивающих реализацию требуемой нелинейной зависимости выходной частоты от входного кода. Использование блока памяти весовых коэффициентов для нейронной сети позволяет использовать одно и то же устройство для реализации различных функциональных зависимостей выходной частоты от входного кода. Использование вместо сумматоров, реализующих только операцию суммирования, в устройстве сумматоров, реализующих операции суммирования и вычитания, позволяет также расширить круг воспроизводимых функциональных зависимостей.

Технический результат достигается тем, что в преобразователь кода в частоту, содержащий счетчик, дешифратор, память кодов, четыре элемента "И", два элемента "ИЛИ", два элемента задержки, группа выходов счетчика соединена через дешифратор со входами памяти кодов, выходы памяти кодов соединены через первый и второй элементы "И" с первыми входами первого и второго элементов "ИЛИ" соответственно, вторые входы первого и второго элементов "ИЛИ" соединены через третий и четвертый элементы "И" соответственно с первым входом цифрового кода устройства, второй частотный вход устройства соединен с входом первого элемента "И" и через первый элемент задержки с входом третьего элемента "И", выход первого элемента "ИЛИ" соединен с первым суммирующим входом первого сумматора, выход первого сумматора соединен со вторым входом переноса второго сумматора, выход второго сумматора соединен со входом второго элемента "И" и через второй элемент задержки со входом четвертого элемента "И", выход второго элемента "ИЛИ" соединен с первым входом второго сумматора, выход второго сумматора соединен со входом счетчика, выход переноса которого одновременно является выходом устройства;

вводятся блок памяти весовых коэффициентов и блок обучения, вход данных блока обучения соединен со входом тестовой последовательности, адресный вход блока памяти весовых коэффициентов соединен с шиной SA адреса весовых коэффициентов блока обучения, информационный вход блока памяти весовых коэффициентов соединен с шиной SD данных весовых коэффициентов блока обучения, вход разрешения записи блока памяти весовых коэффициентов соединен с выходом разрешения записи we блока обучения, выходы w1 и w2 блока памяти весовых коэффициентов соединены соответственно со вторыми входами первого и второго сумматоров, задающими режим работы сумматоров (сумматоры работают в режимах суммирования и вычитания), выходы vi (i=1,2,…,m) и ui (i=1,2,…,m) блока памяти весовых коэффициентов соединены с третьими входными шинами первого и второго сумматоров, задающими начальное значение, используемое в операциях суммирования и вычитания, выходы si (i=1,2,…,m) блока памяти весовых коэффициентов соединены со входами памяти кодов.

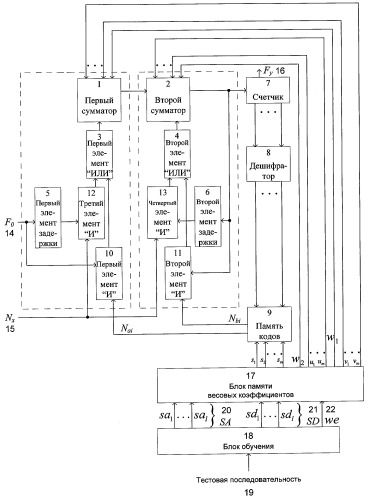

На чертеже представлена структурная схема предлагаемого устройства.

Нейросетевой преобразователь кода в частоту содержит первый сумматор 1, второй сумматор 2, первый элемент "ИЛИ" 3, второй элемент "ИЛИ" 4, первый элемент задержки 5, второй элемент задержки 6, счетчик 7, дешифратор 8, память кодов 9, первый элемент "И" 10, второй элемент "И" 11, третий элемент "И" 12, четвертый элемент "И" 13, вход опорной (эталонной) частоты F0 14, вход преобразуемого кода Nx 15, выход результирующей частоты Fy 16, блок памяти весовых коэффициентов 17, блок обучения 18, вход тестовой последовательности 19, шину SA 20 адреса весовых коэффициентов блока обучения, шину SD 21 данных весовых коэффициентов блока обучения, выход разрешения записи we 22 блока обучения.

Первый сумматор 1 реализует операцию суммирования кодов Nx и с преобразованием суммы в частоту (режим суммирования) или (режим вычитания), представляющую собой последовательность импульсов переполнения на выходе первого сумматора 1, образуемых путем переноса на его вход кодов и Nx с частотой F0 (k - число разрядов сумматора). Первый сумматор 1 является неотъемлемой частью искусственной нейронной сети преобразователя. Весовой коэффициент w1, подаваемый на второй вход первого сумматора 1, задает тип операции: суммирование (w1=1) или вычитание (w1=0). Величина V, подаваемая на третью входную шину первого сумматора 1, задает диапазон результата суммирования/вычитания (0≤V<2k).

Первый сумматор 1 имеет первый суммирующий вход, второй вход управления, определяющий тип операции (суммирование или вычитание), третью входную шину, задающую начальное значение суммы и выход переноса.

Второй сумматор 2 работает по принципу развертывающих структур. Формирование на его выходе периода

в режиме вычитания осуществляется путем линейной развертки кода во втором сумматоре 2 от начального числа, равного сумме (Nx+), образуемой в начале периода до момента переполнения второго сумматора 2. Линейная развертка кода достигается при работе второго сумматора 2 в режиме счета, когда на его счетный вход подаются импульсы частоты Fi. В режиме суммирования второго сумматора 2 на его выходе формируется период

.

Второй сумматор 2 имеет первый суммирующий вход, второй вход управления, определяющий тип операции (суммирование или вычитание), третью входную шину, задающую начальное значение суммы и выход переноса. Второй сумматор 2 является неотъемлемой частью искусственной нейронной сети преобразователя.

Первый элемент "ИЛИ" 3 и второй элемент "ИЛИ" 4 имеют по два логических входа и одному логическому выходу.

Первый 10, второй 11, третий 12 и четвертый 13 элементы "И" имеют по два логических входа и одному логическому выходу.

Счетчик 7 имеет вход разрешения счета, группу цифровых выходов и выход переноса. С выхода переноса счетчика 7 снимается выходная частота преобразования Fy 16.

Дешифратор 8 имеет группу цифровых входов и группу цифровых выходов.

Память кодов 9 имеет группу цифровых входов и группу цифровых выходов и предназначена для промежуточного хранения цифровых коэффициентов и .

Блок памяти весовых коэффициентов 17 предназначен для хранения коэффициентов, задающих веса wi (i=1, 2), ui=(1, 2,…,m) и vi (i=1, 2,…,m) синаптических связей первого 1 и второго 2 сумматоров.

Блок памяти весовых коэффициентов 17 имеет адресную входную шину, шину данных и вход разрешения записи, а также выходы коэффициентов, задающих веса wi (i=1, 2), ui=(1, 2,….m) и vi (i=1, 2,…,m) синаптических связей первого и второго сумматоров.

Блок обучения 18 предназначен для обучения нейронной сети блока определения интервала на реализацию требуемой функции разбиения входной частоты на ее диапазоны.

Блок обучения 18 имеет вход тестовой последовательности, выходную адресную шину, выходную шину данных и выход разрешения записи.

Нейросетевой преобразователь кода в частоту содержит счетчик 7, дешифратор 8, память кодов 9, первый элемент "И" 10, второй элемент "И" 11, третий элемент "И" 12, четвертый элемент "И" 13, первый элемент задержки 5, второй элемент задержки 6, блок памяти весовых коэффициентов 17, блок обучения 18, первый сумматор 1, второй сумматор 2, первый элемент "ИЛИ" 3, второй элемент "ИЛИ" 4, первый вход цифрового кода устройства 15, второй частотный вход устройства 14, выход устройства 16, вход тестовой последовательности 19, шину SA 20 адреса весовых коэффициентов, шину SD 21 данных весовых коэффициентов, выход разрешения записи we 22. Группа цифровых выходов счетчика 7 соединена через дешифратор 8 со входами памяти кодов 9. Выходы памяти кодов 9 соединены через первый элемент "И" 10 и второй элемент "И" 11 с первыми входами первого элемента "ИЛИ" 3 и второго элемента "ИЛИ" 4 соответственно. Вторые входы первого элемента "ИЛИ" 3 и второго элемента "ИЛИ" 4 соединены через третий элемент "И" 12 и четвертый элемент "И" 13 соответственно с первым входом цифрового кода Nx устройства 15. Второй частотный вход F0 устройства 14 соединен с входом первого элемента "И" 3 и через первый элемент задержки 5 с входом третьего элемента "И" 12. Выход первого элемента "ИЛИ" 3 соединен с первым суммирующим входом первого сумматора 1. Выход первого сумматора 1 соединен со вторым входом переноса второго сумматора 2. Выход второго сумматора 2 соединен со входом второго элемента "И" 11 и через второй элемент задержки 6 со входом четвертого элемента "И" 13. Выход второго элемента "ИЛИ" 4 соединен с первым входом второго сумматора 2. Выход второго сумматора 2 соединен со входом счетчика 7, выход переноса которого одновременно является выходом устройства. Вход данных блока обучения 18 соединен со входом тестовой последовательности 19. Адресный вход блока памяти весовых коэффициентов 17 соединен с шиной SA 20 адреса весовых коэффициентов блока обучения 18. Информационный вход блока памяти весовых коэффициентов 17 соединен с шиной SD21 данных весовых коэффициентов блока обучения 18. Вход разрешения записи блока памяти весовых коэффициентов 17 соединен с выходом разрешения записи we 22 блока обучения 18. Выходы w1 и w2 блока памяти весовых коэффициентов 17 соединены со вторыми входами первого сумматора 1 и второго сумматора 2 соответственно, задающими веса режимов работы сумматоров. Первый сумматор 1 и второй сумматор 2 могут работать в режимах суммирования и вычитания. Выходы vi (i=1, 2,…,m) и ui=(1, 2,…,m) блока памяти весовых коэффициентов 17 соединены с третьими входными шинами первого сумматора 1 и второго сумматора 2 соответственно, задающими начальное значение, используемое в операциях суммирования и вычитания. Выходы si (i=1, 2,…,m) блока памяти весовых коэффициентов 17 соединены со входами памяти кодов 9.

Нейросетевой блок определения интервала работает следующим образом.

Для реализации нелинейной зависимости преобразования нейросетевой преобразователь кода в частоту должен быть обучен при помощи блока обучения 18. Обучение осуществляется при помощи подачи тестовой последовательности 19. Тестовая последовательность состоит из последовательно подаваемых значений входного кода Nx 15 и соответствующих этим значениям значений выходной частоты Fy 16. Объем тестовой последовательности влияет на точность обучения. Чем больше тестовая последовательность, тем точнее обучение устройства на реализацию зависимости выходной частоты Fy 16 от входного кода Nx 15.

Блок обучения 18 может быть реализован, например, на внешней или внутренней плате расширения персонального компьютера.

При подаче тестовой последовательности 19 на вход блока обучения 18 начинается операция обучения. По окончании операции обучения осуществляется запись новых значений весовых коэффициентов и порогов нейронов в блок памяти весовых коэффициентов 17. Для этого на вход подтверждения записи блока памяти весовых коэффициентов 17 с выхода we 22 блока обучения 18 подается значение we=1. На вход шины адреса блока памяти весовых коэффициентов 17 с выхода SA 20 блока обучения 18 подается адрес соответствующего весового коэффициента. При этом на шину данных SD 21 подается значение весового коэффициента.

На входы устройства поступает входной код Nx и опорная частота F0.

Формирование сумм Nx+ и Nx+ в первом сумматоре 1 и втором сумматоре 2 соответственно происходит при подаче импульса опорной частоты F0 и импульса переполнения второго сумматора 2. При этом код Nx подается в первый 1 и второй 2 сумматоры с некоторой задержкой τ3<Т0, длительность которой обеспечивается элементами задержки 5 и 6. Результирующая частота Fz снимается со счетчика 7.

Описываемый нейросетевой преобразователь относится к классу гибридных вычислительных устройств с дискретно-управляемыми параметрами (в том числе с использованием цифровых весовых коэффициентов искусственной нейронной сети), использующих принцип многократного использования импульсно-цифровых решающих элементов, входящих в состав операционного блока. Управление последовательностью выполнения отдельных операций производится счетчиком 7 и дешифратором 8.

Операционный блок, моделирующий в каждом i-м такте (i=1, 2,…,n) простую дробь вида (x+ai/(x+bi), состоит из последовательного соединения линейных преобразователей (Пр) "код - частота" (N→F) и "код-период" (N→T). Преобразователь "N→F" построен на основе первого сумматора 1, реализующего операцию суммирования кодов Nx и с преобразованием суммы/разности в частоту

(режим суммирования) или

(режим вычитания), представляющую собой последовательность импульсов переполнения на выходе первого сумматора 1, образуемых путем переноса на его вход кодов и Nx с частотой F0 (k - число разрядов сумматора). Первый сумматор 1 является неотъемлемой частью искусственной нейронной сети преобразователя. Весовой коэффициент w1, подаваемый на второй вход первого сумматора 1, задает тип операции: суммирование (wi=1) или вычитание (w1=0). Величина V, подаваемая на третью входную шину первого сумматора 1, задает диапазон результата суммирования/вычитания (0≤V<2k).

Пр "N→Т" построен на основе второго сумматора 2 и работает по принципу развертывающихся структур. Формирование на его выходе периода

в режиме вычитания (весовой коэффициент w2=0, а весовой коэффициент 0≤U<2k задает максимальную границу) осуществляется путем линейной развертки кода во втором сумматоре 2 от начального числа, равного сумме (Nx+), образуемой в начале периода до момента переполнения второго сумматора 2. Линейная развертка кода достигается при работе второго сумматора 2 в режиме счета, когда на его счетный вход подаются импульсы частоты Fi. Поэтому с учетом (1) выражение (3) в режиме суммирования первого сумматора 1 и вычитания второго сумматора 2 примет вид:

В момент формирования импульса окончания периода счетчик 7 изменяет свое состояние и из памяти кодов 9 подключает через элементы "И" 10, 12 или 11, 13 к элементам "ИЛИ" 3, 4 коды и .

Процесс формирования следующего периода аналогичен предыдущему. Цикл формирования одного периода Tz выходной частоты Fz равен n тактам, число которых задается коэффициентом пересчета счетчика 7. Наряду с этим счетчик 7 производит последовательное суммирование периодов , образуя на своем выходе суммарный период (в режиме суммирования первого сумматора 1 и вычитания второго сумматора 2), равный

При этом результирующая частота Fz (в режиме суммирования первого сумматора 1 и вычитания второго сумматора 2) на выходе нейросетевого преобразователя равна

Пр "N→T" на основе второго сумматора 2 в режиме суммирования второго сумматора 2 (w2=1) формирует на его выходе период:

В итоге результирующая частота Fz (в режиме вычитания первого сумматора 1 и вычитания второго сумматора 2 (w2=0)) с учетом выражений (2) и (3) на выходе нейросетевого преобразователя равна

Результирующая частота Fz (в режиме суммирования первого сумматора 1 и суммирования второго сумматора 2 (w2=1) с учетом выражений (1) и (7) на выходе нейросетевого преобразователя равна

Результирующая частота Fz (в режиме вычитания первого сумматора 1 и суммирования второго сумматора 2) с учетом выражений (2) и (7) на выходе нейросетевого преобразователя равна

Из выражения (7) следует, что нейросетевой преобразователь кода в частоту позволяет воспроизводить нелинейные зависимости, приближающиеся суммой простых дробей.

Для реализации нелинейной зависимости нейросетевой преобразователь кода в частоту должен быть обучен при помощи блока обучения 18. Обучение осуществляется при помощи подачи тестовой последовательности 19. Тестовая последовательность состоит из последовательно подаваемых значений входного кода Nx 15 и соответствующих этим значениям значений выходной частоты Fy 16. Пример тестовой последовательности приведен в таблице 1. Объем тестовой последовательности влияет на точность обучения. Чем больше тестовая последовательность, тем точнее обучение устройства на реализацию зависимости выходной частоты Fy 16 от входного кода Nx 15.

Блок обучения 18 может быть реализован, например, на внешней или внутренней плате расширения персонального компьютера.

| Таблица 1. | |

| Пример тестовой последовательности для обучения нейросетевого преобразователя кода в частоту. | |

| Значение входного кода Ny | Значение выходной частоты Fx |

| 1100 | 3,0 кГц |

| 1011 | 4,0 кГц |

| 1010 | 5,0 кГц |

| 1001 | 6,0 кГц |

| 1000 | 7,5 кГц |

| 0111 | 9,0 кГц |

| 0110 | 10,0 кГц |

| 0101 | 11,8 кГц |

| 0100 | 13,6 кГц |

| 0011 | 15,0 кГц |

| 0010 | 17,0 кГц |

| 0001 | 19,0 кГц |

| 0000 | 19,5 кГц |

При подаче тестовой последовательности 19 на вход блока обучения 18 начинается операция обучения. По окончании операции обучения осуществляется запись новых значений весовых коэффициентов и порогов нейронов в блок памяти весовых коэффициентов 17. Для этого на вход подтверждения записи блока памяти весовых коэффициентов 17 с выхода we 22 блока обучения 18 подается значение we=1. На вход шины адреса блока памяти весовых коэффициентов 17 с выхода SA 20 блока обучения 18 подается адрес соответствующего весового коэффициента. При этом на шину данных SD 21 подается значение весового коэффициента.

Таким образом, применение предлагаемого нейросетевого преобразователя кода в частоту позволяет расширить функциональные возможности, а именно реализовать функциональное преобразование входного кода в частоту, а также позволяет повысить интеллектуальные способности устройства, заключающиеся в возможности реализации одним преобразователем нескольких функциональных зависимостей.

Нейросетевой преобразователь кода в частоту, содержащий счетчик, дешифратор, память кодов, четыре элемента "И", два элемента "ИЛИ", два элемента задержки, два сумматора, группа цифровых выходов счетчика соединена через дешифратор со входами памяти кодов, выходы памяти кодов соединены через первый и второй элементы "И" с первыми входами первого и второго элементов "ИЛИ" соответственно, вторые входы первого и второго элементов "ИЛИ" соединены через третий и четвертый элементы "И" соответственно с первым входом цифрового кода устройства, второй частотный вход устройства соединен с входом первого элемента "И" и через первый элемент задержки с входом третьего элемента "И", выход первого элемента "ИЛИ" соединен с первым суммирующим входом первого сумматора, выход первого сумматора соединен со вторым входом переноса второго сумматора, выход второго сумматора соединен со входом второго элемента "И" и через второй элемент задержки со входом четвертого элемента "И", выход второго элемента "ИЛИ" соединен с первым входом второго сумматора, выход второго сумматора соединен со входом счетчика, выход переноса которого одновременно является выходом устройства, отличающийся тем, что в преобразователь введены блок памяти весовых коэффициентов и блок обучения, вход данных блока обучения соединен со входом тестовой последовательности, адресный вход блока памяти весовых коэффициентов соединен с шиной SA адреса весовых коэффициентов блока обучения, информационный вход блока памяти весовых коэффициентов соединен с шиной SD данных весовых коэффициентов блока обучения, вход разрешения записи блока памяти весовых коэффициентов соединен с выходом разрешения записи we блока обучения, выходы w1 и w2 блока памяти весовых коэффициентов соединены соответственно со вторыми входами первого и второго сумматоров, задающими режим работы сумматоров (сумматоры могут работать в режимах суммирования и вычитания), выходы vi (i=1, 2, …, m) и ui (i=1, 2, …, m) блока памяти весовых коэффициентов соединены с третьими входными шинами первого и второго сумматоров, задающими начальное значение, используемое в операциях суммирования и вычитания, выходы si (i=1, 2, …, m) блока памяти весовых коэффициентов соединены со входами памяти кодов.