Программно-управляемая логическая схема, использующая магниторезистивные устройства с передачей спинового вращения

Иллюстрации

Показать всеРаскрыты системы, схемы и способы для программно-управляемой логической схемы, использующей технологию магниторезистивной оперативной памяти с передачей спинового вращения (STT-MRAM). Запоминающие элементы на магнитном туннельном переходе могут быть сформированы в матрицы ввода и матрицы вывода. Матрицы ввода и матрицы вывода могут быть соединены вместе для формирования сложных матриц, которые обеспечивают возможность реализации логических функций. Технический результат - расширение функциональных возможностей. 3 н. и 17 з.п. ф-лы, 7 ил., 3 табл.

Реферат

Притязание на приоритет по разделу 35 Кодекса законов США §119

По настоящей заявке на патент испрашивается приоритет по дате подачи предварительной заявки № 60/908767, озаглавленной "SOFTWARE PROGRAMMABLE LOGIC USING SPIN TRANSFER TORQUE MAGNETORESISTIVE RANDOM ACCESS MEMORY", поданной 29 марта 2007 г., права на которую принадлежат заявителю этой заявки и полностью включенной в этот документ по ссылке.

Область техники, к которой относится изобретение

Варианты осуществления изобретения относятся к программируемой логической матрице (PLA) или программируемой пользователем вентильной матрице (FPGA). Более конкретно, варианты осуществления изобретения относятся к PLA, FPGA или программно-управляемой логической схеме, использующей технологию магниторезистивной оперативной памяти с передачей спинового вращения (STT-MRAM).

Предшествующий уровень техники

Программируемая в условиях эксплуатации вентильная матрица является полупроводниковым устройством, которое включает в себя компоненты программируемых логических схем, называемых "логическими блоками", и программируемые межсоединения. Логические блоки могут быть запрограммированы для выполнения функции элементарных логических вентилей, например, AND и XOR или более сложных комбинационных функций, например декодеров или простых математических функций. В большинстве матриц FPGA логические блоки также включают в себя элементы памяти, которые могут быть простыми триггерами или более полными блоками памяти. Иерархия программируемых межсоединений обеспечивает возможность соединения логических блоков так, как это необходимо специалисту по разработке систем. После того как матрица FPGA изготовлена, специалист по разработке систем может использовать программирование для реализации многих различных логических функций, тем самым конструируя "программируемое в условиях эксплуатации" устройство.

PLA аналогична FPGA, за исключением того, что PLA модифицируется, или "программируется", на этапе изготовления интегральных схем посредством изменений в одной или двух масках. Как описано в американском патенте 5959465, PLA, имеющая элементы флэш-памяти EPROM, как правило, формируется из двух логических матриц, матрицы ввода и матрицы вывода. Каждая матрица принимает входы, которые применяются к выводам затвора транзисторов в пределах логической матрицы, и обеспечивает выходы в узлы вывода. Входы матрицы ввода являются входами программируемой логической матрицы. Выходы матрицы ввода являются промежуточными узлами. Входы матрицы вывода соединены с промежуточными узлами. Выходы матрицы вывода являются выходами PLA. Матрица ввода может обеспечивать функцию AND, а матрица вывода может обеспечивать функцию OR. В качестве альтернативы, обе матрицы могут обеспечивать функцию NOR. Эти функции определяются типом и возможностью подключения используемых транзисторов и сигналами, применяемыми к их затворам. Конфигурация NOR-NOR имеет конкретные преимущества за счет того, что ее проще всего реализовать в логической CMOS-схеме. На этапах NOR существует некоторое количество транзисторов, равное количеству входов, соединенных параллельно. Подключение дополнительных параллельных транзисторов для размещения дополнительных входов не влияет на скорость функционирования этапа.

В американском патенте 6876228 описана матрица FPGA с запоминающими магнитными элементами или ячейками памяти, известная как магниторезистивная оперативная память (MRAM). Информация о соединении записывается в запоминающие магнитные элементы. Информация о соединении последовательно вводится и сохраняется в сдвиговых регистрах, которые соответствуют запоминающим магнитным элементам. Когда включают электропитание, информация о соединении, хранящаяся в запоминающих магнитных элементах, фиксируется посредством элементов-защелок и выводится в переключающие схемы для соединения логических блоков FPGA.

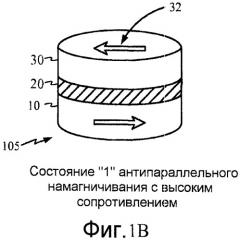

Магниторезистивная оперативная память (MRAM) является технологией энергонезависимой памяти, время отклика (чтение/запись) которой сопоставимо с энергозависимой памятью. В отличие от технологий общепринятой RAM, в которых данные хранятся как электрические заряды или электрические токи, MRAM использует магнитные элементы. Как изображено на фиг.1A и фиг.1B, запоминающий элемент 105 на магнитном туннельном переходе (MTJ) может быть сформирован из двух магнитных слоев 10 и 30, каждый из которых может удерживать магнитное поле, отделенное изолирующим (туннельный переход) слоем 20. В одном из этих двух слоев (например, закрепленном слое 10) устанавливают конкретную полярность. Полярность 32 другого слоя (например, свободного слоя 30) может свободно изменяться так, чтобы соответствовать полярности внешнего поля, которое может быть наложено. Изменение полярности 32 свободного слоя 30 изменит сопротивление запоминающего элемента 105 MTJ. Например, когда полярности ориентированы параллельно, фиг.1A, возникает состояние низкого сопротивления. Когда полярности ориентированы антипараллельно, фиг.1B, то возникает состояние высокого сопротивления. Иллюстрация MTJ 105 была упрощена, и специалистам в данной области техники будет понятно, что каждый изображенный слой может содержать один или несколько слоев материалов, как известно в данной области техники.

Сущность изобретения

Иллюстративные варианты осуществления изобретения нацелены на системы, схемы и способы для программно-управляемой логической схемы, использующей магниторезистивную технологию с передачей спинового вращения.

Вариант осуществления изобретения может включать в себя программируемую логическую матрицу, содержащую: множество устройств на магнитных туннельных переходах (MTJ) с передачей спинового вращения, организованных в матрицу, и множество программируемых источников, соединенных с соответствующими устройствами MTJ, для изменения полярности свободного слоя каждого устройства MTJ, причем первая группа устройств MTJ организована в матрицу ввода, вторая группа устройств MTJ организована в матрицу вывода, и матрица ввода и матрица вывода объединены для формирования логической функции на основе относительных полярностей свободного слоя каждого устройства MTJ.

Другой вариант осуществления может включать в себя способ реализации логической схемы в матрице, содержащий: программирование каждого из множества устройств на магнитных туннельных переходах (MTJ) с передачей спинового вращения, организованных в матрицу, в состояние высокого или низкого сопротивления, причем каждое устройство MTJ программируется первым программируемым источником, соединенным со стороной свободного слоя выбранного устройства MTJ, и программируемым источником, соединенным со стороной закрепленного слоя выбранного устройства MTJ, организацию первой группы устройств MTJ в столбцы и строки матрицы ввода, организацию второй группы устройств MTJ, по меньшей мере, в один столбец в матрице вывода, причем выходы каждой строки соединены с устройствами MTJ, по меньшей мере, в одном столбце, и определение логической функции на основе относительных сопротивлений каждого устройства MTJ.

Краткое описание чертежей

Прилагаемые чертежи представлены для лучшего описания вариантов осуществления изобретения и приведены исключительно для иллюстрации вариантов осуществления, а не для их ограничения.

Фиг.1A и фиг.1B - примеры запоминающих элементов на магнитном туннельном переходе (MTJ) и связанных с ними состояний.

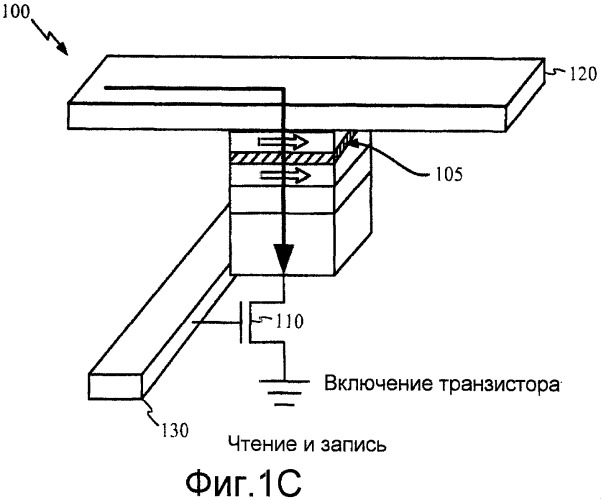

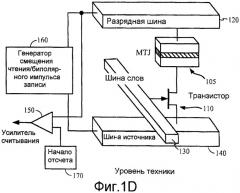

Фиг.1C и фиг.1D - примеры одноразрядных ячеек магниторезистивной оперативной памяти с передачей спинового вращения (STT-MRAM).

Фиг.2 - пример программно-управляемой логической схемы, имеющей матрицу ввода AND и матрицу вывода OR, использующей магниторезистивную технологию с передачей спинового вращения.

Фиг.3A - пример программно-управляемой логической схемы, имеющей матрицу ввода NOR и матрицу вывода NOR.

Фиг.3B - пример реализации уровня вентиля программируемой логической схемы NOR-NOR.

Фиг.4A - пример схемы строк матрицы по фиг.3, использующей магниторезистивную технологию с передачей спинового вращения.

Фиг.4B - пример эквивалентной схемы по фиг.4A.

Фиг.5 - пример программирования отдельных ячеек памяти в логической матрице.

На фиг.6A изображен пример схемы ввода для программируемой и реконфигурируемой логической матрицы, использующей магниторезистивную технологию с передачей спинового вращения.

На фиг.6B изображен пример переключаемого источника питания, используемого в схеме по фиг.6A.

Фиг.7 - график, иллюстрирующий различные уровни напряжения для сигналов для конфигурации AND.

Подробное описание

Аспекты вариантов осуществления изобретения раскрыты в следующем описании и связанных с ним чертежах, нацеленных на конкретные варианты осуществления изобретения. Могут быть разработаны альтернативные варианты осуществления, не отступая от объема изобретения. Кроме того, известные элементы изобретения не будут подробно описываться или будут опускаться, чтобы не затруднять понимание соответствующих деталей вариантов осуществления изобретения.

Слово "иллюстративный" здесь используется в значении "служащий в качестве примера, образца или иллюстрации". Любой вариант осуществления, описанный в этом описании как "иллюстративный", не должен обязательно рассматриваться как предпочтительный или имеющий преимущества перед другими вариантами осуществления. Таким же образом, термин "варианты осуществления изобретения" не требует, чтобы все варианты осуществления изобретения включали в себя рассматриваемый признак, преимущество или режим функционирования.

Варианты осуществления изобретения используют элементы магниторезистивной оперативной памяти с передачей спинового вращения (STT-MRAM), составляющих часть логической матрицы. STT-MRAM использует электроны, которые становятся спин-поляризованными, так как электроны проходят через тонкую пленку (спиновый фильтр). STT-MRAM также известна как RAM с передачей спинового вращательного момента (Spin Transfer Torque RAM, STT-RAM), RAM с переключением намагничивания и передачей спинового вращательного момента (Spin Torque Transfer Magnetization Switching RAM, Spin-RAM), RAM с передачей спинового момента (SMT-RAM). Во время операции записи спин-поляризованные электроны влияют вращающим моментом на свободный слой, который может переключать полярность свободного слоя. Операция чтения аналогична общепринятой MRAM в том смысле, что ток используется для обнаружения сопротивления/логического состояния запоминающего элемента MTJ, как обсуждалось выше.

Теперь обратимся к фиг.1C, пример одноразрядной ячейки 100 STT-MRAM изображен для лучшего понимания программирования MTJ 105. Одноразрядная ячейка 100 STT-MRAM включает в себя MTJ 105, транзистор 110, разрядную шину 120 и шину 130 слов. Транзистор 110 включают и для операции чтения, и для операции записи, чтобы обеспечивать возможность току протекать через MTJ 105 для возможности чтения или записи логического состояния. Логическое состояние MTJ 105 в STT-MRAM записывается электрически, в противоположность магнитной записи в общепринятой MRAM.

Обратимся к фиг.1D, более подробная схема ячейки 101 STT-MRAM изображена для дальнейшего обсуждения операций чтения/записи. Кроме ранее рассмотренных элементов, например, MTJ 105, изображены транзистор 110, разрядная шина 120 и шина 130 слов, шина 140 источника, усилитель 150 считывания, цепи 160 чтения/записи и начало отсчета разрядной шины 170. В отличие от MRAM, операция записи в STT-MRAM является электрической. Цепи 160 чтения/записи формируют напряжение записи между разрядной шиной 120 и шиной 140 источника. В зависимости от полярности напряжения между разрядной шиной 120 и шиной 140 источника, может быть изменена полярность свободного слоя MTJ 105, и соответственно в ячейку 101 может быть записано логическое состояние. Таким же образом, во время операции чтения, формируется ток чтения, который протекает между разрядной шиной 120 и шиной источника 140 через MTJ 105. Когда току дают возможность протекать через транзистор 110, сопротивление (логическое состояние) MTJ 105 может быть определено на основе разности напряжений между разрядной шиной 120 и шиной 140 источника, которая сравнивается с началом отсчета 170 и затем усиливается усилителем 150 считывания. Это функционирование и конструкция ячейки 101 памяти известны в данной области техники. Дополнительные подробности представлены, например, в M. Hosomi, et al., A Novel Nonvolatile Memory with Spin Transfer Torque Magnetoresistive Magnetization Switching: Spin-RAM, proceedings of IEDM conference (2005), которая полностью включена в данный документ по ссылке.

Наряду с другими аспектами, варианты осуществления изобретения имеют преимущество малой мощности, статической памяти и электрических признаков чтения-записи, рассмотренной выше технологии STT. Варианты осуществления изобретения предоставляют много признаков, в том числе: расширяемые аппаратные средства, масштабируемость посредством формирования процесса, реконфигурируемость, отсутствие инициализации, малую утечку в состоянии ожидания и сохранение программы/состояния, маленькие размеры и высокую скорость.

Например, осуществление, изображенное на фиг.2, обеспечивает реализацию сложной функции, получаемую из отдельной памяти и логических компонентов. Как изображено на фиг.2, формирование программно-управляемой функции может быть выполнено с использованием ячеек MTJ (например, 210) STT-MRAM в тандеме с CMOS-вентилями и импульсными источниками электропитания для обеспечения перезаписываемых и читаемых матриц "AND" ("И") (220) и "OR" ("ИЛИ") (240). Топология матриц AND и OR обеспечивает полную логическую конструкцию. Например, функция F0_B=X0_B+Xl_B может быть реализована (где _B обозначает дополнение данного логического сигнала), как изображено. Выход F0_B (250) принимает сигналы из отдельных запоминающих элементов MTJ 210, соединенных в матрицу 220 AND, которая соединена через управляющие элементы 230 MUX и запоминающие элементы MTJ 210 с матрицей 240 OR. Матрица 220 AND может включать в себя одну или несколько разрядных шин 222 AND, соединенных с отдельными запоминающими элементами 210 MTJ 210. Множество разрядных шин 222 AND могут быть объединены для формирования слов из произвольного количества битов. Таким же образом, матрица 240 OR может включать в себя одну или несколько разрядных шин 242 OR, соединенных с запоминающими элементами 210 MTJ, и множество разрядных шин 242 OR могут быть объединены для формирования слов из произвольного количества битов. В следующих разделах будет предоставлено более подробное описание топологии и иллюстративных конфигураций.

На фиг.3A изображена упрощенная схема структуры 300A PLA NOR-NOR. Изображенная структура может выполнять функцию Кроме того, на фиг.3B обеспечено эквивалентное представление логической схемы PLA в логических вентилях 300B. Конфигурация NOR-NOR обеспечивает операции и AND, и OR, которые должны быть реализованы. Например, иллюстрируемая функция также выполняет логическую функцию F0=Xl·X2+X3·X4. Соответственно, сложная положительная и отрицательная логика могут быть выполнены с использованием основных инверторов и вентилей или эквивалентных матриц в PLA, как обсуждалось в этом документе.

Согласно фиг.4A, логическая структура 300 NOR-NOR может быть реализована с использованием технологии STT для реализации функции F0=Xl·X2+X3·X4. Например, в структуре 300 NOR-NOR, множество STT-MTJ (например, 301, как изображено на фиг.4A) может быть соединено вместе в Строках 0 по Строку N. На входах в Строки 0-N существуют схемы 302 оценки, и схема оценки может также быть расположена на выходе логической структуры 300 (например, см. фиг.5). Каждая из схем оценки включает в себя программно-управляемый положительный/отрицательный (+/-) источник, который может быть установлен в минимальное напряжение во время операций чтения. Источник (+/-) может быть сконфигурирован для каждого состояния для операций программирования/записи в зависимости от состояния, которое будет записано в MTJ 301. Операция программирования/записи более подробно описана ниже согласно фиг.5.

Каждый из столбцов, связанных с MTJ 301, включает в себя входы, которые используются через шины X0, X0_B, Xl, Xl_B,..XN, XN_B. Существуют управляющие элементы, включенные перед входами последних ячеек 301 STT-MRAM в Строках 0-N, и инвертирующий усилитель 310 считывания на их выходе. Выход инвертирующего усилителя 310 считывания обеспечивает функцию, реализуемую каждой строкой. Соответственно, выход строки будет инвертирован (например, сигнал высокого уровня в результате станет выходным сигналом низкого уровня), что будет описано более подробно ниже.

Фиг.4A является примером функциональной иллюстрации строк логической структуры 300 NOR-NOR для операций чтения. Предположим, что входы Xl_B и X2_B (альтернативно обозначаемые как и ) являются входами, представляющими интерес в Строке 0, тогда значения сопротивления MTJ в этих строках могут быть установлены на низком уровне посредством программирования "0" или установки MTJ в состояние параллельного намагничивания. Остающиеся столбцы могут быть установлены в состояние высокого сопротивления посредством программирования "1" или установки MTJ в состояние антипараллельного намагничивания. Соответственно, логическое значение высокого уровня в одном из или в обоих X1_B и X2_B в результате приведет к логическому состоянию высокого уровня в строке 0. Будет понято, что значения, используемые в этом документе, приведены просто для примера, и могут допускаться другие конфигурации такие, что "0" является состоянием высокого сопротивления, и "1" является состоянием низкого сопротивления. Соответственно, варианты осуществления изобретения не ограничиваются иллюстративными конфигурациями или связанными с ними значениями.

Как схематично изображено, MTJ 301 могут рассматриваться как программируемые сопротивления. Сопротивления всех MTJ 301 вдоль данной строки можно фактически рассматривать как дающие в результате эквивалентное сопротивление RT, которое в комбинации с фактическим сопротивлением схемы оценки (Reval) может быть представлено как делитель 401 напряжения, на фиг.4B, который формирует напряжение Vtrip (или пусковое напряжение) в строке для данного входного напряжения на входах (например, Xl_B, X2_B и т.д.) или из эквивалентного тока из столбцов ввода. Напряжение Vtrip может иметь диапазон и для высокого уровня и для низкого уровня, в зависимости от пусковой точки инвертора 310, как изображено в (ссылочной позиции) 402. Соответственно, рассмотрение конструкции схемы включает в себя настройку пусковой точки достаточно низко так, чтобы одно логическое состояние высокого уровня на активном входе (например, Xl_B или X2_B) было обнаружено как высокий уровень и вызывало переход выхода инвертирующего усилителя 310 считывания на низкий уровень. Соответственно, пусковая точка может быть настроена так, что любой ток утечки из неиспользуемых входов (например, X3, X4 и т.д.) не вызывает активизацию ложного состояния положительной логики. Так как комплементарные входы Xl и X2 используются в определении состояния Строки 0 (например, значение Vtrip), которая является входом в инвертирующий усилитель 310 считывания, выходом инвертирующего усилителя 310 считывания является функция или Xl·X2. Таким же образом, могут быть реализованы другие функции для других строк и эти логические функции могут быть объединены в более сложные логические функции. Будет понято, что, так как и входы, выходы и их соответствующие дополнения (например, X0 и ) доступны, то различные требуемые функции могут быть подвергнуты преобразованию де Моргана для их выполнения посредством различных логических матриц (например, матрицы AND, матрицы OR, матрицы NOR). Кроме того, так как MTJ 301 могут быть запрограммированы или в высокое, или в низкое сопротивление, то функциональную логику каждой матрицы можно реконфигурировать.

Согласно фиг.5, приведен пример программирования отдельных MTJ 210. Как обсуждалось выше, MTJ 210 могут быть "запрограммированы" или в состояние относительно высокого сопротивления или в состояние относительно низкого сопротивления посредством установки MTJ 210 в антипараллельное или параллельное состояние намагниченности, соответственно. Соответственно, в целях примера, состояние высокого сопротивления будет представлено как логическое состояние 1, и состояние низкого сопротивления будет представлено как логическое состояние 0. Программируемая матрица по фиг.5 аналогична матрице, изображенной на фиг.2, поэтому будут использоваться подобные ссылочные позиции, и не будет подробного обсуждения элементов. Как изображено, каждый MTJ 210 может быть запрограммирован посредством установки пути записи (например, 510) между программно-управляемым положительным/отрицательным (+/-) источниками 512 и 514. В частности, ток записи можно получать между источниками питания 512 и 514 при установке оставшихся логических путей (например, от к ) в состояние высокого импеданса и установки источников питания 512 и 514 в требуемую полярность для записи состояния "1" или "0" в выбранный MTJ 210. Будет понято, что этот процесс программирования можно повторить для всех MTJ в матрице 220 AND.

Таким же образом, MTJ 210 вдоль пути 520 записи может быть запрограммирован посредством источников 522 и 524 (+/-). В частности, ток записи можно формировать между источниками питания 522 и 524 при установке оставшихся логических путей в матрице 240 OR в состояние высокого импеданса и установке источников питания 522 и 524 (+/-) в требуемую полярность для записи состояния "1" или "0" (например, в состояние высокого сопротивления или низкого сопротивления) в выбранный MTJ. Как изображено, часть (например, (a)) управляющего элемента 230 MUX может быть активирована для обеспечения возможности операций записи, и часть чтения (например, (b)) можно устанавливать в состояние высокого импеданса во время операций записи. Будет понято, что часть (a) записи по ссылочной позиции 230 может обеспечивать возможность двунаправленного потока электрического тока так, что оба состояния могут быть запрограммированы в выбранном MTJ. Также будет понято, что функциональные возможности управляющего элемента 230 MUX могут быть реализованы как независимые устройства, и варианты осуществления изобретения не ограничиваются изображенными устройствами или топологией. Соответственно, любое устройство или комбинацию устройств, которые могут получить рассмотренные выше функциональные возможности, можно использовать вместо управляющего элемента 230 MUX.

На фиг.6A изображен пример схемы ввода для программируемой логической схемы STT. Как изображено, входы A и B могут быть обеспечены в логические пути 610, 620, 630 и 640 для обеспечения результатов для входа и A, и B, и их дополнений и В иллюстрированном примере вход A обеспечивается в транзисторы 614 PMOS и инвертируется инвертором 622, и обеспечивается в транзистор 614 PMOS через вентили 618 и 628 NAND, соответственно. Таким же образом, вход B обеспечивается в транзисторы 634 PMOS и инвертируется инвертором 642, и обеспечивается в транзистор 644 PMOS через вентили 638 и 648 NAND, соответственно.

Вентили 618, 628, 638 и 648 NAND также принимают входы из сигнала READ. Соответственно, функция вентилей NAND для установки логических путей 610, 620, 630 и 640 чтения в состояние высокого импеданса, когда операция чтения не является активной. Это обеспечивает возможность независимого программирования MTJ 611, 621, 631, 641, например, как обсуждалось в отношении фиг.5. Однако, будет понято, что конфигурация вентиля NAND предоставлена только как пример, и можно использовать любое подходящее устройство для получения аналогичных функциональных возможностей.

Соответственно, когда вход A имеет высокий уровень напряжения, и сигнал READ (чтение) является высоким, транзистор 614 PMOS будет активизирован. Как отмечено выше, вход A также обеспечивается посредством инвертора 622 в транзистор 624 PMOS, который активизируется в противоположном логическом состоянии пути ссылочной позиции 610 (например, активизируется при низком напряжении входа A) так, что обеспечивается дополнение к входу A. Таким же образом, когда сигнал READ является высоким, вход B обеспечивается в транзистор 634 PMOS и также обеспечивается посредством инвертора 642 в транзистор 644 PMOS для обеспечения и B, и его дополнения в пути 630 и 640, соответственно.

Как отмечено выше, логическое состояние "1" или "0" (например, состояние высокого или низкого сопротивления) магниторезистивных устройств STT (STT MTJ или MTJ) может быть запрограммировано в каждом STT MTJ (например, 611, 621, 631, 641) с использованием связанных программно-управляемых положительных/отрицательных (+/-) источников 680 и 688, как обсуждалось выше. Эта возможность программирования обеспечивает реконфигурируемую логическую матрицу в отношении логических функций каждой матрицы, как будет рассмотрено более подробно ниже. Кроме того, как отмечено выше, во время операций программирования, путь чтения устанавливается в состояние высокого импеданса для обеспечения возможности выбора и программирования каждого MTJ. На фиг.6B изображен пример источников 680 (+/-). Как изображено, программируемый источник электропитания 682 может быть соединен со схемой 684 Оценка (Eval), которая также обеспечивает возможность отдельного включения или отключения программируемого источника 680 питания. Схема 684 Оценка может быть таким устройством CMOS, как передаточный вентиль или любое другое устройство, которое обеспечивает возможность отдельного соединения источника 682 питания. Активизацией схемы 684 Оценка можно управлять посредством сигнала WRITE X, где X является столбцом, который записывают, так как каждый программируемый источник 680 может быть соединен со столбцом одной или нескольких ячеек MTJ (см., например, фиг.5). Программируемый источник 688 можно конфигурировать аналогично, как изображено на фиг.6B, однако схема Оценка будет активизирована на операциях и чтения, и записи для каждой выбранной строки. Во время операции чтения источник питания 682 устанавливается в низкое напряжение (которое может быть землей или отрицательным напряжением), поэтому результирующая схема аналогична примеру чтения по фиг.4A и фиг.4B. В качестве альтернативы, программируемый источник 688 может иметь отдельные схемы для чтения и записи. Например, часть записи можно конфигурировать, как изображено на фиг.6B, и часть чтения может иметь схему Оценка, непосредственно соединенную с землей и управляемую сигналом READ (чтение). Соответственно, будет понято, что вышеизложенные примеры схем приведены только с целью примера, и нет намерения ограничивать объем вариантов осуществления изобретения.

При анализе топологии программируемой логической матрицы, например, изображенной на фиг.5, будет понято, что аналогичные логические конфигурации можно использовать для матрицы вывода (например, 240), где каждый MTJ в матрице вывода может быть запрограммирован или в низкое, или в высокое сопротивление, и выход каждой строки может быть обеспечен как вход в каждый соответствующий MTJ. Таким же образом, программируемые источники могут быть аналогичными для программирования каждого из MTJ в матрице вывода, и часть записи MUX (например, 230) может использоваться для выбора каждого MTJ, в который будет осуществляться запись. В качестве альтернативы, отдельные программируемые источники могут быть обеспечены для каждого выхода MTJ, и соответствующий MUX может быть упрощен для обеспечения только функции чтения. Во время операции чтения результат сигналов из MTJ в матрице вывода может быть считан усилителем считывания (например, 250) и установлен в логические или 1, или 0 на основе порога, как обсуждалось выше, в отношении операции чтения для каждой строки.

Для лучшего понимания функционирования различных логических конфигураций ниже представлена таблица истинности для входа А для данного состояния связанных MTJ 611 и 621. А именно, как изображено, когда вход A находится в состоянии (1) высокого уровня, значения в обоих узлах al и a2 равны логическому 0. Соответственно, выход F будет логическим 0, и дополнение F будет логической 1. Напротив, когда вход A находится в логическом 0, значение в узле al остается 0, но значение в узле a2 равно логической 1, в результате чего выход F будет логической 1, а дополнение F будет логическим 0.

| Таблица 1 | ||||

| Логическая таблица истинности STT | ||||

| Вход А | Состояние MTJ | Узел(a1, a2) | Выход(F) | Выход(F_B) |

| 1 | 1 | 0(a1) | 0 | 1 |

| 0 | 0(a2) | |||

| 0 | 1 | 0(a1) | 1 | 0 |

| 0 | 1(a2) |

Как изображено, F обеспечивается посредством промежуточного преобразования напряжения в Сигнале посредством усилителя 650 считывания, который функционирует для переключения с высокого уровня на низкий уровень после достижения заданного порога или пускового/порогового уровня (например, Vtrip). Таким же образом, дополнение F обеспечивается из выхода инвертора 652. Однако, будет понято, что варианты осуществления изобретения не ограничиваются этой конфигурацией. Например, усилитель считывания может иметь инвертированный выход, и затем быть соединен последовательно с другим инвертором, который может использоваться для обеспечения инвертированной логики относительно напряжения в Сигнале и дополнения инвертированной логики. Также будет понято, что использование логических значений, например 0, не подразумевает, что в узле al или a2 нулевое напряжение, а только означает, что уровень напряжения в Сигнале не является достаточным для запуска логической 1, как считано в выходе F. В целях этого объяснения, предполагается, что пути 630 и 640 находятся в состоянии высокого импеданса и не вносят вклад в напряжение в Сигнале. Влияние различных логических уровней обсуждается более подробно ниже, согласно фиг.7.

На фиг.7 изображены результаты моделирований для логической конфигурации, например, изображенной на фиг.6. На графиках изображены соответствующие уровни напряжения для входов A и B, и можно считать, что они имеют четыре квадранта, которые отображают в четыре двоичные комбинации состояния входов (например, 10, 11, 01, 00). Кроме того, можно устанавливать значение 732 пороговой/пусковой точки для определения окончательного состояния выхода этой строки матрицы (см., например, фиг.4B), на основе напряжения 730 в Сигнале строки, обеспечивающей (информацию) в усилитель считывания. Построен график выходного напряжения 740 для изображения логики, функционирующей для различных состояний входа. Следует отметить, что предполагается, что усилитель считывания для выходного напряжения 740 является инвертированным выходом для изображенного графика. Например, если напряжение 730 в Сигнале ниже напряжения 732 пороговой точки, то выходное напряжение 740 является высоким. Таким же образом, если напряжение 730 в Сигнале выше напряжения 732 пороговой точки, то выходное напряжение 740 является низким.

Когда вход A является высоким, и вход B является низким, все еще будет существовать путь утечки через устройства MTJ STT, и напряжение в Сигнале 730 повысится до определенного уровня, как указано в первом квадранте графика по фиг.7. Это значение Сигнала по существу повторяется в третьем квадранте, где вход A является низким, и вход B является высоким. Самый низкий уровень напряжения для Сигнала 730 имеет место во втором квадранте, когда оба входа A и B являются высокими. Из-за конфигурации логической матрицы, например, изображенной на фиг.6A, когда оба входа A и B являются высокими, они соединены с путями высокого сопротивления через устройства 611 и 613 STT соответственно. Напротив, когда и A, и B являются низкими в четвертом квадранте, имеет место самый высокий уровень напряжения для Сигнала 730, потому что оба пути 620 и 640 будут активными, которые имеют MTJ 621 и 641, установленные в состояние низкого сопротивления. Соответственно, Сигнал 730 больше, чем пороговая точка 732, и выход 740 является низким для этого состояния. Будет понято, что график для неинвертированного выхода в результате приводит к графику выхода, имеющему противоположное состояние. Представление таблицы истинности приведено ниже, в Таблице 2, для графика по фиг.7.

| Таблица 2 | ||

| Вход А | Вход В | Выход |

| 1 | 0 | 0 |

| 1 | 1 | 1 |

| 0 | 1 | 0 |

| 0 | 0 | 0 |

Как обсуждалось выше, также будет понято, что логические матрицы можно реконфигурировать посредством перепрограммирования значений MTJ. Например, если значения MTJ 611, 621, 631 и 641 инвертируются, то логика, реализуемая строкой, изображенной на фиг.6A, может быть изменена на функцию OR. Например, если MTJ 611 и 631 запрограммированы в '0' или состояние низкого сопротивления, то напряжение в Сигнале будет в повышенном состоянии, когда вход или A, или B является высоким, и в его самом высоком состоянии, когда оба (входа) являются высокими. Напряжение будет находиться в своем самом низком состоянии, когда оба входа A и B являются низкими. Соответственно, выход строки может реализовать функцию OR, как иллюстрируется в таблице истинности, представленной ниже, в Таблице 3.

| Таблица 3 | ||

| Вход А | Вход В | Выход |

| 1 | 0 | 1 |

| 1 | 1 | 1 |

| 0 | 1 | 1 |

| 0 | 0 | 0 |

Соответственно, будет понято, что варианты осуществления изобретения включают в себя и программируемые, и реконфигурируемые аспекты с использованием устройств MTJ STT в логической матрице. Далее, будет понято, что варианты осуществления изобретения не ограничиваются изображенными конфигурациями. Варианты осуществления изобретения могут быть программно-управляемыми через топологию и компоновки и включать в себя программируемые функции декодирования, расширяемые наборы команд и оперативное добавление аппаратной логики/манипуляцию ею посредством программирования, реализуемого программно. Кроме того, варианты осуществления изобретения могут включать в себя конструкции, которые выполняются параллельно без требования тактового генератора для синхронизации передачи данных. Соответственно, с использованием устройств MTJ STT, матрицы ввода и матрицы вывода и связанные с ними управляющие элементы как стандартные блоки, варианты осуществления изобретения могут быть выполнены с возможностью получения сложных функциональных возможностей.

Несмотря на то, что в вышеизложенном раскрытии представлены иллюстративные варианты осуществления изобретения, следует отметить, что в этом документе могут быть сделаны различные изменения и модификации, не отступая от объема вариантов осуществления изобретения, определяемых прилагаемой формулой изобретения. Нет необходимости выполнять функции, этапы и/или действия способов в соответствии с вариантами осуществления изобретения, описанными в этом документе, в каком-либо конкретном порядке. Кроме того, хотя элементы изобретения могут быть описаны или заявлены в единственном числе, предполагается множественное число, если только явно не заявлено ограничение до единственного числа.

1. Программируемая логическая матрица, содержащая:множество устройств на магнитных туннельных переходах (MTJ) с передачей спинового вращения, организованных в матрицу, имножество программируемых источников, соединенных с соответствующими устройствами MTJ, для изменения полярности свободного слоя каждого устройства MTJ,причем первая группа устройств MTJ организована в матрицу ввода,причем вторая группа устройств MTJ организована в матрицу вывода ипричем матрица ввода и матрица вывода объединены для формирования логической функции на основе относительных полярностей свободного слоя каждого устройства MTJ; иусилитель считывания выхода, соединенный с матрицей вывода, выполненный с возможностью обнаруживать уровень сигнала в столбце матрицы вывода и формировать двоичный выходной сигнал на основе сравнения уровня сигнала в столбце матрицы вывода с пороговым уровнем сигнала.

2. Программируемая логическая матрица по п.1, в которой каждое устройство MTJ содержит запоминающий элемент на магнитном туннельном переходе (MTJ), который может