Персональный компьютер

Иллюстрации

Показать всеИзобретение относится к вычислительной технике и может быть использовано при изготовлении персональных компьютеров. Техническим результатом является снижение энергоемкости радиопередающего и приемного устройств, а также осуществление формирования изображения на экране монитора без разверток, осуществление режима стереоизображения. Устройство содержит первое радиопередающее устройство, содержащее формирователь кодов, синтезатор частот, передатчик радиосигналов, распределители импульсов, шесть кодеров, радиоприемное устройство, имеющее канал приема радиосигналов, канал формирования управляющих сигналов, два канала обработки кодов кадров стереопар, каждый из которых содержит приемный регистр, три декодера, три блока удвоения отсчетов, три накопителя кодов кадра, три импульсных усилителя, а также правый и левый плоскопанельные экраны и очки раздельного поля зрения. 18 ил., 1 табл.

Реферат

Изобретение относится к персональным компьютерам /ПК/ и выполняет его функции.

Прототипом принят "Персональный компьютер" [1], содержащий системный блок, цифровой монитор, первое радиопередающее устройство в корпусе системного блока и первое радиоприемное устройство в корпусе цифрового монитора, устройство ввода в составе второго радиопередающего устройства на корпусе клавиатуры, мыши и второго радиоприемного устройства на системном блоке ПК и содержащий устройство ввода модем. Недостатки прототипа: передача видеоинформации по двум радиоканалам первым радиопередающим устройством и прием ее двумя радиоканалами в первом радиоприемном устройстве увеличивает энергоемкость и всего ПК, построение изображения разверткой строк и построчной разверткой кадра снижает качество и яркость изображения на экране, отсутствует режим стереоизображений, необходимый для каждого домашнего ПК.

Цель изобретения - снижение энергоемкости первых радиопередающего и приемного устройств, построение изображения кадра без использования разверток строк и кадра, воспроизведение устройством отображения стереовидеоинформации.

Техническими результатами являются снижение энергоемкости первых радиопередающего и приемного устройств передачей и приемом видеоинформации по одному каналу, воспроизведение изображения на экране без разверток, осуществление режима стереоизображения, выполняемого двухэкранным способом, дающим наилучшие результаты [2, с.540], с применением очков раздельного поля зрения.

Сущность изобретения в том, что в первое радиопередающее устройство ПК вводятся шесть кодеров, передатчик радиосигналов выполняется одноканальным, в радиоприемном устройстве имеется один канал приема радиосигналов и в него вводятся канал обработки кодов правых кадров стереопар и канал обработки кодов левых кадров стереопар, правый и левый плоскопанельные экраны и очки раздельного поля зрения.

Первое радиопередающее и первое радиоприемное устройства работают в двух режимах: первый - передача и прием параллельно правого и левого стереокадров с видеоадаптера ПК, второй - передача и прием обычных монокадров с видеоадаптера ПК. На передающей стороне с видеоадаптера ПК предлагается видеорежим 1000строк×800отсчетов×25 Гц: 1000 - число строк в кадре, 800 - число кодируемых отсчетов в строке, 25 Гц - частота стереопар /параллельно передаются правый и левый кадры стереопар/. Число отсчетов 800 применяется для снижения тактовой частоты на передающей стороне, на приемной стороне число отсчетов в строке удваивается /800×2/ и становится 1600. Правый и левый кадры воспроизводятся синхронно на двух, расположенных рядом, правом и левом экранах /два глаза - два экрана/, изображения с которых воспринимаются пользователем через очки раздельного поля зрения. Частота дискретизации кодов цветовых сигналов правого кадра R, G, В и левого кадра R2, G2, B2, выдаваемых с соответствующих выходов видеоадаптера ПК, составляет: fд=1000×800×25 Гц=20 МГц. В цифровом представлении изображения всегда присутствуют много идущих последовательно кодов, равных по величине. За счет таких кодов есть смысл выполнить сжатие потока кодов каждого цветового сигнала отдельно. В кодере идущие последовательно равные по величине коды подсчитываются и на выходе кодера первым кодом идет первый код последовательности одинаковых кодов, за ним /вторым/ идет код подсчитанного числа равных кодов. Для 100% восстановления сжатого потока кодов коэффициент сжатия за кадр принимается небольшим, равным 4. При сжатии потока кодов кадра используется плавающий коэффициент сжатия от 1 до 255 /11111111/. При коэффициенте сжатия 4 частота дискретизации с выхода кодеров будет 5 МГц //.

Частота тактовых синусоидальных колебаний, используемых в формирователе кодов передающей стороны, составляет: fт=5 МГц×27=135 МГц. 5 МГц - частота дискретизации кодов на выходе кодера.

27 - число разрядов в суммарном коде, состоящем из трех девятиразрядных кодов цветовых сигналов R, G, В, 9×3=27.

Период следования кодов 200 нс //, период одного разряда в коде 7,4 нс //. Несущая частота принимается:

fн=135 МГц×15=2025 МГц. Верхняя боковая частота амплитудно модулированной несущей fНВ=2025 МГц+135 МГц=2160 МГц, нижняя боковая частота fНН=2025 МГц-135 МГц=1890 МГц. Для передачи видеоинформации принимается нижняя боковая частота несущей 1890 МГц. Входными сигналами для передающей стороны являются восьмиразрядные коды цветовых сигналов правого кадра стереопары R, G, В и коды цветовых сигналов левого кадра стереопары R2, G2, B2 с видеоадаптера ПК в формате стереокадра, т.е. поступающие с него параллельно на входы шести кодеров [2, с.542, строка снизу], предлагаемого здесь видеорежима 1000×800×25 Гц. С передатчика радиосигналов коды правого и левого кадров стереопар параллельно передаются на приемную сторону, где сжатая видеоинформация восстанавливается на 100% декодерами, удваивается число отсчетов в строке с 800 до 1600 и на двух экранах параллельно и синхронно воспроизводятся правый и левый кадры стереопары, видеорежим 1000×1600×25 Гц, разрешение кадра 1,6×106 пикселов. Объемное изображение зритель принимает через очки раздельного поля зрения.

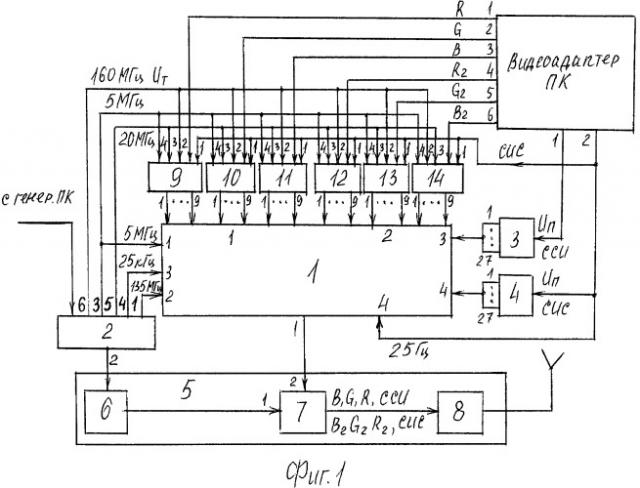

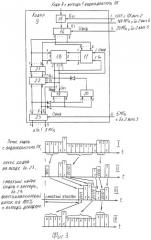

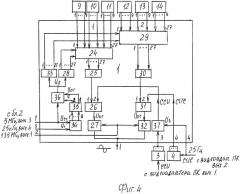

Функциональная схема первого радиопередающего устройства - на фиг.1, структура цифрового потока - на фиг.2, кодер - на фиг.3, формирователь кодов - на фиг.4, спектр амплитудно-модулированного сигнала - на фиг.5, первое радиоприемное устройство - на фиг.6, декодер - на фиг.7, двухполярный амплитудный детектор - на фиг.8, блок удвоения отсчетов - на фиг.9, накопитель кодов кадра - на фиг.10, блок регистров - на фиг.11, 12, общий вид элемента матрицы - на фиг.13, ячейка - на фиг.14, перекрытие потока излучения в диафрагме - на фиг.15, расположение элементов матриц в экране - на фиг.16, временные диаграммы работы - на фиг.17, блок выделения ССИ /СИС/ - на фиг.18.

Первое радиопередающее устройство /фиг.1/ расположено в системном блоке ПК и включает формирователь 1 кодов, синтезатор 2 частот, первый самоходный распределитель 3 импульсов /СРИ/ [3, с.269, 274], второй СРИ 4 и передатчик 5 радиосигналов из одного канала, содержащий усилитель 6 несущей частоты, амплитудный модулятор 7 и выходной усилитель 8, включает с первого 9 по третий 11 кодеры сигналов R, G, В и с четвертого 12 по шестой 14 кодеры сигналов R2, G2, B2. Амплитудный модулятор 7 состоит из последовательно соединенных кольцевого модулятора и полосового фильтра [4, с.234, 235], отфильтровывающего верхнюю боковую частоту 2160 МГц /фиг.5/. Сжатие потока кодов каждого цветового сигнала выполняется своим кодером 9-14, средний коэффициент сжатия в периоде кадра не ниже 4. Кодеры идентичны, каждый содержит /фиг.3/ последовательно соединенные ключ 15, первый восьмиразрядный регистр 16, второй восьмиразрядный регистр 17, схему сравнения /компаратор/ 18, восьмиразрядный счетчик 19 импульсов и дешифратор 20, последовательно соединенные блок 21 элементов задержек из восьми элементов, блок 22 ключей из восьми ключей и буферный накопитель 23 кодов кадра с объемом 200×103 /200отсч×1000строк/ девятиразрядных кодов. Информационным входом /с видеоадаптера ПК/ является сигнальный вход ключа 15, подключенный к соответствующему выходу /1-6/ видеоадаптера ПК /фиг.1/. Выходами кодера являются первый-девятый выходы буферного накопителя 23 кодов кадра. Первый-восьмой выходы первого регистра подключены параллельно к первому-восьмому входам блока элементов задержек и первому-восьмому входам первого входа схемы 18 сравнения, первый выход которой подключен к счетному входу счетчика 19 импульсов, к второму управляющему Uз входу блока 22 ключей и к первому управляющему Uвыд входу второго регистра 17, второй и третий выходы схемы 18 сравнения объединены и подключены параллельно к второму управляющему Uo входу второго регистра 17, к первому управляющему Uот входу блока 22 ключей, к первому управляющему входу Uвыд счетчика 19 импульсов и к входу девятого разряда буферного накопителя 23 кодов кадра. Выходы счетчика 19 импульсов подключены к входу дешифратора 20 и через диоды - к входам первого-восьмого разрядов буферного накопителя 23 кодов кадра, а выход дешифратора 20 через диод подключен к первому управляющему Uот входу блока 22 ключей, к первому управляющему входу Uвыд счетчика 19 импульсов и к входу девятого разряда буферного накопителя 23 кодов кадра. Управляющими входами кодера 9 являются: первым - первый управляющий Uот вход ключа 15, подключенный к входу второго СРИ 4, вторым - тактовый вход Uт 160 МГц первого регистра 16, подключенный к шестому выходу синтезатора 2 частот, третьим - управляющий вход Uвыд /20 МГц/ первого регистра, подключенный к пятому выходу синтезатора 2 частот, четвертым - управляющий вход Uвыд /5 МГц/ буферного накопителя 23 кодов кадра, подключенный к третьему выходу синтезатора 2 частот. Формирователь 1 кодов /фиг.4/ включает два идентичных канала, первый включает последовательно соединенные первый блок 24 элементов И из 27 элементов, первые входы которых являются первым информационным входом формирователя 1 кодов, первый 25, второй 26 элементы ИЛИ, первый выходной ключ 27, первый самоходный распределитель 28 импульсов /СРИ/, двадцать семь выходов которого подключены к вторым входам блока 24 элементов И, второй канал включает второй блок 29 элементов И, которых 27 штук и первые входы которых являются вторым информационным входом формирователя 1 кодов, третий 30 и четвертый 31 элементы ИЛИ, второй выходной ключ 32 и второй СРИ 33, двадцать семь выходов которого подключены к вторым входам элементов И в блоке 29. Формирователь 1 кодов содержит восьмиразрядный счетчик 34 импульсов и дешифратор 35, первый ключ 36 и второй ключ 37, сигнальный вход которого является третьим информационным входом формирователя кодов, четвертым информационным входом которого является второй вход четвертого элемента ИЛИ 31. Выход второго ключа 37 подключен к второму входу элемента ИЛИ 26. Выход первого ключа 36 подключен к входам СРИ 33, 28, первый выход дешифратора 35 подключен к первому управляющему входу Uот ключа 36, к второму управляющему Uз входу которого подключен второй выход дешифратора 35. Управляющими входами формирователя 1 кодов являются: первым - объединенные входы 5 МГц ключа 36 и счетный вход счетчика 34 импульсов, вторым - объединенные сигнальные входы 135 МГц обоих выходных ключей 27, 32, третьим - управляющий вход /25 кГц/ Uо счетчика 34 импульсов, четвертым - управляющий вход Uз /25 Гц/ ключа 37. Выходом формирователя 1 кодов являются объединенные выходы выходных ключей 27, 32, подключенные к второму входу амплитудного модулятора 7 /фиг.1/. Вход синтезатора 2 частот подключен к соответствующему выходу тактового генератора ПК, а выходы его подключены: первый 135 МГц к второму управляющему входу формирователя 1 кодов, второй - синусоидальные колебания несущей частоты 2025 МГц к входу усилителя несущей частоты 6, третий - 5 МГц подключен параллельно к первому управляющему входу формирователя 1 кодов и к четвертым управляющим входам кодеров 9-14, четвертый - к третьему управляющему входу 25 кГц формирователя 1 кодов, пятый подключен параллельно к третьим управляющим входам кодеров 9-14 /20 МГц/, шестой подключен параллельно к вторым управляющим входам /160 МГц/ кодеров 9-14. Первое радиоприемное устройство расположено на тыльной стороне корпуса правого плоскопанельного экрана 48, включает блок 38 выбора канала передачи, один канал приема радиосигналов, канал обработки кодов правых кадров стереопар, канал обработки кодов левых кадров стереопар, первый /правый/ 48 и второй /левый/ 55 плоскопанельные экраны, очки раздельного поля зрения и канал формирования управляющих сигналов. Канал приема радиосигналов из последовательно соединенных блока 39 приема радиосигналов, усилителя 40 радиочастоты и двухполярного амплитудного детектора 41, выполненного по принципиальной схеме на фиг.8, включает первый формирователь 42 импульсов, вход которого подключен к первому выходу двухполярного амплитудного детектора 41, второй формирователь 49 импульсов, вход которого подключен к второму выходу двухполярного амплитудного детектора 41, первый вход блока приема радиосигналов подключен к антенне, вторые входы подключены к первой группе выходов блока выбора канала передачи. Канал обработки кодов правых кадров стереопар включает первый приемный регистр 43 из двадцати семи разрядов и три канала сигналов R, G, В, которые идентичны и каждый содержит последовательно соединенные декодер 44, блок 45 удвоения отсчетов, накопитель 46 кодов кадра и блок 47 импульсных усилителей, содержащий импульсных усилителей по числу отсчетов в строке, числу разрядов в коде и числу строк в кадре 12,8×106/1600×8×1000/.

Информационный вход первого приемного регистра подключен к выходу первого формирователя 42 импульсов, выходы разрядов первого приемного регистра подключены: выходы первого-девятого разрядов к первому-девятому входам декодера канала сигнала R, десятого-восемнадцатого разрядов к первому-девятому входам декодера 44 канала сигнала G, девятнадцатого-двадцать седьмого разрядов к первому-девятому входам декодера 44 канала сигнала В. Выходы трех блоков 47 импульсных усилителей подключены к соответствующим входам правого плоскопанельного экрана. Канал обработки кодов левых кадров стереопар размещается на тыльной стороне корпуса левого плоскопанельного экрана и включает второй приемный регистр 50 из двадцати семи разрядов, информационный вход его соединен по соответствующему кабелю с выходом второго формирователя 49 импульсов, расположенного на корпусе правого плоскопанельного экрана, и включает три канала сигналов R2, G2, B2, которые идентичны и каждый включает последовательно соединенные декодер 51, блок 52 удвоения отсчетов, накопитель 53 кодов кадра и блок 54 импульсных усилителей, содержащий каждый импульсных усилителей по числу отсчетов в строке, числу разрядов в коде и числу строк в кадре 12,8·106. Выходы разрядов второго приемного регистра 50 подключены: выходы первого-девятого разрядов к первому-девятому входам декодера 51 канала сигнала R2, десятого-восемнадцатого разрядов к первому-девятому входам декодера 51 канала сигнала G2, девятнадцатого-двадцать седьмого разрядов к первому-девятому входам декодера канала сигнала B2. Выходы трех блоков 54 импульсных усилителей подключены к соответствующим входам левого плоскопанельного экрана 55.

Канал формирования управляющих сигналов содержит последовательно соединенные блок 56 выделения строчного синхроимпульса /ССИ/ и синтезатор 57 частот, блок 58 выделения синхроимпульсов стереопар /СИС/. Первый вход блока 56 выделения ССИ подключен к выходу первого формирователя 42 импульсов, управляющий его вход подключен к выходу второго формирователя 49 импульсов, первый вход блока 58 выделения СИС подключен к выходу второго формирователя 49 импульсов, второй управляющий вход подключен к выходу первого формирователя 42 импульсов. Синтезатор 57 частот выдает: с первого выхода тактовые импульсы 135 МГц, который подключен к тактовым входам первого 43 и второго 50 приемных регистров, со второго выхода импульсы Uвыд 5 МГц, выход подключен к вторым управляющим входам первого и второго приемных регистров 43, 50, с третьего выхода импульсы частоты дискретизации 20 МГц, выход подключен к объединенным вторым управляющим входам декодеров и к объединенным входам блоков удвоения отсчетов в обоих каналах обработки кодов правых и левых кадров стереопар, с четвертого выхода импульсы двойной частоты дискретизации кодов /40 МГц/, выход подключен к объединенным третьим управляющим входам накопителей 46, 53 кодов кадра в обоих каналах обработки кодов правых и левых кадров стереопар. Объединенные первые управляющие входы всех накопителей 46, 53 кодов кадра подключены к выходу блока 58 выделения синхроимпульсов СИС, объединенные вторые управляющие входы всех накопителей 46, 53 кодов кадра подключены к выходу блока 56 выделения строчных синхроимпульсов /ССИ/. Управляющие входы второго приемного регистра 50, декодеров 51, блоков 52 удвоения отсчетов и накопителей 53 кодов кадра каналов сигналов R2, G2, B2 подключены к выходам синтезатора 57 частот, блока 56 выделения ССИ и блока 58 выделения СИС по соответствующему кабелю соответствующей длины.

Очки 59 раздельного поля зрения /фиг.6/ представляют оправу с дужками для ушей, окна очков стекол не имеют, между собой соединены подвижно вертикальной осью для поворота относительно друг друга в горизонтальной плоскости, для разделения поля зрения глаз каждое очко имеет конусную бленду на конце прямоугольной формы. Бленда из двух частей: первая часть вкручивается в очко, вторая часть подвижная, может вдвигаться в первую или выдвигаться из нее, изменяя длину бленды. Для просмотра стереопрограммы экраны 48, 55 ставятся на небольшом расстоянии друг от друга, зритель на расстоянии 2-3 метров от них и посреди. Разворотом очков и выдвижением /или вдвижением/ второй части бленды пользователь настраивает разделение полей зрения глаз так, чтобы левый глаз видел только левый экран, правый глаз видел только правый экран. При смене места потребуется небольшая подстройка полей зрения. Для людей, постоянно пользующихся очками в обычной жизни, - в аптеке "Оптика" вставить нужные им стекла.

Декодеры 44, 51 идентичны, каждый включает /фиг.7/ последовательно соединенные первый девятиразрядный регистр 60, накопитель 61 кодов кадра емкостью 200·103 девятиразрядных кодов /200отсч×1000стр/, второй девятиразрядный регистр 62, первый блок 63 ключей из восьми ключей и третий восьмиразрядный регистр 64, последовательно соединенные второй блок 65 ключей из восьми ключей, восьмиразрядный вычитающий счетчик 66 импульсов и дешифратор 67, первый 68, второй 69, третий 70 и четвертый 71 ключи. Информационным входом декодера 44 являются диоды первого-девятого разрядов первого регистра 60, выходом являются первый-восьмой выходы третьего регистра 64. Управляющими входами декодера являются: первым - объединенные управляющий вход Uвыд регистра 60 и сигнальный вход 5 МГц третьего ключа 70, вторым - объединенные сигнальные входы 20 МГц ключей 68, 69, 71. Выход девятого разряда второго регистра 62 подключен параллельно к первому Uот управляющему входу второго ключа 69, к вторым управляющим Uз входам ключей 68, 70, 71 и к первому управляющему Uот входу второго блока 65 ключей и второму управляющему Uз входу первого блока 63 ключей. Выход первого ключа 68 подключен к первому управляющему Uвыд1 входу третьего регистра 64, второй управляющий Uвыд2 вход которого подключен с выходу второго ключа 69, к которому подключен и счетный вход Uсч вычитающего счетчика 66 импульсов. Выход дешифратора 67 подключен параллельно к первому управляющему Uот входу первого блока 63 ключей, к второму управляющему Uз входу второго блока 65 ключей, к первым управляющим входам ключей 68, 70, 71 и к второму управляющему входу второго ключа 69. Выход третьего ключа 70 подключен к входу Uвыд накопителя 61 кодов кадра, выход ключа 71 подключен к управляющему входу Uвыд второго регистра 62. На вход декодеров 44, 51 поступают девятиразрядные коды с частотой 5 МГц, с выхода декодера идут восьмиразрядные коды с частотой 20 МГц. Блоки 45, 52 удвоения отсчетов идентичны /фиг.9/, каждый включает триггер 72, вход которого является управляющим входом блока, первый 73 и второй 74 блоки ключей /в каждом по восемь ключей/, первый 75, второй 76, третий 77 и четвертый 78 регистры, первый 80 и второй 81 блоки элементов задержек в каждом по восемь задержек, сумматор 79 и шестнадцать диодов. Информационными входами являются поразрядно объединенные первый-восьмой входы блоков 73, 74 ключей, первым-восьмым выходами являются поразрядно объединенные первый-восьмой выходы блоков 80, 81 элементов задержек и выходы ноль-семь сумматора 79. Накопители 46, 53 кодов кадра идентичны, каждый содержит /фиг.10/ блоки 821-1000 регистров по числу строк в кадре. Информационными входами накопителя кодов кадра являются поразрядно объединенные первые-восьмые входы всех /1000/ блоков 82 регистров. Выходами являются выходы всех блоков 82 регистров, всего 12,8×106/1600×8×1000/. Управляющими входами являются: первым - первый управляющий вход 25 Гц первого блока 821 регистров, вторым - объединенные вторые управляющие Uвыд входы 25 кГц блоков 82 регистров, третий - объединенные третьи управляющие Uд входы 40 МГц всех блоков 82 регистров. Управляющий выход каждого предыдущего блока регистров является первым управляющим входом для каждого последующего блока 82 регистров, управляющий выход последнего /1000/ блока 82 регистров подключен параллельно к четвертым управляющим входам всех блоков регистров 82. Блоки 82 регистров идентичны, каждый включает /фиг.11/ первый 83 и второй 84 ключи, распределитель 85 импульсов и восемь регистров 86, каждый из 1600 разрядов по числу отсчетов в строке. Информационными входами блока 82 регистров являются поразрядно объединенные третьи входы разрядов восьми регистров 861-8, выходами являются параллельные выходы всех разрядов /1600/ восьми регистров 86 12800/1600×8/. Выходы 1000 блоков регистров являются выходами каждого накопителя 46 /53/ кодов кадра, всего выходов 12,8×106/2800×1000/. Управляющими входами являются: первым - первый управляющий Uот вход /25 Гц/ первого ключа 83, вторым - сигнальный вход Uвыд /25 кГц/ второго ключа 84, третий - сигнальный вход Uд /40 МГц/ первого ключа 83, четвертым - первый управляющий Uот вход второго ключа 84. Выход первого ключа 83 подключен к входу распределителя 85 импульсов, выходы которого последовательно, начиная с первого, подключены к первым /тактовым/ входам разрядов параллельно восьми регистров 86, последний /1600/ выход подключен к второму управляющему Uз входу своего ключа 83 и является управляющим выходом в следующий блок регистров. Выход второго ключа 84 подключен к вторым управляющим входам разрядов параллельно восьми регистров 86 и к второму управляющему входу Uз ключа 84, прошедший один импульс Uвыд закрывает ключ 84. Выходы накопителей 46, 53 кодов кадра подключены к входам своих блоков 47, 54 импульсных усилителей, каждый из которых содержит импульсных усилителей по числу выходов с накопителя кодов кадра 12,8×106/1600×8×1000/. Выходы трех блоков 47 импульсных усилителей подключены к входам правого экрана 48, выходы трех блоков 54 импульсных усилителей подключены к входам левого экрана 55. Плоскопанельные экраны 48, 55 идентичны, каждый содержит элементы матриц по числу разрешения кадра: 1,6·106/1600×1000/ пикселов. Общий вид элемента матрицы на фиг.13 содержит светодиод 87 белого свечения, корпус 88 соответствующей формы, объединяющий в себе три ячейки: 89 левая нижняя излучает красный цвет R, 90 верхняя излучает зеленый цвет G, 91 правая нижняя излучает синий цвет В. Каждая ячейка имеет цилиндрический корпус из изоляционного непрозрачного материала 92, микрообъектив 93 в переднем торце корпуса 92, соответствующий цветной светофильтр 94 в выходном торце корпуса, диафрагму 95, имеющую цилиндрический корпус 96 с прорезями, и включает с первого 971 по восьмой 978 микропьезоэлементы, первые торцы которых с двумя управляющими входами жестко закреплены в корпусе ячейки 96, вторые свободные концы микропьезоэлементов 971-8 являются шторками диафрагмы, размещены в прорезях корпуса 96 и выполнены в форме плоских непрозрачных тонких лепестков, каждый из которых имеет соответствующую форму и площадь, величины площадей от первого микропьезоэлемента к восьмому соответствуют принципу двоичного кода: 27, 26, 25…21, 20. Управляющие входы микропьезоэлементов 971-8 являются управляющими входами ячеек и подключены к соответствующим выходам соответствующих импульсных усилителей в блоках 47, 54 импульсных усилителей. Лепестки микропьезоэлементов являются исполнительными элементами /шторками/ диафрагмы и по управляющим сигналам с импульсных усилителей открывают часть поперечного пространства диафрагмы соответственно весу разряда, к которому принадлежит лепесток, приведено в таблице, фиг.16.

| Номер разряда в коде | 1 | 2 | 3 | 4 | 5 | 6 | 7 | 8 |

| Вес разряда в коде | 27 | 26 | 25 | 24 | 23 | 22 | 21 | 20 |

| Открываемая часть диафрагмы, в % | 50 | 25 | 12,5 | 6,25 | 3,125 | 1,56 | 0,78 | 0,39 |

Цветной светофильтр 94 расположен в выходном торце корпуса 92 ячейки /фиг.14/. Лепестки микропьезоэлементов размещаются в прорезях корпуса 96 диафрагмы для исключения помех друг другу. Управляющие входы микропьезоэлементов 971-8 являются управляющими входами /фиг.16/ ячейки и подключены к выходам своих импульсных усилителей в блоках 47, 54. В отсутствие управляющих сигналов /импульсов единиц кода/ микропьезоэлементы в исходном ненапряженном состоянии, все лепестки сосредоточены к центру диафрагмы и полностью закрывают путь потоку излучения. При поступлении управляющего импульса микропьезоэлемент выполняет изгиб и выводит свой свободный конец /лепесток/ из внутреннего пространства диафрагмы, открывая ее часть соответственно весу этого разряда в коде. При поступлении кода 11111111 управляющие импульсы поступают на все восемь микропьезоэлементов, диафрагма открыта полностью /на 100%/. При разных значениях кодов открываются соответствующие части диафрагмы: яркость излучения ячейки прямо пропорциональна коду видеосигнала. Длительность управляющих импульсов соответствует длительности кадра, при частоте 25 Гц составляет 40 мс, соответственно лепестки микропьезоэлементов в открытом состоянии тоже 40 мс. Ячейки с микропьезоэлементами выполняются в высшей степени миниатюрными для получения элементов матриц с мизерными размерами. Ячейки изготавливаются отдельно, затем их по трем цветам светофильтров объединяют в элемент матрицы, из которых набирают экран, расположение элементов матриц в экране на фиг.15. Каждый элемент матрицы формирует свой пиксел яркостью и цветовым тоном соответственно трех кодов видеосигналов R, G, В /R2, G2, B2/, которые обеспечивают расчетное число 16777216 цветовых оттенков.

Блок 56 выделения строчных синхроимпульсов /ССИ/ и блок 58 выделения синхроимпульсов стереопар /СИС/ идентичны, каждый включает /фиг.18/ пятиразрядный счетчик 98 импульсов, дешифратор 99, элемент НЕ 100, первый Д1 и второй Д2 диоды. Информационным входом блока является счетный вход счетчика 98 импульсов /вход 1/, управляющим входом является вход диода Д1 /вход 2/, выход которого подключен к управляющему входу Uо счетчика 98 импульсов. Выходом блока 56 /58/ является выход дешифратора 99, который также через диод Д2 подключен к выходу элемента НЕ 100, а вместе они подключены к управляющему входу счетчика 98 импульсов после диода Д1. Код ССИ и СИС являются двадцатисемиразрядными из одних единиц /импульсов/. Код ССИ поступает с формирователя 42 импульсов на счетный вход в блоке 56, управляющий его вход подключен к выходу второго формирователя 49 импульсов. Код СИС поступает на счетный вход блока 58 со второго формирователя 49 импульсов, управляющий вход блока 58 подключен к выходу формирователя 42 импульсов. При поступлении кода ССИ на вход счетчика 98 он ведет счет двадцати семи импульсов подряд, на выходах счетчика формируется код 11011, который дешифрируется дешифратором 99, и на выходе блока 56 появляется импульс, представляющий импульс ССИ /25 кГц/. В момент поступления с формирователя 42 импульсов кода ССИ с выхода формирователя 49 импульсов кода нет /фиг.2 вверху/. Начиная со второго кода строки с блока 49 пойдут коды на управляющий вход Uо счетчика 98 импульсов, с приходом каждого импульса /единицы кода/ счетчик 98 будет ими обнуляться. Параллельно на счетный вход счетчика 98 поступают коды с формирователя 42, в каждом имеются и единицы и нули, и по каждому нулю элемент НЕ 100 выдает сигнал на управляющий Uо вход, который тоже обнуляет счетчик 98: в результате счетчик не сможет достичь счета 27 импульсов подряд. В добавление с выхода дешифратора 99 сигнал ССИ через диод поступает на вход Uо и тоже обнуляет счетчик 98 импульсов. Схемы 56, 58 /фиг.18/ исключают появление на выходе ложного ССИ /СИС/. При поступлении кода СИС на счетный вход блока 58 на его управляющий вход Uо с выхода формирователя 42 импульсов коды не идут, это обеспечивает ключ 37 в блоке 1 /фиг.4/, который на время прохода кода СИС /200 нс/ закрывает ключ 37, и импульсы ССИ не проходят через ключ 37. По окончании длительности кода СИС ключ 37 открывается. Работа блока 58 аналогична работе блока 56.

При работе видеоадаптера ПК коды цветовых сигналов R, G, В правого кадра стереопары поступают с выходов 1-3 видеоадаптера ПК /фиг.1/ на входы трех кодеров 9-11, коды цветовых сигналов R2, G2, B2 левого кадра стереопары поступают с выходов 4-6 видеоадаптера ПК параллельно на входы трех кодеров 12-14. Частота следования кодов в видеорежиме 1000стр×800отсч×25 Гц составляет 20 МГц.

Работа кодеров 9-14, фиг.3.

Кодеры работают идентично. 8-разрядные коды цветового сигнала в последовательном виде с частотой разрядов 160 МГц /20 МГц×8/ с выхода 1-6 видеоадаптера ПК поступают на сигнальный вход ключа 15, открываемый передним фронтом импульса СИС, и остается открытым весь период стереопары /40 мс/. Сигналы разрядов кода заполняют первый регистр 16, код принимает параллельный вид, в котором он и используется дальше.

С регистра 16 код выдается сигналом Uвыд 20 МГц с пятого выхода синтезатора 2 частот /фиг.1/ во второй регистр 17, на первые входы схемы сравнения 18 и на первый-восьмой входы блока 21 элементов задержек. Код в блоке 21 задерживается на время срабатывания схемы сравнения 18 нс и поступает через открытые ключи блока 22 на входы буферного накопителя 23 кодов кадра. Схема сравнения 18 выполняет сравнение по величине каждого предыдущего и последующего кодов для выявления равенства кодов или неравенства. При следовании неравных кодов они проходят через открытые ключи блока 22 и поступают в буферный накопитель 23 кодов, выдача из которого идет сигналами Uвыд 5 МГц. При коэффициенте сжатия выше 4 эта частота выдачи будет тем более удовлетворять. Схема сравнения 18 выполняет сравнение кодов по величине, представлена двумя микросхемами 530СП1 с временем срабатывания 18 нс [5, c.279]. При неравенстве кодов код А больше кода В появляется сигнал на выходе 2 блока 18 /в микросхеме выход 5 [5, с.272, рис.2.190]/, при равенстве кодов появляется сигнал с выхода 1 схемы 18 сравнения /в микросхеме выход 7/, который закрывает ключи в блоке 22, поступает счетным импульсом в счетчик 19 импульсов и как сигнал Uвыд на первый управляющий вход регистра 17. Счетчик 19 восьмиразрядный, ведет счет импульсов с выхода 1 блока 18, пока идут коды, равные по величине. Максимальный код в счетчике 19 11111111 /255/, отсюда диапазон коэффициентов сжатия потока кодов от 1 до 255. Счетчик 19 из микросхем К531ИЕ160 с временем срабатывания 9 нс [5, с.428]. При неравных кодах /А больше В или А меньше В/ с объединенных выходов 2 и 3 схемы сравнения 18 следует сигнал Uвыд, который используется для выдачи кода числа равных кодов из счетчика 19 через диоды на входы блока 23 и для заполнения в блоке 23 девятого разряда, с которого этот сигнал будет использоваться далее для опознания по нему кода числа равных кодов при декодировании на приемной стороне.

Этот же сигнал открывает ключи в блоке 22 и обнуляет регистр 17 /вход 2/. Выданный перед этим с блока 23 код является первым кодом последовательности, на диаграммах фиг.3 эти коды помечены крестиками, коды, равные по величине и подсчитанные счетчиком 19, исключаются из потока, за их счет и идет сжатие. Емкость буферного накопителя 23 кодов 200·103 девятиразрядных кодов обеспечивает следование с выхода кодера кодов с частотой 5 МГц. При следовании подряд кодов, равных по величине более 255, в работу вступает дешифратор 20. При коде 11111111 дешифратор 20 выдает сигнал, который одновременно открывает ключи в блоке 22, обнуляет регистр 17, сигналом Uвыд выдает код из счетчика 19 /вход 1/ и обнуляет его, а в девятый разряд блока 23 поступает сигнал для опознания кода числа равных кодов. Пропускная способность кодера задается временем срабатывания схемы сравнения 18, которая обеспечивает до 40 Мбайт/с и удовлетворяет поступающему в кодер потоку 20 Мбайт/с. С выходов кодеров 9-11 коды в параллельном виде поступают на первый информационный вход формирователя 1 кодов /фиг.1/, с выходов кодеров 12-14 коды в параллельном виде поступают на второй информационный вход формирователя 1 кодов.

Работа формирователя 1 кодов, фиг.4.

С началом периода стереопары счетчик 34 принимает первый счетный импульс строки 5 МГц, дешифратор 35 при коде 00000001 выдает с первого выхода импульс Uот, который открывает ключ 36, и параллельно с этим сигнал СИС поступает передним фронтом, закрывает ключ 37 на время прохода кода СИС с СРИ 4 на четвертый управляющий вход формирователя 1 кодов. Двадцатисемиразрядный код СИС из одних единиц поступает на второй вход элемента ИЛИ 31, каждый импульс кода открывает на время своей длительности 7,4 нс // выходной ключ 32, который пропускает 27 положительных полусинусоид, поступающих модулирующим сигналом на второй вход амплитудного модулятора 7 /фиг.1/. С приходом второго импульса 5 МГц на счетный вход счетчика 34 он проходит открытый к этому моменту ключ 36 и запускает в работу СРИ 28, 33, с выходов которых 27 импульсов последовательно поступают на вторые входы элементов И блоков 24 и 29, на первые входы которых поступают в параллельном виде коды сигналов R, G, В в блоке 24 и коды сигналов R2, G2, B2 в блоке 29. Формирователь 1 кодов первым кодом стереопары выдает код СИС, первым кодом строки, начиная со второй строки кадра, выдает код ССИ, затем выдает со второго по 200-й коды цветовых сигналов /фиг.2/. На выходе формирователя 1 кодов сигналы единиц кодов R, G, В и кода ССИ представляются положительными полусинусоидами моночастоты 135 МГц, сигналы единиц кодов R2, G2, B2 и кода СИС представляются отрицательными полусинусоидами той же частоты. Временные диаграммы работы формирователя 1 кодов на фиг.17. Сигналы 1-9 разрядов кодов R, G, В правого кадра и сигналы 1-9 разрядов кодов R2, G2, B2 левого кадра стереопары образуют вместе суммарный код /фиг.2/. На третий информационный вход формирователя 1 кодов поступает код ССИ. На вторые входы элементов И блоков 24, 29 поступают последовательно по 27 импульсов с СРИ 28, 33. Так как ключ 36 открывается первым счетным импульсом строки с дешифратора 35, то СРИ 28, 33 начинают работать со второго импульса строки, и формирование кодов видеосигналов идет со второго по 200-й отсчеты строки. С выходов блока 24 и 29 импульсы кодов поступают через элементы ИЛИ 25, 26 и 30, 31 на управляющие входы своих выходных ключей 27 и 32 и открывают их на длительность импульса 7,4 нс. Выходной ключ 27 при каждом импульсе пропускает в открытом состоянии одну положительную полусинусоиду моночастоты 135 МГц на выход, выходной ключ 32 в открытом состоянии пропускает одну отрицательную полусинусоиду той же частоты. Выходы ключей 27, 32 объединены, поэтому выходные сигналы с формирователя 1 кодов представляются полными или неполными синусоидами 135 МГц со стабильностью частоты тактового генератора ПК и являются синусоидальным модулирующим сигналом для несущей частоты 2025 МГц в амплитудном модуляторе 7 /фиг.1/. Спектр амплитудно-модулированного сигнала /фиг.5/ состоит из несущей и двух боковых частот. Сама несущая и одна из боковых частот в информационном смысле являются избыточными, поэтому в амплитудном модуляторе 7 подавляется несущая 2025 МГц и отфильтровывается верхняя боковая частота 2160 МГц. В выходной усилитель 8 выдается нижняя боковая частота 1890 МГц с видеоинформацией, которая при стабильности несущей 10-7 занимает полосу ±189 Гц или 379 Гц. На приемной стороне /фиг.6/ радиосигналы принимаются блоком 39, который является селектором каналов с электронной настройкой с блока 38 выбора канала передачи. Блок 39 включает входную цепь, усилитель радиочастоты, смеситель и соответствую