Дифференциальный усилитель с высокочастотной коррекцией

Иллюстрации

Показать всеИзобретение относится к радиотехнике и связи для усиления аналоговых сигналов, в структуре аналоговых микросхем различного функционального назначения (например, широкополосных и избирательных усилителях (У) и компараторах). Технический результат: повышение коэффициента усиления в диапазоне средних частот до уровня , который в 10÷40 раз превышает Ку на постоянном токе. Это позволяет в ряде случаев исключить дополнительные каскады У, уменьшить общее энергопотребление в сравнении с многокаскадными У. Дифференциальный усилитель (ДУ) содержит первый (1) и второй (2) входные транзисторы (Т), эмиттеры которых через первый (3) токостабилизирующий двухполюсник (ТД) связаны с первой (4) шиной источников питания (ИП), первый (5) резистор коллекторной нагрузки, первый вывод которого соединен с выходом (6) ДУ, коллектором второго (2) входного Т и коллектором первого (7) вспомогательного Т, второй (8) ТД, включенный между эмиттером первого Т (7) и первой (4) шиной ИП, причем коллектор первого (1) входного Т связан со второй (9) шиной ИП. Второй вывод резистора коллекторной нагрузки (5) соединен со второй (9) шиной ИП через первый (10) дополнительный резистор и соединен с эмиттером первого Т (7) через первый (11) корректирующий конденсатор, причем база первого Т (7) связана с первой (12) цепью установления его статического режима. 4 з.п. ф-лы, 14 ил.

Реферат

Изобретение относится к области радиотехники и связи и может быть использовано в качестве устройства усиления аналоговых сигналов, в структуре аналоговых микросхем различного функционального назначения (например, широкополосных и избирательных усилителях и компараторах).

В современной микроэлектронике находят широкое применение классические дифференциальные каскады с резистивной нагрузкой, включенной в коллекторную цепь входного транзистора [1-19].

Наиболее близким по технической сущности к заявляемому устройству является ДУ по патенту США №6.825.723, fig.1.

Существенный недостаток известного устройства состоит в том, что при любых известных способах высокочастотной коррекции его амплитудно-частотной характеристики коэффициент передачи по напряжению скорректированного ДУ всегда меньше, чем его Ку на постоянном токе, т.е. в области низких частот.

Основная задача предлагаемого изобретения состоит в повышении коэффициента усиления в диапазоне средних частот до уровня , который в 10÷40 раз превышает Ку на постоянном токе. Это позволяет в ряде случаев исключить дополнительные каскада усиления, уменьшить общее энергопотребление в сравнении с многокаскадными усилителями.

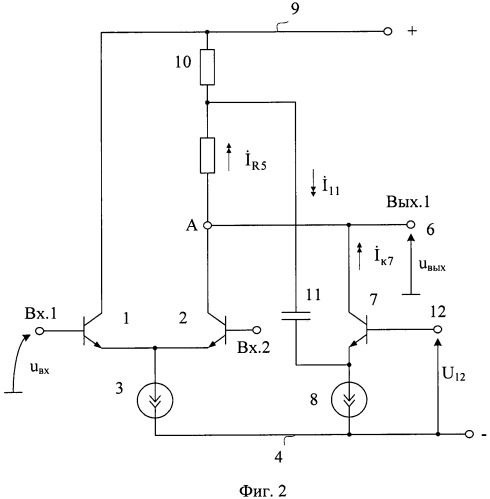

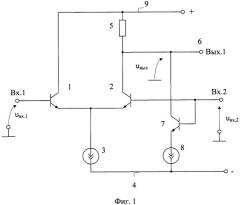

Поставленная задача решается тем, что в дифференциальном усилителе фиг.1, содержащем первый 1 и второй 2 входные транзисторы, эмиттеры которых через первый 3 токостабилизирующий двухполюсник связаны с первой 4 шиной источников питания, первый 5 резистор коллекторной нагрузки, первый вывод которого соединен с выходом 6 устройства, коллектором второго 2 входного транзистора и коллектором первого 7 вспомогательного транзистора, второй 8 токостабилизирующий двухполюсник, включенный между эмиттером первого 7 вспомогательного транзистора и первой 4 шиной источников питания, причем коллектор первого 1 входного транзистора связан со второй 9 шиной источников питания, предусмотрены новые элементы и связи - второй вывод резистора коллекторной нагрузки 5 связан со второй 9 шиной источников питания через первый 10 дополнительный резистор и соединен с эмиттером первого 7 вспомогательного транзистора через первый 11 корректирующий конденсатор, причем база первого 7 вспомогательного транзистора связана с первой 12 цепью установления его статического режима.

Схема усилителя-прототипа показана на фиг.1. На фиг.2 представлена схема заявляемого устройства в соответствии с п.1 формулы изобретения.

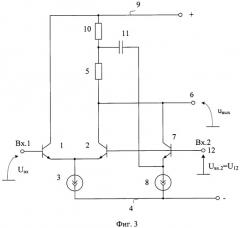

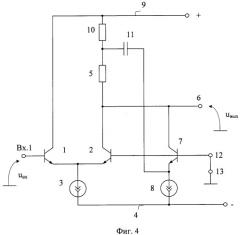

На фиг.3 приведена схема заявляемого ДУ в соответствии с п.2, а на фиг.4 - п.3 формулы изобретения.

На фиг.5 приведена схема заявляемого ДУ в соответствии с п.4, а на фиг.6 - п.5 формулы изобретения.

На фиг.7 показана схема ДУ фиг.5, в которой первый 3 токостабилизирующий двухполюсник реализован на транзисторах 21-22 и резисторах 23-24.

На фиг.8 представлен график теоретической амплитудно-частотной характеристики ДУ фиг.2.

На фиг.9 показана схема ДУ-прототипа в среде компьютерного моделирования Cadence на моделях интегральных транзисторов HJW ФГУП НПП «Пульсар».

На фиг.10 показаны амплитудно-частотные характеристики схемы фиг.8 при разных емкостях конденсатора С1=С11.

На фиг.11 показана схема заявляемого устройства фиг.2 в среде компьютерного моделирования Cadence на моделях интегральных транзисторов HJW ФГУП НПП «Пульсар».

На фиг.12 приведены амплитудно-частотные характеристики ДУ фиг.11 при разных значениях емкости корректирующего конденсатора Сn=С11.

На фиг.13 показана схема предлагаемого ДУ фиг.7 в среде компьютерного моделирования Cadence на моделях интегральных транзисторов HJW ФГУП НПП «Пульсар».

На фиг.14 приведены амплитудно-частотные характеристики ДУ фиг.13 при разных значениях емкости корректирующего конденсатора Сn=С11.

Дифференциальный усилитель фиг.2 содержит первый 1 и второй 2 входные транзисторы, эмиттеры которых через первый 3 токостабилизирующий двухполюсник связаны с первой 4 шиной источников питания, первый 5 резистор коллекторной нагрузки, первый вывод которого соединен с выходом 6 устройства, коллектором второго 2 входного транзистора и коллектором первого 7 вспомогательного транзистора, второй 8 токостабилизирующий двухполюсник, включенный между эмиттером первого 7 вспомогательного транзистора и первой 4 шиной источников питания, причем коллектор первого 1 входного транзистора связан со второй 9 шиной источников питания. Второй вывод резистора коллекторной нагрузки 5 соединен со второй 9 шиной источников питания через первый 10 дополнительный резистор и соединен с эмиттером первого 7 вспомогательного транзистора через первый 11 корректирующий конденсатор, причем база первого 7 вспомогательного транзистора связана с первой 12 цепью установления его статического режима.

На фиг.3, в соответствии с п.2 формулы изобретения, в качестве первой 12 цепи установления статического режима используется база второго 2 входного транзистора, на которую могут подаваться разные опорные уровни напряжения U12=Uвх.2.

На фиг.4, в соответствии с п.3 формулы изобретения, база второго 2 входного транзистора связана с общей шиной 13 первого 4 и второго 9 источников питания.

На фиг.5, в соответствии с п.4 формулы изобретения, коллектор первого 1 входного транзистора соединен со второй 9 шиной источников питания через последовательно соединенные второй 14 резистор коллекторной нагрузки и второй 15 дополнительный двухполюсник, общий узел которых через второй 16 корректирующий конденсатор соединен с эмиттером второго 17 вспомогательного транзистора, эмиттер второго 17 вспомогательного транзистора подключен к первой 4 шине источников питания через третий 18 токостабилизирующий двухполюсник, его коллектор соединен с коллектором первого 1 входного транзистора и вторым 19 выходом устройства, а база связана со второй 20 цепью установления статического режима.

На фиг.6, в соответствии с п.5 формулы изобретения, в качестве первой 12 цепи установления статического режима используется база второго 2 входного транзистора, а в качестве второй 20 цепи установления статического режима - база первого 1 входного транзистора.

Рассмотрим работу ДУ фиг.2.

Предельный коэффициент усиления по напряжению дифференциального каскада фиг.1 при емкости конденсатора 11 (С11), равной нулю, определяется сопротивлением первого 5 резистора коллекторной нагрузки R5>>R10:

где S1-2=(rэ1+rэ2)-1 - крутизна усиления ДУ в режиме короткого замыкания по выходу, зависящая от сопротивлений эмиттерных переходов (rэ1, rэ2) транзисторов 1 и 2.

Покажем аналитически, что более высокие значения Ку в диапазоне средних частот реализуются в схеме фиг.2 при С1.

Действительно, комплексный коэффициент передачи по напряжению ДУ фиг.2 определяется по формуле:

где - комплекс эквивалентного выходного импеданса узла «А»;

- комплексная крутизна ДУ в режиме короткого замыкания выхода ДУ.

Для ДУ фиг.2, в котором отсутствует корректирующая емкость 11, при условии, что R5>>R10:

Комплекс эквивалентной нагрузки можно найти по формуле:

где ,

- комплекс импеданса первого 11 корректирующего конденсатора;

.

После преобразований последней формулы находим, что

Поэтому коэффициент усиления по напряжению ДУ фиг.2

или при :

Таким образом, выигрыш по Ку, который дает токовая ВЧ-коррекция в ДУ фиг.2

Если ω=0, то . В области высоких частот (когда ω→∞)

При этом модуль коэффициента ДУ фиг.1, характеризующего эффективность ВЧ-коррекции:

График функции показан на фиг.8.

Начиная с частоты f3, эффективность токовой ВЧ-коррекции уменьшается в связи с влиянием коэффициента , емкости коллектор-база транзисторов 2 и 7 и их емкостей на подложку.

В схеме ДУ фиг.3 статический режим транзистора 7 устанавливается таким же способом, как и у входного транзистора 2 - источником сигнала Uвх.2-U12.

В схеме ДУ фиг.4 роль первой 12 цепи установления статического режима выполняет общая шина 13 источников питания.

Схемы фиг.5, фиг.6 и фиг.7 являются дифференциальными усилителями с двумя противофазными выходами, относительно которых обеспечивается предлагаемая ВЧ коррекция.

Графики фиг.10, фиг.11, фиг.14 соответствуют фиг.8. Они показывают высокое совпадение теоретической (фиг.8) и практических характеристик. При этом выигрыш по Ку в диапазоне средних частот ДУ, зависящем от численных значений емкости коррекции, достигает 18-22 дБ (т.е. более чем в 10 раз).

БИБЛИОГРАФИЧЕСКИЙ СПИСОК

1. Патент США №4.027.272, fig.1

2. Патент Японии JP 54-104266

3. Патент Японии JP 54-84458

4. Патент Японии JP 54-84457

5. Патент Японии JP 54-104267

6. Патент RU 1748611

7. Патентная заявка SU №2006/0186965, fig.2

8. Патент Японии JP 54-102949

9. Патент США №4.536.717

10. Патент ES 2329183, fig.4

11. Патент США №4.365.207, fig.2

12. Патентная заявка WO/2002/047257

13. Патентная заявка WO/2006/068455

14. Патент Японии JP 51-112253

15. Патент США №3.366.889, fig.1

16. Патентная заявка КР 2005004511

17. Патент США №4.689.579, fig.4

18. Патент Японии JP 53-17051

19. Патент ЕР 2149989, fig.4

1. Дифференциальный усилитель с высокочастотной коррекцией, содержащий первый (1) и второй (2) входные транзисторы, эмиттеры которых через первый (3) токостабилизирующий двухполюсник связаны с первой (4) шиной источников питания, первый (5) резистор коллекторной нагрузки, первый вывод которого соединен с выходом (6) устройства, коллектором второго (2) входного транзистора и коллектором первого (7) вспомогательного транзистора, второй (8) токостабилизирующий двухполюсник, включенный между эмиттером первого (7) вспомогательного транзистора и первой (4) шиной источников питания, причем коллектор первого (1) входного транзистора связан со второй (9) шиной источников питания, отличающийся тем, что второй вывод резистора коллекторной нагрузки (5) соединен со второй (9) шиной источников питания через первый (10) дополнительный резистор и соединен с эмиттером первого (7) вспомогательного транзистора через первый (11) корректирующий конденсатор, причем база первого (7) вспомогательного транзистора связана с первой (12) цепью установления его статического режима.

2. Дифференциальный усилитель по п.1, отличающийся тем, что в качестве первой (12) цепи установления статического режима используется база второго (2) входного транзистора.

3. Дифференциальный усилитель по п.2, отличающийся тем, что база второго (2) входного транзистора связана с общей шиной (13) первого и второго источников питания.

4. Дифференциальный усилитель по п.1, отличающийся тем, что коллектор первого (1) входного транзистора соединен со второй (9) шиной источников питания через последовательно соединенные второй (14) резистор коллекторной нагрузки и второй (15) дополнительный двухполюсник, общий узел которых через второй (16) корректирующий конденсатор соединен с эмиттером второго (17) вспомогательного транзистора, эмиттер второго (17) вспомогательного транзистора подключен к первой (4) шине источников питания через третий (18) токостабилизирующий двухполюсник, его коллектор соединен с коллектором первого (1) входного транзистора и вторым (19) выходом устройства, а база связана со второй (20) цепью установления статического режима.

5. Дифференциальный усилитель по п.4, отличающийся тем, что в качестве первой (12) цепи установления статического режима используется база второго (2) входного транзистора, а в качестве второй (20) цепи установления статического режима - база первого (1) входного транзистора.