Дифференциальный усилитель с парафазным выходом

Иллюстрации

Показать всеИзобретение относится к области радиотехники и связи и может быть использовано в качестве устройства усиления аналоговых сигналов, в структуре аналоговых микросхем различного функционального назначения (например, SiGe-операционных усилителях (ОУ), СВЧ-усилителях, компараторах, непрерывных стабилизаторах напряжения и т.п.). Технический результат: повышение предельных значений коэффициента усиления по напряжению ДУ при низковольтном питании. Дифференциальный усилитель с парафазным выходом содержит входной дифференциальный каскад (1) с первым (2) и вторым (3) выходами, первый (4) двухполюсник коллекторной нагрузки, включенный между первым (2) выходом входного дифференциального каскада и первым (5) источником питания, второй (6) двухполюсник коллекторной нагрузки, включенный между вторым (3) выходом входного дифференциального каскада и первым (5) источником питания, второй (7) источник питания, связанный с эмиттерной цепью входного дифференциального каскада (1). Первый (2) выход входного дифференциального каскада (1) подключен ко входу первого (8) неинвертирующего повторителя тока, второй (3) выход входного дифференциального каскада (1) подключен ко входу второго (9) неинвертирующего повторителя тока, выход первого (10) дополнительного инвертирующего усилителя тока подключен ко второму (3) выходу входного дифференциального каскада (1), а его вход связан с выходом первого (8) неинвертирующего повторителя тока, выход второго (11) дополнительного инвертирующего усилителя тока подключен к первому (2) выходу входного дифференциального каскада (1), а его вход связан с выходом второго (9) неинвертирующего повторителя тока, причем общие эмиттерные выходы первого (10) и второго (11) дополнительных инвертирующих усилителей тока связаны со вторым (7) источником питания. 4 з.п. ф-лы, 16 ил.

Реферат

Изобретение относится к области радиотехники и связи и может быть использовано в качестве устройства усиления аналоговых сигналов, в структуре аналоговых микросхем различного функционального назначения (например, SiGe-операционных усилителях (ОУ), СВЧ-усилителях, компараторах, непрерывных стабилизаторах напряжения и т.п.).

В современной микроэлектронике находят применение классические дифференциальные усилители (ДУ) с двумя резисторами в коллекторной цепи выходных транзисторов [1-17]. Данная архитектура является основой широкого класса аналоговых и цифровых устройств и является базовой как для существующих, так и для принципиально новых нанотехнологий [10].

Наиболее близким по технической сущности к заявляемому устройству является классический входной дифференциальный каскад по Ав. свид. СССР №1102019.

Существенный недостаток известного ДУ, архитектура которого присутствует также в других усилительных каскадах [1-17], состоит в том, что при ограничениях на напряжение питания (Еп), характерных для SiGe технологических процессов (Еп≤2,0÷2,5 В), его коэффициент усиления по напряжению (Kу) получается небольшим (Kymax=10÷20). В первую очередь это обусловлено ограничениями на сопротивления резисторов коллекторной нагрузки, которые из-за малых Еп не могут выбираться высокоомными. Поэтому для повышения Ку применяются так называемые динамические нагрузки (ДН), например, на биполярных транзисторах, которые требуют для обеспечения линейного режима работы 0,8÷1,6 В статического напряжения UДН между источником питания и выходом ДН. Причем численные значения UДН равны 0,8 В для простейших динамических нагрузок, имеющих, к сожалению, невысокое выходное дифференциальное сопротивление

,

где UЭрли - напряжение Эрли выходного р-n-р транзистора ДН;

Iэ=I0 - статический ток эмиттера р-n-р выходного транзистора ДН.

Для интегральных транзисторов ФГУП НПП «Пульсар» UЭрли=20÷30 В. Следовательно, при I0=1 мА применение классических динамических нагрузок не позволяет получить Ку>200÷300. Более высокие выходные сопротивления RДН реализуются в токовых зеркалах Вильсона или каскадных схемах. Однако они работают только в том случае, когда статическое напряжение между выводами такой динамической нагрузки более чем 2Uэб≥1,6 В. При низковольтном питании это неприемлемо.

Таким образом, при малых напряжениях питания, а особенно в тех случаях, когда требуется получить более-менее значительные амплитуды выходного напряжения, классические схемотехнические решения ДУ неэффективны.

Основная задача предполагаемого изобретения состоит в повышении предельных значений коэффициента усиления по напряжению ДУ при низковольтном питании.

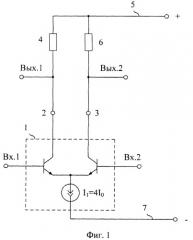

Поставленная задача достигается тем, что в дифференциальном усилителе фиг.1, содержащем входной дифференциальный каскад 1 с первым 2 и вторым 3 выходами, первый 4 двухполюсник коллекторной нагрузки, включенный между первым 2 выходом входного дифференциального каскада и первым 5 источником питания, второй 6 двухполюсник коллекторной нагрузки, включенный между вторым 3 выходом входного дифференциального каскада и первым 5 источником питания, второй 7 источник питания, связанный с эмиттерной цепью входного дифференциального каскада 1, предусмотрены новые элементы и связи - первый 2 выход входного дифференциального каскада 1 подключен ко входу первого 8 неинвертирующего повторителя тока, второй 3 выход входного дифференциального каскада 1 подключен ко входу второго 9 неинвертирующего повторителя тока, выход первого 10 дополнительного инвертирующего усилителя тока подключен ко второму 3 выходу входного дифференциального каскада 1, а его вход связан с выходом первого 8 неинвертирующего повторителя тока, выход второго 11 дополнительного инвертирующего усилителя тока подключен к первому 2 выходу входного дифференциального каскада 1, а его вход связан с выходом второго 9 неинвертирующего повторителя тока, причем общие эмиттерные выходы первого 10 и второго 11 дополнительных инвертирующих усилителей тока связаны со вторым 7 источником питания.

На чертеже фиг.1 показана схема ДУ-прототипа.

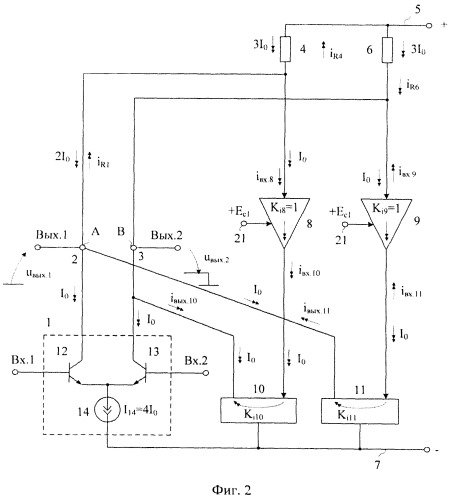

Схема заявляемого устройства, соответствующего п.1 формулы изобретения, показана на чертеже фиг.2.

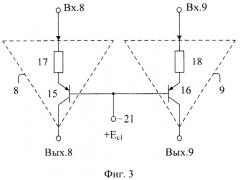

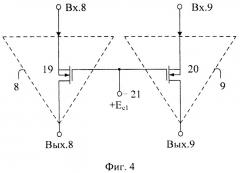

На чертежах фиг.3 и фиг.4 показаны примеры выполнения первого 8 и второго 9 неинвертирующих повторителей тока в соответствии с п.2 и п.3 формулы изобретения.

На чертежах фиг.5 и фиг.6 показаны примеры практической реализации двухполюсников коллекторной нагрузки 4 и 6 в виде полевых транзисторов.

На чертеже фиг.7 представлена схема ДУ-прототипа фиг.1 в среде компьютерного моделирования Cadence на моделях интегральных транзисторов HJW, а на чертеже фиг.8 - заявляемого ДУ фиг.2.

Графики фиг.9 характеризуют зависимость коэффициента усиления по напряжению (Kу) ДУ фиг.7 - фиг.8 при численных значениях коэффициента усиления по току дополнительных инвертирующих усилителей тока 8 и 9 Ki=2.

Аналогично графики фиг.10 показывают АЧХ ДУ фиг.7 и фиг.8 при другом значении Ki≈2,1.

На чертежах фиг.11, фиг.12 приведены графики зависимости (в разном масштабе) коэффициента усиления Kу от численных значений коэффициента передачи дополнительных инвертирующих усилителей тока 10 и 11 (Ki).

На чертеже фиг.13 приведена схема ДУ фиг.2 в среде компьютерного моделирования Cadence на моделях интегральных транзисторов SGB25VD, в котором двухполюсники коллекторной нагрузки 4 и 6 соответствуют чертежам фиг.5 и фиг.6.

На чертеже фиг.14 приведены графики зависимости коэффициента усиления Kу ДУ фиг.13 от численных значений коэффициента передачи по току дополнительных инвертирующих усилителей тока (Ki) 10 и 11 при разных размерах затвора транзисторов коллекторной нагрузки (геометрических параметрах транзисторов, входящих в двухполюсники 5 и 6).

На чертеже фиг.15 приведены графики зависимости коэффициента усиления по напряжению ДУ фиг.13 от численных значений коэффициента передачи инвертирующих усилителей тока (Ki) при ширине затвора транзисторов коллекторной нагрузки 10 мкм и ширине затворов транзисторов двухполюсников 8 и 9, равных 80 мкм.

На чертеже фиг.16 показана амплитудно-частотная характеристика ДУ фиг.13 при ширине затвора транзисторов коллекторной нагрузки 10 мкм и ширине затвора транзисторов двухполюсников 8 и 9, равном 80 мкм.

Дифференциальный усилитель фиг.2 содержит входной дифференциальный каскад 1 с первым 2 и вторым 3 выходами, первый 4 двухполюсник коллекторной нагрузки, включенный между первым 2 выходом входного дифференциального каскада и первым 5 источником питания, второй 6 двухполюсник коллекторной нагрузки, включенный между вторым 3 выходом входного дифференциального каскада и первым 5 источником питания, второй 7 источник питания, связанный с эмиттерной цепью входного дифференциального каскада 1. Первый 2 выход входного дифференциального каскада 1 подключен ко входу первого 8 неинвертирующего повторителя тока, второй 3 выход входного дифференциального каскада 1 подключен ко входу второго 9 неинвертирующего повторителя тока, выход первого 10 дополнительного инвертирующего усилителя тока подключен ко второму 3 выходу входного дифференциального каскада 1, а его вход связан с выходом первого 8 неинвертирующего повторителя тока, выход второго 11 дополнительного инвертирующего усилителя тока подключен к первому 2 выходу входного дифференциального каскада 1, а его вход связан с выходом второго 9 неинвертирующего повторителя тока, причем общие эмиттерные выходы первого 10 и второго 11 дополнительных инвертирующих усилителей тока связаны со вторым 7 источником питания. В частном случае входной дифференциальный каскад 1 реализован на базе транзисторов 12, 13 и двухполюснике 14, ток которого I14=2I0.

На чертеже фиг.3 в соответствии с п.2 формулы изобретения в качестве первого 8 и второго 9 неинвертирующих повторителей тока используются вспомогательные транзисторы 15 и 16 по схеме с общей базой, последовательно с входными эмиттерными цепями которых включены вспомогательные резисторы 17 и 18 для получения заданного уровня входного сопротивления rвх.8=rвх.9=R17=R18.

На чертеже фиг.4, в соответствии с п.3 формулы изобретения, в качестве первого 10 и второго 11 дополнительных инвертирующих усилителей тока рекомендуется использовать классические токовые зеркала, коэффициенты передачи по току которых, в частном случае, имеют значение Ki=2.

На чертеже фиг.4, в соответствии с п.4 формулы изобретения, в качестве первого 8 и второго 9 неинвертирующих повторителей тока используются полевые транзисторы по схеме с общим затвором 19 и 20. В этом случае , , где Si - крутизна полевых транзисторов 19 и 20.

На чертежах фиг.5 и фиг.6, в соответствии с п.5 формулы изобретения, в качестве как первого 4, так и второго 6 двухполюсников коллекторной нагрузки используются N>1 параллельно включенных полевых транзисторов, затворы которых соединены со стоками (элементы 21-24, 25-28). Параллельное включение полевых транзисторов обеспечивает заданный уровень выходного сопротивления в узлах 2 и 3 ДУ фиг.2.

Статический режим ДУ фиг.2 устанавливается двухполюсником 14 и цепью смещения потенциалов 21 (Ec1), в качестве которой могут применяться как резистивные делители напряжения питания, так и более совершенные схемы источников напряжения с малыми выходными сопротивлениями.

Рассмотрим работу ДУ фиг.2 на переменном токе.

Положительное изменение входного напряжения uвх приводит к противофазному, но одинаковому изменению напряжений uвых на выходах ДУ Вых.1 и Вых.2, которые создают токи iR4 и iR6 через двухполюсники коллекторной нагрузки 4, 6 и токи iвх.8, iвх.9 - через входные сопротивления первого 8 и второго 9 неинвертирующих повторителей тока:

где rвх.8, rвх.9 - входные сопротивления неинвертирующих повторителей тока 8 и 9, которые могут иметь такие же значения, что R4=R6.

Приращения токов iвx.8 и iвх.9 передаются на входы дополнительных инвертирующих усилителей тока 10 и 11, а затем на их выходы:

где Ki8=Ki9≈1 - коэффициент усиления по току неинвертирующих повторителей тока 8 и 9;

Ki10, Ki11 - коэффициенты усиления по току дополнительных инвертирующих усилителей тока 10 и 11.

В результате эквивалентные сопротивления в коллекторной цепи 2 и 3 входного дифференциального каскада 1, определяющие коэффициенты усиления ДУ, можно найти по формулам

После преобразований формул (6) и (7) можно найти, что

где Y4, Y6 - проводимости двухполюсников коллекторной нагрузки 4 и 6;

yвх.8, yвх.9 - входные проводимости неинвертирующих повторителей тока 8 и 9, зависящие, в частном случае фиг.3, от резисторов 17 и 18.

Для получения больших Kу необходимо иметь , . Практически это означает, что коэффициенты передачи по току функциональных узлов 8, 9, 10 и 11, а также входные проводимости (увх.8=увх.9=увх) и проводимости двухполюсников 4 и 6 (Y4=Y6=Y0) должны удовлетворять условиям:

или

В частном случае при Ki8=Ki9=1 необходимо, чтобы

Таким образом, для получения максимального выигрыша по Kу коэффициенты передачи по току дополнительных неинвертирующих усилителей тока должны удовлетворять условиям (14) и (15). Например, если rвх=R0, то Ki11=Ki10=2. При rвх=3R0 необходимо иметь Ki11=Ki10=4.

Заданные соотношения между rвх и R0 регулируются, например, числом транзисторов в структуре двухполюсников коллекторной нагрузки 4 и 6 (фиг.5, фиг.6), а также сопротивлениями 17 и 18 во входной цепи неинвертирующих повторителей тока 8 и 9 (фиг.3).

Поэтому коэффициент усиления ДУ фиг.2 при Ki10=Ki11=2, Ki8=1, Ki9=1 увеличивается на один-два порядка. Данный вывод подтверждают результаты компьютерного моделирования фиг.9, фиг.10, фиг.11, фиг.12, фиг.14, схем фиг.7, фиг.8, фиг.13.

В качестве неинвертирующих повторителей тока 8 и 9 авторы рекомендуют применять транзисторные каскады с общей базой (фиг.3) на транзисторах 15 и 16 или полевые транзисторы 19, 20 (фиг.4).

Таким образом, в предлагаемом ДУ фиг.2 при низкоомных двухполюсниках коллекторной нагрузки 4 и 6 реализуются более высокие значения коэффициента усиления по напряжению.

Заявляемая схема особенно перспективна для использования в микроэлектронных SiGe изделиях СВЧ-устройств.

БИБЛИОГРАФИЧЕСКИЙ СПИСОК

1. Патент США №3.541.464

2. Патентная заявка WO 2004/102789

3. Патент США №5.389.893

4. Патент Японии JP 53-142849

5. А.св. СССР 1102019

6. Патентная заявка WO 2005/077525

7. Патентная заявка США №2006/0181348

8. Патентная заявка WO 2006/077525

9. Патент Англии GB 2419052

10. Патентная заявка США №2008/0290941

11. Патент WO 96/21271

12. Патентная заявка США 2009/0108882 fig.3

13. Патент Японии JP 55030218

12. Патент Англии GB 1350352

15. Патент Японии JP 54-47467

16. Патент Японии JP 55099810

17. Патент ФРГ DE 2821942

1. Дифференциальный усилитель с парафазным выходом, содержащий входной дифференциальный каскад (1) с первым (2) и вторым (3) выходами, первый (4) двухполюсник коллекторной нагрузки, включенный между первым (2) выходом входного дифференциального каскада и первым (5) источником питания, второй (6) двухполюсник коллекторной нагрузки, включенный между вторым (3) выходом входного дифференциального каскада и первым (5) источником питания, второй (7) источник питания, связанный с эмиттерной цепью входного дифференциального каскада (1), отличающийся тем, что первый (2) выход входного дифференциального каскада (1) подключен ко входу первого (8) неинвертирующего повторителя тока, второй (3) выход входного дифференциального каскада (1) подключен ко входу второго (9) неинвертирующего повторителя тока, выход первого (10) дополнительного инвертирующего усилителя тока подключен ко второму (3) выходу входного дифференциального каскада (1), а его вход связан с выходом первого (8) неинвертирующего повторителя тока, выход второго (11) дополнительного инвертирующего усилителя тока подключен к первому (2) выходу входного дифференциального каскада (1), а его вход связан с выходом второго (9) неинвертирующего повторителя тока, причем общие эмиттерные выходы первого (10) и второго (11) дополнительных инвертирующих усилителей тока связаны со вторым (7) источником питания.

2. Дифференциальный усилитель по п.1, отличающийся тем, что в качестве первого (8) и второго (9) неинвертирующих повторителей тока используются вспомогательные транзисторы (15) и (16) по схеме с общей базой, последовательно с входными эмиттерными цепями которых включены вспомогательные резисторы (17) и (18).

3. Дифференциальный усилитель по п.1, отличающийся тем, что в качестве первого (10) и второго (11) дополнительных инвертирующих усилителей тока используются классические токовые зеркала, коэффициент передачи по току которых лежит в пределах Кi=0,8÷1,2.

4. Дифференциальный усилитель по п.1, отличающийся тем, что в качестве первого (8) и второго (9) неинвертирующих повторителей тока используются полевые транзисторы по схеме с общим затвором (19) и (20).

5. Дифференциальный усилитель по п.1, отличающийся тем, что в качестве каждого первого (4) и второго (6) двухполюсников коллекторной нагрузки используются N>1 параллельно включенных полевых транзисторов, затворы которых соединены со стоками (21-24, 25-28).