Односторонняя коммутационная матрица

Иллюстрации

Показать всеИзобретение относится к связи и вычислительной технике и может быть использовано в системах коммутации для построения коммутационных полей АТС, сетей ЭВМ, микропроцессорных систем и т.п. Техническим результатом является возможность одновременного электрического соединения каждой из n=2k электрических линий матрицы попарно между собой. Односторонняя коммутационная матрица состоит из управляемых и неуправляемых переключателей, имеющих 2 порта первой пары, 2 порта второй пары и расположенных по n/2-линиям - строкам и k уровням, причем управляемые переключатели имеют также битовый вход управляющего кода С. 4 ил.

Реферат

Изобретение относится к связи и вычислительной технике и может быть использовано в системах коммутации для построения коммутационных полей АТС, сетей ЭВМ, микропроцессорных систем и т.п.

Матрица предназначена для одновременного электрического соединения попарно n=2k коммутируемых электрических линий, каждая из которых может быть как входом, так и выходом электрических сигналов.

Известна однородная коммутационная структура (см. патент РФ №2033635, МПК G06F 7/00). Структура предназначена для управления и перераспределения входных потоков данных в параллельно-конвейерных устройствах и однородных структурах, а также для реализации коммутационных функций от произвольного числа переменных.

Недостатком данного устройства является то, что число переключающих элементов структуры при увеличении числа n коммутируемых линий растет пропорционально n2. При больших значениях n реализация коммутационной структуры технически сложна.

Известна однородная коммутационная структура (см. патент РФ №2136039, МПК G06F 15/163, G06F 7/00). Структура предназначена для управления и перераспределения входных потоков, данных в параллельно-конвейерных устройствах и однородных структурах, а также для реализации коммутационных функций от произвольного числа переменных. Технический результат изобретения заключается в обеспечении возможности коммутации любого информационного входа с любым информационным выходом. Структура содержит матрицу ячеек. Каждая из ячеек соединена с ячейками, соседними по строкам и столбцам.

Недостатком данного устройства является то, что число переключающих элементов структуры при увеличении числа n коммутируемых линий растет пропорционально n2. При больших значениях n реализация коммутационной структуры технически сложна.

Известна коммутационная среда (см. патент РФ №2280891, МПК G06F 15/163). Недостатком данного устройства является то, что число коммутаторов среды быстро растет с увеличением числа коммутируемых линий. При больших значениях n реализация коммутационной структуры технически сложна.

Известна коммутационная сеть для программируемых логических матриц (FPGA) (см. патент US №6940308, МПК H03K 19/173). Данное устройство базируется на коммутационной сети с топологией Бенеша и дает возможность одновременного соединения любого из n входов с любым из n выходов. При этом число переключателей сети растет как nlog2n. Недостатком данного устройства является то, что одна часть выводов сети изначально определяется как входы, другая часть выводов сети определяется как выходы. При этом соединения возможны только для входов с выходами.

Наиболее близким к заявляемому решению является коммутационная сеть (см. патент US №5175539, МПК H04J 3/00).

Коммутационная сеть предназначена для избирательного одновременного соединения каждого из n входов с одним из n выходов. Она имеет входную часть, содержащую входы и имеющую, по крайней мере, k-1 (k=log2n) последовательно соединенных уровней k-уровневой сети baseline, n выходов и выходную часть, в которой n входов соединены с n выходами входной части, включающую k-уровневую сеть baseline и n выходов, которые образуют выходы коммутационной сети.

Недостатком данного устройства также является то, что одна часть выводов сети изначально определяется как входы, другая часть выводов сети определяется как выходы. При этом соединения возможны только для входов с выходами. Кроме этого, входы и выходы данной сети удалены друг от друга. Это затрудняет соединение двух близко расположенных входов и выходов логических элементов, подключаемых к сети, при реализации различных устройств с динамически меняющейся структурой в виде интегральной микросхемы.

Задачей настоящего решения является упрощение конструкции коммутационной матрицы, для обеспечения одновременного электрического соединения каждой из ее n=2k коммутируемых электрических линий попарно между собой.

Техническим результатом является возможность одновременного электрического соединения каждой из n=2k электрических линий матрицы попарно между собой, при этом число переключателей составляет (n/2-l)log2n, а коммутируемые электрические линии расположены с одной стороны матрицы и находятся в непосредственной близости друг от друга.

Поставленная задача достигается тем, что в предлагаемом решении используется односторонняя коммутационная матрица, предназначенная для одновременного управляемого внешними кодами соединения попарно n=2k электрических коммутируемых линий, состоящая из управляемых и неуправляемых переключателей, имеющих 2 порта первой пары, 2 порта второй пары и расположенных по n/2-линиям - строкам и k уровням, причем управляемые переключатели имеют также битовый вход управляющего кода С, и выполнены с возможностью осуществления электрического соединения первого порта первой пары со вторым портом второй пары и второго порта первой пары с первым портом второй пары, или первого порта первой пары с первым портом второй пары и второго порта первой пары со вторым портом второй пары, в зависимости от логического уровня сигнала на входе С, неуправляемые переключатели выполнены с возможностью осуществления фиксированного электрического соединения первого порта первой пары со вторым портом второй пары и второго порта первой пары с первым портом второй пары, или первого порта первой пары с первым портом второй пары и второго порта первой пары со вторым портом второй пары, каждая коммутируемая линия матрицы электрически соединена с одним из портов первой пары первого уровня, каждый из портов первой пары первого уровня электрически соединен с одной коммутируемой линией, каждый порт второй пары каждого переключателя, стоящего на линии i и уровне m матрицы, соединен с одним портом первой пары переключателя, стоящего на следующем уровне m+1 и на линии h, причем , а второй порт второй пары каждого переключателя, стоящего на линии i и уровне m матрицы, соединен с одним портом первой пары переключателя, стоящего на следующем уровне m+1 и на линии p, причем

где int - функция выделения целой части, - операция вычисления остатка от частного , при этом каждый порт первой пары каждого переключателя уровня m+1 соединен с одним портом первой пары переключателя предыдущего уровня m, один из переключателей каждого уровня m<k матрицы неуправляемый, каждый из портов второй пары каждого переключателя уровня k электрически соединен с одним из портов второй пары другого переключателя уровня k, причем для каждой пары Trk, Tpk соединенных таким образом переключателей, расположенных на строках с номерами r и p, справедливо

r-p=±2q-l+xq-12q-2+xg-22q-3+…+x120, где x1 - произвольные коэффициенты из множества {-1,0,1} или r+p=2q-1+yq-12q-2+yq-22q-3+…+y120, где y1 - произвольные коэффициенты из множества {0,1,2}.

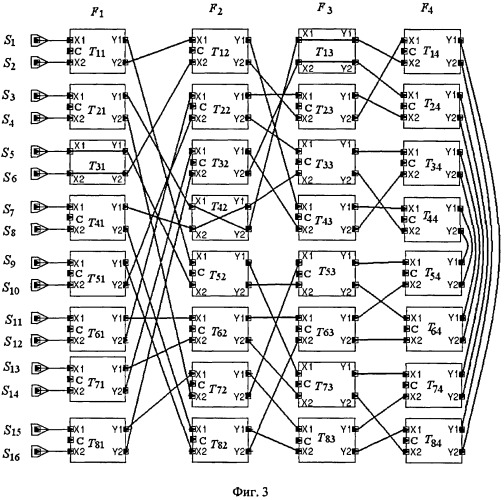

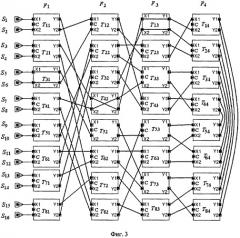

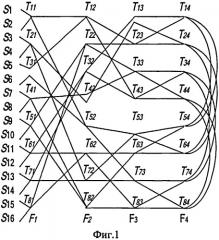

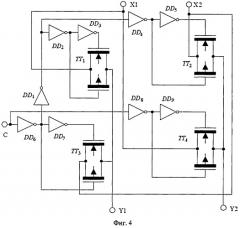

Изобретение поясняется чертежами, где на фиг.1, фиг.2 приведены диаграммы орграфов, иллюстрирующих варианты соединений переключателей, образующих матрицу для случая n=16, на фиг.3 приведена схема матрицы для случая n=16, на фиг.4 приведена схема переключателя матрицы, где

- F1, F2, F3, F4 - коммутационные уровни матрицы;

- S1-S16 - электрические коммутируемые линии матрицы;

- С - вход управляющего кода переключателя матрицы;

- X1, Х2 - первая пара портов переключателей;

- Y1, Y2 - вторая пара портов переключателей;

- DD1…DD9 - усилители-инверторы управляющего сигнала на входе С;

- ТТ1…ТТ4 электронные ключи на КМОП транзисторах.

Матрица имеет n электрических коммутируемых линий данных и битовые входы управляющих кодов. Матрица состоит из управляемых и неуправляемых переключателей где , k=log2n. Каждый переключатель имеет первую пару портов X1, X2, вторую пару портов Y1, Y2, причем управляемые переключатели имеют также вход управляющего кода С, который принимает значения логического нуля или единицы. Каждый переключатель выполнен с возможностью электрического соединения либо первого порта первой пары с первым портом второй пары, а второго порта первой пары со вторым портом второй пары, либо первого порта первой пары с вторым портом второй пары, а второго порта первой пары с первым портом второй пары, в зависимости от логического уровня на входе С. Неуправляемые переключатели осуществляют фиксированное электрическое соединение первого порта первой пары с первым портом второй пары, а второго порта первой пары со вторым портом второй пары, или первого порта первой пары со вторым портом второй пары, а второго порта первой пары с первым портом второй пары. Для реализации переключателей используются известные решения. В качестве одного из вариантов может использоваться схема, состоящая из четырех двунаправленных ключей на КМОП транзисторах, приведенная на фиг.4. Данная схема построена на базе четырехканального коммутатора К561КТЗ (Шило В.Л. Популярные цифровые микросхемы: Справочник. - М.: Радио и связь, 1987, с.228, 229).

Если сигнал на входе С положительный, открыты ключи на транзисторах ТТ3, ТТ4, и переключатель осуществляет электрическое соединение первого порта первой пары со вторым портом второй пары, и второго порта первой пары с первым портом второй пары. Если сигнал на входе С имеет нулевой уровень, то открыты ключи на транзисторах ТТ1, TT2 и переключатель осуществляет электрическое соединение первого порта первой пары и первого порта второй пары, а также торого порта первой пары и второго порта второй пары.

Переключатели образуют матрицу с n/2-линиями и k коммутационными уровнями F1,…,Fk. Входы управляющих кодов матрицы образованы входами кодов переключателей С. Каждая коммутируемая линия матрицы имеет электрическое соединение с одним портом первых пар переключателей Тi1 первого уровня. Каждый порт первой пары каждого переключателя Тi1 первого уровня имеет электрическое соединение с одной коммутируемой линией матрицы. Каждый переключатель Tim уровня матрицы через порты второй пары соединен с портами первой пары переключателей Thm+1, Tpm+1 уровня m+1. Причем ,

где

int - функция выделения целой части, - операция вычисления остатка от частного .

Один из переключателей матрицы уровня m<k неуправляемый.

Каждый из портов второй пары каждого переключателя уровня k электрически соединен с одним из портов второй пары другого переключателя уровня k, причем для каждой пары Trk, Tpk соединенных таким образом переключателей справедливо

r-p=±2k-l+xk-12k-2+xk-22k-3+…+x120, где x1 - произвольные коэффициенты из множества {-1,0,1}, xi∈{-1,0,1}, или r+p=2k-1+yk-12k-2+yk-22k-3+…+y120, где y1 - произвольные коэффициенты из множества {0,1,2}, yi∈{0,1,2}.

На фиг.1, 2 представлены варианты соединений переключателей матрицы, удовлетворяющие приведенным выше условиям для случая n=16. Диаграмма графа на фиг.1 соответствует случаю |r-p|=2k-1, коэффициенты xi=0 для любого значения i. Диаграмма графа на фиг.2 соответствует случаю r+p=2k-1, коэффициенты yi=0 для любого значения i. Матрица имеет 4 уровня F1, F2, F3, F4. Переключатели первого уровня одним портом второй пары соединены с произвольным портом первой пары любого переключателя из верхней половины переключателей второго уровня, а вторым портом второй пары соединены с произвольным портом первой пары любого переключателя из нижней половины переключателей второго уровня. Каждый порт переключателей второго уровня соединен с любым портом первой пары любого переключателя из верхней четверти переключателей третьего уровня, а вторым портом второй пары соединен с любым портом первой пары любого переключателя из нижней четверти переключателей третьего уровня и т.д. На каждом уровне с номером меньше k один неуправляемый переключатель. На первом уровне T31, на втором уровне Т32, на третьем уровне Т13.

Каждый порт первой пары переключателей m+1 уровня соединен с одним портом второй пары переключателей m уровня. Каждый порт второй пары переключателей уровня m соединен с одним портом первой пары переключателей уровня m+1.

Устройство работает следующим образом.

На коммутируемые линии матрицы подаются сигналы. На входы С переключателей подаются управляющие коды. Соединение заданных линий выполняется за время τ·log2n, где τ - задержка сигнала на одном переключателе.

Таким образом, с использованием односторонней коммутационной матрицы реализуется одновременное управляемое соединение n электрических линий попарно. Число переключателей матрицы составляет (n/2-1)·log2(n)+1 и растет практически линейно с ростом n, что делает технически возможным коммутацию большого числа электрических линий. Число возможных различных парных соединений, осуществляемых данной матрицей, составляет . Предложенная матрица имеет в два раза меньшее число переключателей по сравнению с коммутационной сетью с топологией Бенеша. Коммутируемые линии находятся с одной стороны матрицы и располагаются в непосредственной близости друг от друга. В предложенной коммутационной матрице соединения между уровнями заданы не жестко, что дает возможность их изменения, например, для оптимизации топологии матрицы.

Односторонняя коммутационная матрица, предназначенная для одновременного управляемого внешними кодами соединения попарно n=2k электрических коммутируемых линий, состоящая из управляемых и неуправляемых переключателей, имеющих 2 порта первой пары, 2 порта второй пары и расположенных по n/2-линиям - строкам и k уровням, причем управляемые переключатели имеют также битовый вход управляющего кода С, и выполнены с возможностью осуществления электрического соединения первого порта первой пары со вторым портом второй пары и второго порта первой пары с первым портом второй пары, или первого порта первой пары с первым портом второй пары и второго порта первой пары со вторым портом второй пары, в зависимости от логического уровня сигнала на входе С, неуправляемые переключатели выполнены с возможностью осуществления фиксированного электрического соединения первого порта первой пары со вторым портом второй пары и второго порта первой пары с первым портом второй пары, или первого порта первой пары с первым портом второй пары и второго порта первой пары со вторым портом второй пары, каждая коммутируемая линия матрицы электрически соединена с одним из портов первой пары первого уровня, каждый из портов первой пары первого уровня электрически соединен с одной коммутируемой линией, каждый порт второй пары каждого переключателя, стоящего на линии i и уровне m матрицы соединен с одним портом первой пары переключателя стоящего на следующем уровне m+1 и на линии h, причем , а второй порт второй пары каждого переключателя, стоящего на линии i и уровне m матрицы соединен с одним портом первой пары переключателя стоящего на следующем уровне m+1 и на линии р, причем где int - функция выделения целой части, - операция вычисления остатка от частного , при этом каждый порт первой пары каждого переключателя уровня m+1 соединен с одним портом первой пары переключателя предыдущего уровня m, один из переключателей каждого уровня m<k электрически соединен с одним из портов второй пары другого переключателя уровня k, причем для каждой пары, соединенных таким образом переключателей, расположенных на строках с номерами r и p справедливо r-p=±2q-l+xq-12q-2+xg-22q-3+…+x120, где x1 - произвольные коэффициенты из множества {-1,0,1} или r+p=2q-1+yq-12q-2+yq-22q-3+…+y120, где у1 - произвольные коэффициенты из множества {0,1,2}.