Каскодный дифференциальный операционный усилитель с малым напряжением смещения нуля и повышенным коэффициентом усиления

Иллюстрации

Показать всеИзобретение относится к области радиотехники и связи и может быть использовано в качестве устройства усиления аналоговых сигналов, в структуре аналоговых микросхем различного функционального назначения (например, операционных усилителях с повышенным коэффициентом усиления по напряжению и малым смещением нуля). Технический результат: уменьшение э.д.с. смещения нуля (Uсм) при одновременном повышении коэффициента усиления по напряжению разомкнутого ДУ (Ку). Каскодный дифференциальный операционный усилитель содержит входной дифференциальный каскад (1) с первым (2) и вторым (3) коллекторными выходами, первый коллекторный выход (2) соединен с эмиттером первого (4) выходного транзистора, второй (3) коллекторный выход соединен с эмиттером второго (5) выходного транзистора, эмиттеры первого (4) и второго (5) выходных транзисторов через соответствующие первый (6) и второй (7) токостабилизирующие двухполюсники связаны с первой (8) шиной источника питания, цепь смещения потенциалов (9), связанную с объединенными базами первого (4) и второго (5) выходных транзисторов, первое (10) токовое зеркало, вход которого подключен к коллектору второго (5) выходного транзистора, а выход соединен с коллектором первого (4) выходного транзистора и базой третьего (11) выходного транзистора, коллектор третьего (11) выходного транзистора соединен с выходом устройства (12) и через третий (13) токостабилизирующий двухполюсник соединен с первой (8) шиной источника питания, вторую (14) шину источника питания, соединенную с общим эмиттерным выходом первого (10) токового зеркала, входным дифференциальным каскадом (1) и эмиттером третьего (11) выходного транзистора. В схему введены второе (15) токовое зеркало, а также первый (16) и второй (17) дополнительные транзисторы, база первого (16) дополнительного транзистора подключена к базе третьего (11) выходного транзистора, его эмиттер соединен со второй (14) шиной источника питания, коллектор первого (16) дополнительного транзистора связан со входом второго (15) токового зеркала, общий эмиттерный выход второго (15) токового зеркала соединен с эмиттером второго (17) дополнительного транзистора, выход второго (15) токового зеркала подключен ко второй (14) шине источника питания, база второго (17) дополнительного транзистора соединена со вторым (3) коллекторным выходом входного дифференциального каскада (1), а коллектор второго (17) дополнительного транзистора подключен к первой (8) шине источника питания. 6 ил.

Реферат

Изобретение относится к области радиотехники и связи и может быть использовано в качестве устройства усиления аналоговых сигналов, в структуре аналоговых микросхем различного функционального назначения (например, операционных усилителях с повышенным коэффициентом усиления по напряжению и малым смещения нуля).

Известны схемы так называемых «перегнутых» каскодных дифференциальных усилителей (ДУ) на n-p-n и p-n-p транзисторах [1-35], которые стали основой более чем 20 серийных операционных усилителей, выпускаемых как зарубежными (НА2520, НА5190, AD797, AD8631, AD8632, ОР90 и др.), так и российскими (154УД3 и др.) микроэлектронными фирмами. В связи с высокой популярностью такой архитектуры ДУ на их модификации выдано более 100 патентов. Предполагаемое изобретение относится к данному подклассу устройств.

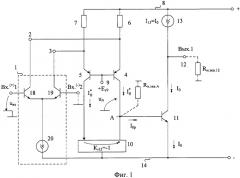

Ближайшим прототипом (фиг.1) заявляемого устройства является дифференциальный операционный усилитель, описанный в патенте США фирмы National Semiconductor №6.788.143, fig.2, содержащий входной дифференциальный каскад 1 с первым 2 и вторым 3 коллекторными выходами, первый коллекторный выход 2 соединен с эмиттером первого 4 выходного транзистора, второй 3 коллекторный выход соединен с эмиттером второго 5 выходного транзистора, эмиттеры первого 4 и второго 5 выходных транзисторов через соответствующие первый 6 и второй 7 токостабилизирующие двухполюсники связаны с первой 8 шиной источника питания, цепь смещения потенциалов 9, связанную с объединенными базами первого 4 и второго 5 выходных транзисторов, первое 10 токовое зеркало, вход которого подключен к коллектору второго 5 выходного транзистора, а выход соединен с коллектором первого 4 выходного транзистора и базой третьего 11 выходного транзистора, коллектор третьего 11 выходного транзистора соединен с выходом устройства 12 и через третий 13 токостабилизирующий двухполюсник соединен с первой 8 шиной источника питания, вторую 14 шину источника питания, соединенную с общим эмиттерным выходом первого 10 токового зеркала, входным дифференциальным каскадом 1 и эмиттером третьего 11 выходного транзистора.

Существенный недостаток известного ДУ (фиг.1) состоит в том, что он имеет сравнительно большое значение э.д.с. смещения нуля, что отрицательно сказывается на статических параметрах различных аналоговых устройств на его основе, а также невысокий коэффициент усиления по напряжению Ку, влияющий на параметры аналоговых интерфейсов в схемах с отрицательной обратной связью.

Основная задача предполагаемого изобретения состоит в уменьшении э.д.с. смещения нуля (Uсм) при одновременном повышении коэффициента усиления по напряжению разомкнутого ДУ (Ку).

Поставленная задача решается тем, что в дифференциальном усилителе фиг.1, содержащем входной дифференциальный каскад 1 с первым 2 и вторым 3 коллекторными выходами, первый коллекторный выход 2 соединен с эмиттером первого 4 выходного транзистора, второй 3 коллекторный выход соединен с эмиттером второго 5 выходного транзистора, эмиттеры первого 4 и второго 5 выходных транзисторов через соответствующие первый 6 и второй 7 токостабилизирующие двухполюсники связаны с первой 8 шиной источника питания, цепь смещения потенциалов 9, связанную с объединенными базами первого 4 и второго 5 выходных транзисторов, первое 10 токовое зеркало, вход которого подключен к коллектору второго 5 выходного транзистора, а выход соединен с коллектором первого 4 выходного транзистора и базой третьего 11 выходного транзистора, коллектор третьего 11 выходного транзистора соединен с выходом устройства 12 и через третий 13 токостабилизирующий двухполюсник соединен с первой 8 шиной источника питания, вторую 14 шину источника питания, соединенную с общим эмиттерным выходом первого 10 токового зеркала, входным дифференциальным каскадом 1 и эмиттером третьего 11 выходного транзистора, предусмотрены новые элементы и связи - в схему введены второе 15 токовое зеркало, а также первый 16 и второй 17 дополнительные транзисторы, база первого 16 дополнительного транзистора подключена к базе третьего 11 выходного транзистора, его эмиттер соединен со второй 14 шиной источника питания, коллектор первого 16 дополнительного транзистора связан со входом второго 15 токового зеркала, общий эмиттерный выход второго 15 токового зеркала соединен с эмиттером второго 17 дополнительного транзистора, выход второго 15 токового зеркала подключен ко второй 14 шине источника питания, база второго 17 дополнительного транзистора соединена со вторым 3 коллекторным выходом входного дифференциального каскада 1, а коллектор второго 17 дополнительного транзистора подключен к первой 8 шине источника питания.

Схема усилителя-прототипа представлена на фиг.1.

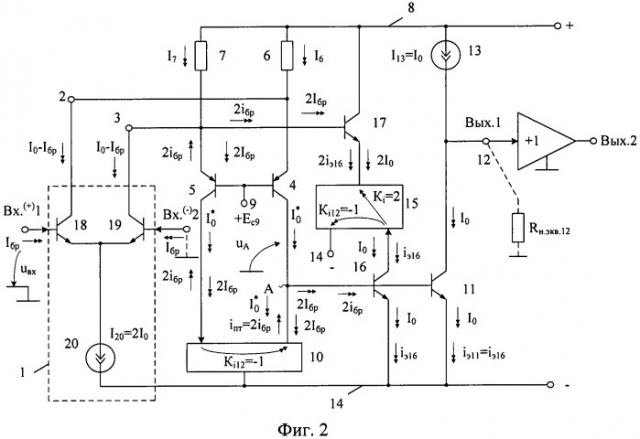

На фиг.2 представлена схема заявляемого устройства в соответствии с формулой изобретения.

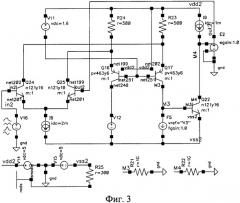

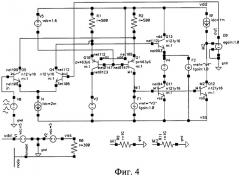

На фиг.3 и фиг.4 показаны схемы известного (фиг.3) и заявляемого (фиг.4) устройств в среде компьютерного моделирования Cadance на моделях HJW, а на фиг.5 - зависимость напряжения смещения нуля (Uсм) сравниваемых схем фиг.3 и фиг.4 от температуры.

На фиг.6 показаны амплитудно-частотные характеристики сравниваемых схем фиг.3 и фиг.4

Дифференциальный усилитель фиг.2 содержит входной дифференциальный каскад 1 с первым 2 и вторым 3 коллекторными выходами, первый коллекторный выход 2 соединен с эмиттером первого 4 выходного транзистора, второй 3 коллекторный выход соединен с эмиттером второго 5 выходного транзистора, эмиттеры первого 4 и второго 5 выходных транзисторов через соответствующие первый 6 и второй 7 токостабилизирующие двухполюсники связаны с первой 8 шиной источника питания, цепь смещения потенциалов 9, связанную с объединенными базами первого 4 и второго 5 выходных транзисторов, первое 10 токовое зеркало, вход которого подключен к коллектору второго 5 выходного транзистора, а выход соединен с коллектором первого 4 выходного транзистора и базой третьего 11 выходного транзистора, коллектор третьего 11 выходного транзистора соединен с выходом устройства 12 и через третий 13 токостабилизирующий двухполюсник соединен с первой 8 шиной источника питания, вторую 14 шину источника питания, соединенную с общим эмиттерным выходом первого 10 токового зеркала, входным дифференциальным каскадом 1 и эмиттером третьего 11 выходного транзистора. В схему введены второе 15 токовое зеркало, а также первый 16 и второй 17 дополнительные транзисторы, база первого 16 дополнительного транзистора подключена к базе третьего 11 выходного транзистора, его эмиттер соединен со второй 14 шиной источника питания, коллектор первого 16 дополнительного транзистора связан со входом второго 15 токового зеркала, общий эмиттерный выход второго 15 токового зеркала соединен с эмиттером второго 17 дополнительного транзистора, выход второго 15 токового зеркала подключен ко второй 14 шине источника питания, база второго 17 дополнительного транзистора соединена со вторым 3 коллекторным выходом входного дифференциального каскада 1, а коллектор второго 17 дополнительного транзистора подключен к первой 8 шине источника питания. В частном случае входной дифференциальный каскад содержит входные транзисторы 18 и 19, а также источник тока 20. В ряде вариантов применения к выходу устройства 12 может подключать буферный каскад 21. В качестве первого 10 и второго 15 токовых зеркал могут применяться токовые зеркала Вильсона (10), а также более простые варианты их построения (15), описанные в технической литературе.

Рассмотрим работу заявляемого дифференциального усилителя фиг.2 в начале на постоянном токе (определим его напряжение смещения нуля Uсм).

Статический режим по току ДУ фиг.2 устанавливается источником опорного тока 20 I20=2I0 в эмиттерной цепи входного дифференциального каскада 1 и токостабилизирующими двухполюсниками 6, 7 и 13. При этом токи в элементах схемы, соответствующие обозначениям на фиг.2:

где

- коллекторный ток транзисторов 4 и 5 в ДУ фиг.2 без транзистора 17 (т.е. в схеме ДУ-прототипа);

Iэij, Iкij - эмиттерные и коллекторные токи транзисторов схемы фиг.2;

I6, I7 - статические токи двухполюсников 6 и 7;

I20=2I0 - статический ток общей эмиттерной цепи входного дифференциального каскада 1;

βр - статический коэффициент передачи по току базы n-p-n транзисторов схемы фиг.2;

Iвх.пт.10, Iвых.пт.10 - входной и выходной токи токового зеркала 10;

Iбр=I0/βp - ток базы p-n-p транзисторов схемы фиг.2 при Iэ=I0.

Сумма статических токов в узле А, определяющая напряжение смещения нуля:

Подставляя (1)-(7) в (8) можно найти, что в заявляемом ДУ ток Iр=0, что уменьшает Uсм более чем на порядок.

Действительно, компьютерное моделирование показывает, что в схеме ДУ-прототипа систематическая составляющая напряжения смещения нуля принимает достаточно большое значение: Uсм.п=0,726 мВ (фиг.5).

В заявляемом устройстве численные значения Uсм=58,9 мкВ.

Следовательно, в схеме фиг.2 созданы условия, при которых устраняется систематическая ошибка усиления сигналов постоянного тока, обусловленная структурными особенностями ДУ. Это позволяет рекомендовать заявляемую схему для применения в составе прецизионных интерфейсов.

Рассмотрим далее факторы, определяющие коэффициент усиления по напряжению (Ку) ДУ фиг.2 и фиг.1 без обратной связи.

В схеме фиг.1 общий коэффициент усиления по напряжению определяется произведением КуΣ=Ку1Ку2,

где - коэффициент усиления по напряжению ДУ со входа Вx.(+)1 до узла «А»;

RН.экв.А - эквивалентное выходное сопротивление узла «А»;

- коэффициент усиления по напряжению от узла «А» до выхода Вых.1;

RН.экв.12 - эквивалентное сопротивление нагрузки в узле 12 ДУ фиг.1;

rэj - эмиттерное сопротивление j-го транзистора.

Эквивалентное выходное сопротивление узла «А» определяется, в основном, входным сопротивлением транзистора 11:

где β11=50÷100 - коэффициент усиления по току базы транзистора 11;

rэ.11=25÷50 Ом - сопротивление эмиттерного перехода транзистора 11.

Таким образом, общий КуΣ усилителя-прототипа:

В заявляемой схеме фиг.2:

где Кi=2 - коэффициент передачи по току токового зеркала 15 со входа в общий эмиттерный выход;

Ki12.10 - коэффициент усиления по току токового зеркала 10.

Таким образом, в заявляемой схеме:

где α5≈1 - коэффициент усиления по току эмиттера транзистора 5.

При этом выигрыш по КуΣ, который дает предлагаемое техническое решение:

Данные выводные подтверждаются результатами компьютерного моделирования (фиг.6). Выигрыш по Ку - 44 дБ, т.е. более чем на два порядка.

Следует заметить, что схема фиг.2 может иметь так называемый Raie-to-raie выход 12 (без буферного усилителя 21), что весьма перспективно для микросхем с малым напряжением питания.

Источники информации

1. Матавкин В.В. Быстродействующие операционные усилители. - М.: Радио и связь, 1989. - с.74, рис.4.15, стр.98, рис.6.7.

2. Патент США №6.218.900, фиг.1.

3. Патентная заявка US 2002/0196079.

4. Патент США №6.788.143.

5. Патент США №3.644.838, фиг.2.

6. Патент США Re 30.587.

7. Патент ЕР 1.227.580.

8. Патент США №6.714.076.

9. Патент США №5.786.729.

10. Патент США №5.327.100.

11. Патентная заявка US 2004/0090268A1.

12. Патент США №4.274.061.

13. Патент США №5.422.600, фиг.2.

14. Патент США №6.788.143, фиг.2.

15. Патент США №4.959.622, фиг.1.

16. Патент США №4.406.990, фиг.4.

17. Патент США №5.418.491.

18. Патент США №6.018.268.

19. Патент США №5.952.882.

20. Патент США №4.723. 111.

21. Патент США №4.293.824.

22. Патент США №6.580.325.

23. Патент США №6.965.266.

24. Патент США №6.867.643.

25. Патент США №6.236.270.

26. Патент США №5.323.121.

27. Патент США №6.229.394.

28. Патент США №5.734.296.

29. Патент США №5.477.190.

30. Патент США №5.091.701.

31. Патент США №6.717.474.

32. Патент США №6.084.475.

33. Патент США №3.733.559.

34. Патентная заявка US 2005/0001682A1.

35. Патент США №6.300.831.

Каскодный дифференциальный операционный усилитель с малым напряжением смещения нуля и повышенным коэффициентом усиления, содержащий входной дифференциальный каскад (1) с первым (2) и вторым (3) коллекторными выходами, первый коллекторный выход (2) соединен с эмиттером первого (4) выходного транзистора, второй (3) коллекторный выход соединен с эмиттером второго (5) выходного транзистора, эмиттеры первого (4) и второго (5) выходных транзисторов через соответствующие первый (6) и второй (7) токостабилизирующие двухполюсники связаны с первой (8) шиной источника питания, цепь смещения потенциалов (9), связанную с объединенными базами первого (4) и второго (5) выходных транзисторов, первое (10) токовое зеркало, вход которого подключен к коллектору второго (5) выходного транзистора, а выход соединен с коллектором первого (4) выходного транзистора и базой третьего (11) выходного транзистора, коллектор третьего (11) выходного транзистора соединен с выходом устройства (12) и через третий (13) токостабилизирующий двухполюсник соединен с первой (8) шиной источника питания, вторую (14) шину источника питания, соединенную с общим эмиттерным выходом первого (10) токового зеркала, входным дифференциальным каскадом (1) и эмиттером третьего (11) выходного транзистора, отличающийся тем, что в схему введены второе (15) токовое зеркало, а также первый (16) и второй (17) дополнительные транзисторы, база первого (16) дополнительного транзистора подключена к базе третьего (11) выходного транзистора, его эмиттер соединен со второй (14) шиной источника питания, коллектор первого (16) дополнительного транзистора связан со входом второго (15) токового зеркала, общий эмиттерный выход второго (15) токового зеркала соединен с эмиттером второго (17) дополнительного транзистора, выход второго (15) токового зеркала подключен ко второй (14) шине источника питания, база второго (17) дополнительного транзистора соединена со вторым (3) коллекторным выходом входного дифференциального каскада (1), а коллектор второго (17) дополнительного транзистора подключен к первой (8) шине источника питания.