Способ и устройство для установки политики кэширования в процессоре

Иллюстрации

Показать всеИзобретение относится к операциям кэширования в процессоре, в частности относится к определению политики кэширования. Техническим результатом является улучшение производительности процессора с помощью определения политики кэширования для текущей операции памяти, основываясь на информации о политике кэширования, связанной с целевым запоминающим устройством, к которому обращаются во время определенной операции памяти. Согласно способам и устройству, раскрытым в данном документе, политики кэширования процессора определяются, используя информацию о политике кэширования, связанной с целевым запоминающим устройством, к которому обращаются во время операций с памятью. Согласно одному из вариантов осуществления процессора процессор содержит по меньшей мере одну кэш-память и блок управления памятью. По меньшей мере одну кэш-память выполняют с возможностью хранения информации, локальной для процессора. Блок управления памятью выполняют с возможностью установки одной или более политик кэширования по меньшей мере для одной кэш-памяти. Блок управления памятью устанавливает одну или более политик кэширования, основываясь на информации о политике кэширования, связанной с одним или более целевых запоминающих устройств, выполненных с возможностью хранения информации, используемой процессором. 6 н. и 17 з.п. ф-лы, 7 ил.

Реферат

УРОВЕНЬ ТЕХНИКИ

Область техники, к которой относится изобретение

Настоящее изобретение в общем относится к операциям кэширования в процессоре, в частности относится к определению политики кэширования.

Предшествующий уровень техники

Производительность процессора улучшают с помощью того, что процессор локально включает в себя кэш-память одного или большего количества уровней для хранения информации, к которой часто обращаются, или последней по времени использования информации. Кэш-память процессора - небольшая, быстродействующая память, в которой хранят копию выбранной информации, хранящейся в оперативной памяти, такой как DRAM (динамическое оперативное запоминающее устройство) или накопитель на жестких дисках. Когда команда обращается к ячейке памяти, процессор сначала проверяет, скопирована ли данная ячейка памяти в локальную кэш-память. В частности, адрес, связанный с памятью, к которой обращаются, сравнивают со всеми тэгами (дескрипторами) в кэш-памяти. Если необходимая память расположена в кэш-памяти, то происходит удачное обращение в кэш-память. Иначе, происходит неудачное обращение в кэш-память.

Когда происходит удачное обращение в кэш-память, процессор немедленно считывает или записывает информацию, такую как данные или команды, из или в идентифицированную строку кэш-памяти. В случае неудачного обращения в кэш-память необходимую информацию извлекают из кэш-памяти более высокого уровня или из оперативной памяти. Кроме того, новую запись традиционно выделяют в кэш-памяти для хранения недавно извлеченной информации. Новая запись содержит тэг, идентифицирующий адрес, который вызвал неудачное обращение в кэш-память, и копию информации, извлеченной от оперативной памяти.

Для размещения новой записи кэш-памяти существующую запись удаляют из кэш-памяти. Эвристический алгоритм, используемый для выбора записи для удаления из кэш-памяти, основан на политике замещения, такой как замещение наиболее давно не используемой записи или «первым пришел - первым ушел». Другие политики кэширования (также называемые параметрами кэширования) также используются для определения, как к кэш-памяти обращаются, как ее используют и обслуживают. Другие политики кэширования включают в себя политики записи, политики выделения, политики уровня кэширования и настраиваемые политики.

Политики записи определяют, когда информацию, записываемую в блок данных кэш-памяти, также записывают в оперативную память. Например, кэш-память и оперативную память обновляют одновременно, когда используют политику с прямой записью. Когда используют политику с обратной записью, оперативную память обновляют только тогда, когда соответствующий блок данных кэш-памяти заменяют. При политике с однократной записью используют политику с прямой записью для первой записи в определенный блок данных кэш-памяти и политику с обратной записью для последующей записи в тот же самый блок.

Политика выделения кэш-памяти определяет, когда записывают блок данных кэш-памяти. Например, если политикой выделения, связанной с определенным блоком данных кэш-памяти, является «выделить только для чтения», то данный блок не затрагивают во время записи. Наоборот, блок данных кэш-памяти обновляют и во время записи, и во время считывания, когда политикой выделения является «выделить для чтения и записи». Для процессоров, имеющих множество уровней кэш-памяти, таких как кэш-память команд и данных первого уровня и по меньшей мере одна кэш-память более высокого уровня, политика уровня кэш-памяти определяет, какой уровень кэш-памяти используется для хранения информации. Например, команды можно хранить в кэш-памяти команд первого уровня, в то время как другую информацию можно хранить только в кэш-памяти второго уровня.

Политики кэширования традиционно хранят в таблице страниц. Таблицу страниц хранят в оперативной памяти, причем записи, к которым часто обращаются, или последние по времени использования записи хранят локально в процессоре, например в буфере быстрого преобразования адреса (TLB). Каждая запись таблицы страниц отображает виртуальный адрес на соответствующий физический адрес. В частности, таблица страниц хранит список виртуальных номеров страниц и соответствующих физических номеров страниц. Виртуальные номера страниц идентифицируют соответствующие блоки виртуальной памяти, выделенные процессам, работающим на процессоре, в то время как физические номера страниц идентифицируют соответствующие блоки физической памяти, содержащие фактическую информацию, используемую процессами.

Когда процессор обращается к определенной ячейке памяти, записи таблицы страниц ищут, используя часть виртуального адреса, которая является виртуальным номером страницы, обеспечиваемого как часть обращения. Физический номер страницы извлекают из соответствующей записи таблицы страниц. Физический номер страницы и смещение страницы формируют физический адрес, который используют для обращения к необходимой ячейке памяти.

Если необходимая ячейка памяти не содержится в пределах локальной кэш-памяти процессора, то обращаются к оперативной памяти. Информация о политике кэширования, хранящаяся в соответствующей записи таблицы страниц, определяет, сохраняют ли локально в кэш-памяти информацию, считываемую из оперативной памяти или записываемую в оперативную память как часть обращения к памяти, и если да, то как данную информацию обслуживают в кэш-памяти. Таким образом, политику кэширования традиционно устанавливают и применяют к кэш-памяти на постраничной (или поблочной) основе. Дополнительно, политики кэширования традиционно программируют с помощью операционной системы. Также, политику кэширования применяют в общем случае ко всем процессам, работающим на процессоре, и они могут привести к неэффективности, когда используется определенным типом устройств оперативной памяти. Например, политика выделения кэш-памяти «выделить только для чтения» может оптимизировать использование кэш-памяти для некоторых процессов, таких как прикладные программы работы с графикой, но не других.

СУЩНОСТЬ ИЗОБРЕТЕНИЯ

Согласно раскрытым способам и устройству политики кэширования процессора определяют, используя информацию о политике кэширования, связанной с целевым запоминающим устройством, к которому обращаются во время определенной операции памяти. Таким образом, операции кэширования можно настраивать для определенных параметров настройки запоминающих устройств вместо общих параметров настройки политики кэширования. Производительность процессора улучшают с помощью определения политики кэширования для текущей операции памяти, основываясь на информации о политике кэширования, связанной с целевым запоминающим устройством, к которому обращаются во время операции памяти.

Согласно одному из вариантов осуществления процессора процессор содержит по меньшей мере одну кэш-память и блок управления памятью. По меньшей мере одну кэш-память выполняют с возможностью хранения информации, локальной для процессора. Блок управления памятью выполняют с возможностью установки одной или большего количества политик кэширования по меньшей мере для одной кэш-памяти. Блок управления памятью устанавливает одну или большее количество политик кэширования, основываясь на информации о политике кэширования, связанной с одним или большим количеством целевых запоминающих устройств, выполненных с возможностью хранения информации, используемой процессором.

Согласно одному из вариантов осуществления системы система содержит процессор, имеющий по меньшей мере одну кэш-память, выполненную с возможностью хранения информации, локальной для процессора, одно или большее количество целевых запоминающих устройств, связанных с процессором, и блок управления памятью, который включает в себя процессор. Одно или большее количество целевых запоминающих устройств выполняют с возможностью для хранения информации, используемой процессором. Блок управления памятью выполняют с возможностью установки одной или большего количества политик кэширования по меньшей мере для одной кэш-памяти, основываясь на информации о политике кэширования, связанной с одним или большим количеством целевых запоминающих устройств.

Конечно, настоящее изобретение не ограничено указанными выше особенностями и преимуществами. Специалисты узнают дополнительные особенности и преимущества после чтения последующего подробного описания и после рассмотрения сопроводительных чертежей.

КРАТКОЕ ОПИСАНИЕ ЧЕРТЕЖЕЙ

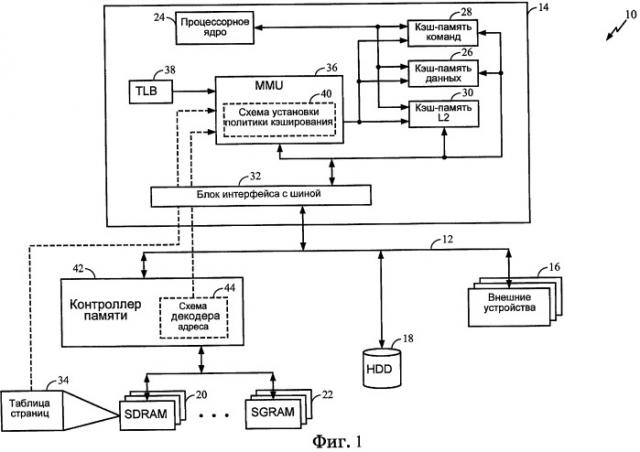

Фиг. 1 - структурная схема, показывающая вариант осуществления системы, включающей в себя процессор, имеющий схему для определения политики кэширования.

Фиг. 2 - структурная схема, показывающая вариант осуществления схемы декодера адреса для обеспечения информации о политике кэширования, связанной с запоминающим устройством.

Фиг. 3 - структурная схема, показывающая другой вариант осуществления системы, включающей в себя процессор, имеющий схему для определения политики кэширования.

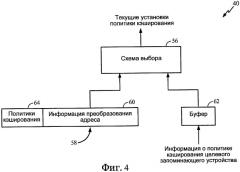

Фиг. 4 - структурная схема, показывающая вариант осуществления схемы для определения политики кэширования в процессоре.

Фиг. 5 - логическая последовательность операций, показывающая вариант осуществления логики программы для определения политики кэширования в процессоре.

Фиг. 6 - схема, иллюстрирующая, как схема на фиг. 4 определяет политику кэширования в ответ на примерную операцию записи.

Фиг. 7 - схема, иллюстрирующая, как схема на фиг. 4 определяет политику кэширования в ответ на примерную операцию чтения.

ПОДРОБНОЕ ОПИСАНИЕ

Фиг. 1 показывает вариант осуществления системы 10, включающей в себя шину 12, связывающую процессор 14 с одним или большим количеством периферийных устройств 16 и оперативной памятью, такой как накопитель на жестких дисках (HDD) 18, и DRAM, такое как синхронное DRAM (SDRAM) 20 и синхронное графическое RAM (SGRAM) 22. Процессор 14 включает в себя процессорное ядро 24, кэш-память 26, 28 данных и команд, кэш-память 30 второго уровня (L2) и блок 32 интерфейса с шиной. Процессорное ядро 24 обеспечивает централизованное управление потоком команд и выполнением команд. Кэш-память 26, 28 данных и команд хранит данные и команды, соответственно. Кэш-память 30 L2 обеспечивает высокоскоростной буфер памяти между кэш-памятью 26, 28 данных и команд и оперативной памятью, внешней по отношению к процессору 14, такой как HDD 18, DRAM 20 и SGRAM 22. Блок 32 интерфейса с шиной обеспечивает механизм для передачи данных, команд, адреса и управляющих сигналов между процессором 14 и устройствами, внешними для процессора 14, такими как периферийные устройства 16 и оперативная память 18, 20, 22.

Оперативная память 18, 20, 22 представлена как виртуальная память для процессов, работающих на процессоре 14. Таким образом, страницы физической памяти выделяют как виртуальную память для использования процессами во время выполнения программы. Таблица 34 страниц хранится в оперативной памяти 18, 20, 22, например, как показано на фиг. 1, для предоставления возможности отображения между виртуальными и физическими адресными пространствами. Блок 36 управления памятью (MMU), который включает в себя процессор 14, обращается к таблице 34 страниц и обрабатывает обращения к памяти, выдаваемые процессором 14, которые включают в себя управление виртуальной памятью, защиту памяти, управление кэш-памятью и арбитраж доступа к шине. Как часть управления виртуальной памятью, MMU 36 хранит записи таблицы страниц (PTE), которые часто используются или к которым недавно обращались, локально на процессоре 14, например в буфере 38 быстрого преобразования адреса (TLB).

Когда процессор 14 обращается к необходимой ячейке памяти, идентифицированной виртуальным адресом, MMU 36 обращается к TLB 38 для определения, содержит ли TLB 38 соответствующую запись. Если да, то виртуальный адрес преобразовывают в физический адрес, используя информацию преобразования адреса, хранящуюся в соответствующей записи TLB. Иначе, таблица 34 страниц ищет соответствующую запись. Любым способом MMU 36 инициирует операцию поиска кэш-памяти в одной из помеченных физическим тегом разновидностей кэш-памяти 26, 28, 30, основываясь на результирующем физическом адресе. Если одна из разновидностей кэш-памяти 26, 28, 30 содержит необходимую ячейку памяти, то к соответствующей строке кэш-памяти обращаются, и обращение к памяти завершают, например, считывая или записывая в строку кэш-памяти. Иначе, MMU 36 инициирует обращение в оперативную память 18, 20, 22 для обращения к необходимой ячейке памяти.

К оперативной памяти 18, 20, 22 обращаются, обеспечивая физический адрес, который идентифицирует необходимую ячейку памяти. Запоминающее устройство, которое содержит необходимую ячейку памяти, называют в данной работе целевым запоминающим устройством. Согласно различным раскрытым вариантам осуществления целевое запоминающее устройство может содержать любой адресуемый модуль памяти, запоминающее устройство или группу блоков памяти, которые включает в себя система. Например, целевое запоминающее устройство может быть одним из DRAM 20, SGRAM 22 или другим запоминающим устройством (не показано) в зависимости от определенного процесса, выполняемого процессором 14.

В ответ на обращение к внешний памяти информацию о политике кэширования, связанной с соответствующим целевым запоминающим устройством, обеспечивают к схеме 40 установки политики кэширования, которую включает в себя или с которой связан MMU 36. Схема 40 установки политики кэширования определяет параметры настройки политики кэширования для текущей операции памяти, основываясь на информации о политике кэширования, связанной с соответствующим целевым запоминающим устройством. Таким образом, когда процессор 14 обращается к определенной ячейке внешней памяти, политику кэширования настраивают для соответствующего целевого запоминающего устройства, содержащего необходимую ячейку памяти.

Например, если операция памяти направлена на одно из устройств SGRAM 22, то политика выделения кэш-памяти, связанная с целевым устройством SGRAM, может быть «выделить только для чтения», когда целевое устройство функционирует в качестве буфера видеокадра для мультимедийного приложения. Процессор 14 может часто записывать в целевое устройство SGRAM во время выполнения мультимедийного приложения, но редко считывать из устройства. Таким образом, политика выделения кэш-памяти целевого устройства SGRAM может указывать «выделить только для чтения» для улучшения производительности процессора. Информация о политике кэширования целевого запоминающего устройства может также указывать определенную политику замещения, политику записи, политику выделения, политику уровня кэширования и/или одну или большее количество настраиваемых политик.

В одном из вариантов осуществления информацию о политике кэширования, связанную с целевым запоминающим устройством, обеспечивают с помощью контроллера 42 памяти, который обеспечивает интерфейс между шиной 12 и различными устройствами 20, 22 DRAM, как показано на фиг. 1. Согласно данному варианту осуществления контроллер 42 памяти включает в себя схему 44 декодера адреса, предназначенную для дешифрации физических адресов памяти, обеспеченных процессором 14, как часть обращения к памяти (например, чтения или записи). Информация о политике кэширования, сгенерированная с помощью схемы 44 декодера адреса, является функцией физического адреса памяти, обеспеченного как часть обращения к определенной памяти. Физический адрес идентифицирует запоминающее устройство, содержащее ячейку памяти, которая является целью текущей операции памяти.

Фиг. 2 показывает один из вариантов осуществления схемы 44 декодера адреса. Согласно данному варианту осуществления схема 44 декодера включает в себя декодер 46 адреса, мультиплексор (MUX) 48 и таблицу 50, имеющую различные записи 52, связанные с соответствующими запоминающими устройствами 20, 22, поддерживаемыми контроллером 42 памяти. Каждая запись таблицы 52 содержит информацию о политике кэширования, связанной с соответствующим запоминающим устройством.

Когда процессор 14 обращается к внешней памяти, физический адрес, который включает в себя как часть обращения, идентифицирует одно из запоминающих устройств 20, 22, поддерживаемых контроллером 42 памяти. Декодер 46 адреса выполняет дешифрацию физического адреса, побуждая мультиплексор 48 выбирать запись 52, содержащую информацию о политике кэширования, связанной с целевым запоминающим устройством, идентифицированным физическим адресом. Контроллер 42 памяти обеспечивает передачу выбранной информации о политике кэширования к MMU 36 через шину 12 и блок 32 интерфейса с шиной (например, как показано пунктирной линией, идущей от схемы 44 декодера адреса к MMU 36 на фиг. 1). Схема 40 установки политики кэширования использует принимаемую информацию о политике кэширования для установки политики кэширования для текущей операции памяти. Таким образом, политику кэширования можно устанавливать на основе строки кэш-памяти в качестве функции целевого запоминающего устройства.

В другом варианте осуществления информацию о политике кэширования обеспечивают с помощью схемы 54 декодера адреса, которую включает в себя процессор 14, как показано на фиг. 3. Согласно данному варианту осуществления схема 54 декодера адреса обеспечивает информацию о политике кэширования, основываясь на виртуальных адресах или физических адресах, например, как ранее описано и в соответствии с фиг. 2. В еще одном варианте осуществления одно или большее количество запоминающих устройств 20, 22, поддерживаемых контроллером памяти 42, хранят свою информацию о политике кэширования, например, в регистре ID (идентификатора) устройства или другом регистре (не показан). Когда к целевому запоминающему устройству обращается контроллер 42 памяти, информацию о политике кэширования обеспечивают на контроллер 42 и направляют к процессору 14, как ранее описано. Альтернативно, информацию о политике кэширования обеспечивают на процессор 14 без запроса, например автоматически во время начальной загрузки системы или после сброса процессора 14. Дополнительно, процессор 14 может сохранять информацию о специализированной политике кэширования после получения, таким образом устраняя потребность запрашивать ту же самую информацию, когда к соответствующему целевому запоминающему устройству впоследствии обращаются. Вместо этого процессор 14 внутренним образом извлекает и использует информацию о специализированной политике кэширования. В любом случае схема 40 установки политики кэширования использует информацию о политике кэширования целевого запоминающего устройства для установки политики кэширования во время операций памяти.

Фиг. 4 показывает вариант осуществления схемы 40 установки политики кэширования, которую включает в себя или которая связана с MMU 36. Согласно данному варианту осуществления схема 40 установки политики кэширования включает в себя схему 56 выбора, предназначенную для установки политики кэширования, направленной на текущую операцию памяти. Более конкретно, запись 58 таблицы страниц (PTE), соответствующая виртуальному адресу, обеспечиваемому как часть обращения к памяти, извлекают или из TLB 38, или из таблицы 34 страниц (например, как показано пунктирной линией, идущей от таблицы 34 страниц к MMU 36 на фиг. 1). Виртуальный адрес преобразовывают в соответствующий физический адрес, основываясь на информации 60 преобразования адреса, хранящейся в соответствующей PTE 58, где физический адрес идентифицирует необходимую ячейку памяти.

Если необходимая ячейка памяти не расположена ни в одной из разновидностей кэш-памяти 26, 28, 30 процессора, то MMU 36 инициирует обращение к внешней памяти. В ответ на запрос контроллер 42 памяти идентифицирует целевое запоминающее устройство, содержащее необходимую ячейку памяти, основываясь на преобразованном физическом адресе. Процессор 14 получает доступ к целевому запоминающему устройству через контроллер 42 памяти. Целевое запоминающее устройство выполняет необходимую операцию памяти (например, чтение или запись). Кроме того, информацию о политике кэширования, связанной с целевым запоминающим устройством, обеспечивают к схеме 40 установки политики кэширования и сохраняют в буфере 62 как часть операции памяти, например, как показано с помощью этапа 100 на фиг. 5.

Схема 56 выбора обрабатывает информацию 64 о политике кэширования, извлеченную из соответствующей PTE 58, и информацию о политике кэширования целевого запоминающего устройства, хранящуюся в буфере 62, например, как показано с помощью этапа 102 на фиг. 5. Информацию 64 о политике кэширования, извлеченную из соответствующей PTE 58, перезаписывают информацией целевого устройства и используют в качестве текущих параметров настройки политики кэширования. Однако, если информацию о политике кэширования не обеспечивают для целевого запоминающего устройства, то вместо нее используют информацию 64 о политике кэширования, извлеченную из соответствующей PTE 58.

Просто иллюстративный пример того, как схема 40 установки политики кэширования определяет политику кэширования, показывают на фиг. 6. Процессорное ядро 24 выдает запрос на запись в память по виртуальному адресу X. MMU 36 извлекает соответствующую PTE или из TLB 38, или из таблицы 34 страниц и использует ее для преобразования виртуального адреса X в соответствующий физический адрес X'. MMU 36 затем проверяет одну или большее количество разновидностей кэш-памяти 26, 28, 30 с физическим тегом, используя физический адрес X'. В этом примере ни одна из разновидностей кэш-памяти 26, 28, 30 не содержит необходимую ячейку памяти, как обозначено неудачным обращением в кэш-память. Соответственно, MMU 36 выдает запрос на запись во внешнюю память к контроллеру 42 памяти, основываясь на физическом адресе X'. Контроллер 42 памяти выбирает целевое запоминающее устройство, содержащее ячейку памяти, идентифицированную физическим адресом X'. Целевое запоминающее устройство выполняет необходимую операцию записи и сообщает контроллеру 42, что запись завершена.

Дополнительно, выполняют дешифрацию физического адреса X', и информацию о политике кэширования, соответствующую целевому запоминающему устройству, извлекают, как ранее описано, например, с помощью схемы 44 или 54 декодера адреса. Альтернативно, целевое запоминающее устройство обеспечивает свою информацию о политике кэширования на контроллер 42 памяти. В любом случае MMU 36 регистрирует, что операция записи завершена. Дополнительно, схема 40 установки политики кэширования обеспечивает информацию о политике кэширования целевого запоминающего устройства. В данном примере информация о политике кэширования указывает «выделить только для чтения». Таким образом, операцию записи завершают в процессоре 14, и MMU 36 не выделяет строку кэш-памяти ни в одной из разновидностей кэш-памяти 26, 28, 30 процессора.

Фиг. 7 продолжает примерную иллюстрацию, показывая последующий запрос на чтение, выданный процессорным ядром 24 к тому же самому виртуальному адресу X. Следует напомнить, что информация о политике кэширования целевого запоминающего устройства указывает «выделить только для чтения» для ячейки памяти, идентифицированной физическим адресом X'. Поэтому строки кэш-памяти не были ранее выделены для физического адреса X'. Во время настоящей операции чтения также происходит неудачное обращение в кэш-память.

Дополнительно, когда целевое запоминающее устройство завершает операцию чтения, операция чтения не заканчивается в процессоре 14, потому что информация о политике кэширования целевого устройства указывает, что строка кэш-памяти должна быть выделена. Таким образом, схема 40 установки политики кэширования устанавливает текущую политику выделения кэш-памяти таким образом, что MMU 36 дает команду одной из разновидностей кэш-памяти 26, 28, 30 процессора выделить строку кэш-памяти для физического адреса X'. Дополнительно, политика уровня кэш-памяти, связанная с целевым запоминающим устройством, может указывать, кэш-память какого уровня должна выделять строку кэш-памяти, например одна из кэш-памяти 26, 28 первого уровня, или кэш-память 30 L2. Другие политики кэширования можно также устанавливать, основываясь на информации о политике кэширования целевого устройства. В любом случае соответствующие данные также обеспечивают к процессорному ядру 24 для обработки.

Учитывая указанный выше диапазон разновидностей и применений, следует признать, что настоящее изобретение не ограничено ни предшествующим описанием, ни сопроводительными чертежами. Вместо этого настоящее изобретение ограничено только последующей формулой изобретения и ее юридическими эквивалентами.

1. Способ определения политики кэширования, содержащий этапы, на которых:принимают первую информацию о политике кэширования от схемы декодера адреса, основываясь на записи таблицы, связанной с целевым запоминающим устройством; иустанавливают политику кэширования, основываясь на второй информации о политике кэширования, принимаемой от целевого запоминающего устройства при сохранении первой информации о политике кэширования в регистре идентификатора устройства целевого запоминающего устройства.

2. Способ по п.1, в котором схема декодера адреса содержит декодер адреса, мультиплексор и таблицу, имеющую записи, связанные с целевым запоминающим устройством.

3. Способ по п.1, дополнительно содержащий этап, на котором перезаписывают первую информацию о политике кэширования второй информацией о политике кэширования при доступности второй информации о политике кэширования на целевом запоминающем устройстве и устанавливают политику кэширования, основываясь на второй информации о политике кэширования.

4. Способ по п.1, в котором политика кэширования включает в себя указание, кэш-память какого уровня должна выделять строку кэш-памяти в ответ на операцию памяти, направленную в целевое запоминающее устройство.

5. Способ по п.1, дополнительно содержащий этап, на котором устанавливают политику кэширования, основываясь на первой информации о политике кэширования при недоступности второй информации о политике кэширования на целевом запоминающем устройстве.

6. Процессор, содержащий:кэш-память, выполненную с возможностью хранения информации, локальной для процессора; иблок управления памятью, выполненный с возможностью установки политики кэширования для кэш-памяти, основываясь на информации о политике кэширования, при доступности информации о политике кэширования в регистре идентификатора устройства целевого запоминающего устройства.

7. Процессор по п.6, в котором блок управления памятью дополнительно выполнен с возможностью направления обращения к памяти на целевое запоминающее устройство.

8. Процессор по п.6, в котором блок управления памятью дополнительно выполнен с возможностьюприема дополнительной информации о политике кэширования от схемы декодера адреса процессора, причем дополнительная информация о политике кэширования извлекается из записи таблицы страниц, связанной с целевым запоминающим устройством; иустановки политики кэширования, основываясь на дополнительной информации о политике кэширования при недоступности дополнительной информации о политике кэширования на целевом запоминающем устройстве.

9. Система для определения политики кэширования, содержащая:процессор, содержащий:кэш-память, выполненную с возможностью хранения информации, локальной для процессора;блок управления памятью, выполненный с возможностью установки политики кэширования для кэш-памяти, основываясь на информации о политике кэширования при доступности информации о политике кэширования на целевом запоминающем устройстве.

10. Система по п.9, в которой процессор дополнительно содержит схему декодера адреса, выполненный с возможностью извлечения дополнительной информации о политике кэширования из записи таблицы страниц, связанной с целевым запоминающим устройством, и в которой процессор дополнительно выполнен с возможностью установки политики кэширования, основываясь на дополнительной информации о политике кэширования при недоступности дополнительной информации о политике кэширования на целевом запоминающем устройстве.

11. Способ определения политики кэширования, содержащий этапы, на которых:извлекают первую информацию о политике кэширования, связанную с целевым запоминающим устройством, из записи таблицы страниц, при этом таблица страниц связана с целевым запоминающим устройством;устанавливают политику кэширования, основываясь на первой информации о политике кэширования, при этом политика кэширования связана с операцией памяти в целевом запоминающем устройстве; ипри доступности второй информации о политике кэширования в регистре идентификатора устройства целевого запоминающего устройства:перезаписывают первую информацию о политике кэширования второй информацией о политике кэширования иустанавливают политику кэширования, основываясь на второй информации о политике кэширования.

12. Способ по п.11, в котором информация о политике кэширования принимается автоматически процессором во время загрузки системы либо в ответ на сброс процессора.

13. Способ по п.11, в котором политика кэширования включает в себя указание, кэш-память какого уровня должна выделять строку кэш-памяти в ответ на операцию памяти, направленную в целевое запоминающее устройство.

14. Способ по п.11, в котором политика кэширования указывает выделять только для чтения.

15. Процессор, содержащий:кэш-память, выполненную с возможностью хранения информации, локальной для процессора; иблок управления памятью, выполненный с возможностью:установки политики кэширования, основываясь на первой информации о политике кэширования, сохраненной в записи таблицы страниц, связанной с целевым запоминающим устройством, при этом целевое запоминающее устройство идентифицируется адресом, связанным с обращением к памяти процессором, причем целевое запоминающее устройство не является кэш-памятью; ипри доступности второй информации о политике кэширования в регистре идентификатора устройства целевого запоминающего устройства:перезаписи первой информации о политике кэширования второй информацией о политике кэширования изамены политики кэширования другой политикой кэширования, основываясь на второй информации о политике кэширования.

16. Процессор по п.15, в котором кэш-память содержит кэш-память Уровня 2 (L2).

17. Процессор по п.15, в котором политика кэширования включает в себя указание, кэш-память какого уровня должна выделять строку кэш-памяти в ответ на операцию памяти, направленную в целевое запоминающее устройство.

18. Система для определения политики кэширования, содержащая:целевое запоминающее устройство ипроцессор, соединенный с целевым запоминающим устройством, при этом процессор включает в себя:кэш-память, выполненную с возможностью хранения информации, локальной для процессора; иблок управления памятью, выполненный с возможностью:установки политики кэширования, основываясь на первой информации о политике кэширования, связанной с целевым запоминающим устройством, причем первая информация о политике кэширования сохранена в записи таблицы страниц, связанной с целевым запоминающим устройством, и при этом запись таблицы страниц идентифицируется адресом, связанным с обращением к памяти процессором; ипри доступности второй информации о политике кэширования в регистре идентификатора устройства целевого запоминающего устройства: перезаписи первой информации о политике кэширования второй информацией о политике кэширования и установки политики кэширования, основываясь на второй информации о политике кэширования.

19. Система по п.18, в которой кэш-память является кэш-памятью команд.

20. Система по п.18, в которой кэш-память является кэш-памятью данных.

21. Система по п.18, в которой целевое запоминающее устройство является синхронным графическим оперативным запоминающим устройством (SGRAM).

22. Система по п.18, в которой целевое запоминающее устройство является синхронным динамическим оперативным запоминающим устройством (SDRAM).

23. Система по п.18, в которой политика кэширования включает в себя указание, кэш-память какого уровня должна выделять строку кэш-памяти в ответ на операцию памяти, направленную в целевое запоминающее устройство.