Самосинхронный rs-триггер с повышенной помехоустойчивостью (варианты)

Иллюстрации

Показать всеИзобретение относится к импульсной и вычислительной технике и может использоваться при построении самосинхронных триггерных, регистровых и вычислительных устройств, систем цифровой обработки информации. Техническим результатом является повышение помехоустойчивости самосинхронного RS-триггера. Устройство содержит блок памяти, блок индикации окончания процессов переключения элементов в триггере, инверторы, блок пре-индикации, отслеживающий окончание переходных процессов в триггере вместе с блоком индикации. 2 н. и 28 з.п. ф-лы, 2 табл., 48 ил.

Реферат

Самосинхронный RS-триггер с повышенной помехоустойчивостью относится к импульсной и вычислительной технике и может использоваться при построении самосинхронных триггерных, регистровых и вычислительных устройств, систем цифровой обработки информации.

Известен RS-триггер [1], содержащий два элемента ИЛИ-НЕ.

Недостаток известного устройства - отсутствие средств индикации окончания переходных процессов.

Наиболее близким к предлагаемому решению по технической сущности и принятым в качестве прототипа является самосинхронный RS-триггер [2], содержащий блок памяти, индикаторный элемент, парафазный информационный вход, вход разрешения записи (вход запроса), вход сброса, первую и вторую составляющие парафазного информационного выхода и индикаторный выход.

Недостаток прототипа - низкая помехоустойчивость из-за того, что информационный выход триггера берется непосредственно с выходов бистабильной ячейки, хранящей состояние триггера, характеризуется низкой нагрузочной способностью и подвержен влиянию помех на сигнальных линиях внешнего окружения триггера, способных привести к несанкционированному изменению состояния бистабильной ячейки.

Задача, решаемая в изобретении, заключается в увеличении помехоустойчивости триггера.

Это достигается тем, что в самосинхронном RS-триггере, содержащем блок памяти, блок индикации, первую и вторую составляющие парафазного информационного входа, первую и вторую составляющие парафазного информационного выхода и индикаторный выход, причем первая и вторая составляющие парафазного информационного входа соединены с первым и вторым входами блока памяти соответственно, первая составляющая парафазного информационного выхода триггера подключена к первому входу блока индикации, вторая составляющая парафазного информационного выхода триггера подключена ко второму входу блока индикации, индикаторный выход триггера соединен с выходом блока индикации, введены два инвертора и блок пре-индикации, первый и второй входы блока пре-индикации соединены с первой и второй составляющими парафазного информационного входа соответственно, вход первого инвертора подключен к первому выходу блока памяти, а его выход соединен с первой составляющей парафазного информационного выхода триггера и третьим входом блока пре-индикации, вход второго инвертора подключен ко второму выходу блока памяти, а его выход соединен со второй составляющей парафазного информационного выхода триггера и четвертым входом блока пре-индикации, первый и второй выходы блока пре-индикации подключены к третьему и четвертому входам блока индикации соответственно, в качестве информационного входа используется парафазный вход со спейсером.

Предлагаемое устройство удовлетворяет критерию "существенные отличия". Использование инверторов в синхронных триггерах известно. Однако использование их в самосинхронном RS-триггере в сочетании с блоком пре-индикации, с учетом специфики работы самосинхронных устройств и сохранения свойства индицируемости триггера позволило достичь эффекта, выраженного целью изобретения. Существенное отличие предлагаемой реализации RS-триггера от аналогичных решений в самосинхронной схемотехнике заключается в решении проблемы сохранения индицируемости триггера (гарантированного отслеживания моментов окончания всех переходных процессов при переключении триггера из одного состояния в другое) при вводе инверторов на его парафазном информационном выходе. Конкретные технические реализации предлагаемого решения описаны ниже.

Поскольку введенные конструктивные связи в аналогичных технических решениях не известны, устройство может считаться имеющим существенные отличия.

Понятие "парафазный", используемое в тексте данной заявки, определяется следующим образом. Парафазным считается сигнал, представленный двумя составляющими - парой переменных, которые в статическом состоянии имеют взаимоинверсные состояния. В результате в статическом состоянии такой сигнал {X, ХВ} может принимать одно из двух рабочих состояний: {Х=0, ХВ=1} или {Х=1, ХВ=0}.

Переход парафазного сигнала из одного статического рабочего состояния в противоположное рабочее состояние может осуществляться двумя способами.

Первый способ предполагает использование парафазного сигнала со спейсером: когда переходу в следующее рабочее статическое состояние обязательно предшествует переход в третье статическое состояние - спейсерное (нерабочее состояние или состояние гашения). Если используется состояние {1,1}, то говорят, что используется парафазный сигнал с единичным спейсером, а если состояние {0,0}, то - парафазный сигнал с нулевым спейсером. Спейсерное состояние - статическое состояние, установка которого в самосинхронной схемотехнике должна фиксироваться индикатором окончания переходного процесса, в данном случае - окончания установки спейсерного состояния.

Второй способ предполагает использование парафазного сигнала без спейсера (или просто парафазного сигнала). При этом переход из одного рабочего статического состояния в другое осуществляется через динамическое (кратковременное) состояние: {1,1} или {0,0}, - называемое транзитным состоянием.

В материалах данной заявки в качестве информационного входного сигнала триггера используется парафазный сигнал со спейсером в вариантах без входа разрешения записи и парафазный сигнал без спейсера в вариантах, где есть вход разрешения записи, а информационный выход триггера является парафазным сигналом без спейсера.

На фиг.1 изображена схема однотактного самосинхронного RS-триггера с повышенной помехоустойчивостью.

Схема содержит блок памяти 1, блок индикации 2, первую 3 и вторую 4 составляющие парафазного информационного входа, первую 5 и вторую 6 составляющие парафазного информационного выхода, индикаторный выход 7, первый 8 и второй 9 инверторы, блок пре-индикации 10, первая 3 составляющая парафазного информационного входа соединена с первым I1 входом блока памяти 1 и первым Х1 входом блока пре-индикации 10, вторая 4 составляющая парафазного информационного входа соединена со вторым I2 входом блока памяти 1 и вторым Х2 входом блока пре-индикации 10, первый Q1 выход блока памяти 1 подключен к входу первого инвертора 8, выход которого соединен с третьим Х3 входом блока пре-индикации 10, первым входом К1 блока индикации 2 и первой 5 составляющей парафазного информационного выхода триггера, второй Q2 выход блока памяти 1 подключен к входу второго инвертора 9, выход которого соединен с четвертым X4 входом блока пре-индикации 10, вторым входом К2 блока индикации 2 и второй 6 составляющей парафазного информационного выхода триггера, первый Y1 и второй Y2 выходы блока пре-индикации 10 подключены к третьему K3 и четвертому K4 входам блока индикации 2 соответственно, выход О блока индикации 2 подключен к индикаторному выходу 7 триггера.

Схема работает следующим образом. При подаче на информационный вход рабочего состояния происходит запись нового состояния в блок памяти 1, которое через инверторы 8 и 9 транслируется на первую 5 и вторую 6 составляющие парафазного информационного выхода триггера. Окончание записи нового состояния в триггер или переход его в фазу хранения фиксируют блоки пре-индикации 10 и индикации 2, анализирующие соответствие состояний на выходе инверторов 8-9 и парафазном входе I1-I2 блока памяти 1, соответствующим значением индикаторного выхода 7 триггера. Конкретное значение спейсера (00 или 11) информационного входа 3-4 однозначно соответствует базису реализации триггера.

Особенности данной схемы по сравнению с прототипом следующие.

Триггер имеет инверторы, формирующие составляющие парафазного информационного выхода. Они увеличивают нагрузочную способность парафазного информационного выхода триггера и обеспечивают электрическую развязку выходов блока памяти от внешнего окружения, что приводит к повышению устойчивости хранимой в триггере информации к воздействию помех на сигнальных шинах схемы.

Таким образом, предлагаемое устройство обеспечивает повышение нагрузочной способности выходов триггера и его помехоустойчивости. Цель изобретения достигнута.

Конкретная техническая реализация предлагаемого однотактного самосинхронного RS-триггера и его составных блоков зависит от типа спейсерного состояния парафазного входа: высокий или низкий уровень на обеих составляющих информационного входа обеспечивает хранение состояния триггера. Он влияет на базис реализации блоков памяти и индикации и определяет спецификацию первой и второй составляющих парафазного информационного входа со спейсером и первой и второй составляющих парафазного информационного выхода триггера, как описано ниже.

На фиг.2 показана схема двухтактного самосинхронного RS-триггера с повышенной помехоустойчивостью. Она отличается от схемы на фиг.1 тем, что блок памяти 1 содержит два дополнительных выхода U1, U2, являющихся выходами входной бистабильной ячейки блока памяти 1, подключенных к пятому X5 и шестому Х6 входам блока пре-индикации 10.

Схема двухтактного самосинхронного RS-триггера работает следующим образом. При подаче на информационный вход рабочего состояния происходит запись нового состояния в первую бистабильную ячейку блока памяти 1 с выходами U1, U2. При этом состояние выходов Q1, Q2 блока памяти 1 и соответственно парафазного выхода 5, 6 триггера не изменяется. Окончание переключений элементов триггера фиксируется блоком индикации 2 изменением состояния его выхода. После подачи на вход 3, 4 спейсера состояние первой бистабильной ячейки блока памяти 1 переписывается в его вторую бистабильную ячейку и через инверторы 8 и 9 транслируется на парафазный выход 5, 6 триггера. По окончании переключений всех элементов триггера блок индикации 2 и соответственно индикаторный выход 7 триггера переключаются в противоположное состояние (возвращаются в исходное состояние, соответствующее состоянию хранения в первой бистабильной ячейке блока памяти 1).

На фиг.3 представлена схема блока индикации для всех однотактных самосинхронных RS-триггеров с повышенной помехоустойчивостью, имеющих парафазный информационный вход с нулевым спейсером, и всех двухтактных самосинхронных RS-триггеров с повышенной помехоустойчивостью, имеющих парафазный информационный вход с единичным спейсером. Она содержит элемент ИЛИ-И-НЕ 11, чьи входы первой группы входов ИЛИ подключены к первому K1 и третьему К3 входам блока индикации, входы второй группы входов ИЛИ соединены со вторым К2 и четвертым К4 входами блока индикации, а выход подключен к выходу блока индикации О.

На фиг.4 показана схема блока индикации для всех однотактных самосинхронных RS-триггеров с повышенной помехоустойчивостью, имеющих парафазный информационный вход с единичным спейсером, и всех двухтактных самосинхронных RS-триггеров с повышенной помехоустойчивостью, имеющих парафазный информационный вход с нулевым спейсером. Она содержит элемент И-ИЛИ-НЕ 12, чьи входы первой группы входов И подключены к первому K1 и третьему К3 входам блока индикации, входы второй группы входов И соединены со вторым К2 и четвертым K4 входами блока индикации, а выход подключен к выходу блока индикации О.

На фиг.5 представлена схема блока пре-индикации 10 однотактного самосинхронного RS-триггера с повышенной помехоустойчивостью с парафазным информационным входом с нулевым спейсером. Она состоит из двух элементов И-НЕ 13-14, входы первого элемента И-НЕ 13 подключены к первому Х1 и третьему Х3 входам блока пре-индикации 10, входы второго элемента И-НЕ 14 подключены ко второму Х2 и четвертому X4 входам блока пре-индикации 10, выходы второго 14 и первого 13 элементов И-НЕ соединены с первым Y1 и вторым Y2 выходами блока пре-индикации 10 соответственно.

На фиг.6 показана схема блока пре-индикации 10 однотактного самосинхронного RS-триггера с повышенной помехоустойчивостью с парафазным информационным входом с единичным спейсером. Она состоит из двух элементов ИЛИ-НЕ 15-16, входы первого элемента ИЛИ-НЕ 15 подключены к первому X1 и третьему Х2 входам блока пре-индикации 10, входы второго элемента ИЛИ-НЕ 16 подключены ко второму Х2 и четвертому Х4 входам блока пре-индикации 10, выходы второго 16 и первого 15 элементов ИЛИ-НЕ соединены с первым Y1 и вторым Y2 выходами блока пре-индикации 10 соответственно.

На фиг.7 показана схема блока пре-индикации 10 двухтактного самосинхронного RS-триггера с повышенной помехоустойчивостью с парафазным информационным входом с нулевым спейсером. Она состоит из двух элементов ИЛИ-НЕ 17-18, входы первого элемента ИЛИ-НЕ 17 подключены к первому X1, третьему Х3 и пятому X5 входам блока пре-индикации 10, входы второго элемента ИЛИ-НЕ 18 подключены ко второму Х2, четвертому Х4 и шестому Х6 входам блока пре-индикации 10, выходы второго 18 и первого 17 элементов ИЛИ-НЕ соединены с первым Y1 и вторым Y2 выходами блока пре-индикации 10 соответственно.

На фиг.8 показана схема блока пре-индикации 10 двухтактного самосинхронного RS-триггера с повышенной помехоустойчивостью с парафазным информационным входом с единичным спейсером. Она состоит из двух элементов И-НЕ 19-20, входы первого элемента И-НЕ 19 подключены к первому X1, третьему Х3 и пятому Х5 входам блока пре-индикации 10, входы второго элемента И-НЕ 20 подключены ко второму Х2, четвертому Х4 и шестому Х6 входам блока пре-индикации 10, выходы второго 20 и первого 19 элементов И-НЕ соединены с первым Y1 и вторым Y2 выходами блока пре-индикации 10 соответственно.

Традиционно блок памяти в однотактных самосинхронных RS-триггерах реализуется на одной бистабильной ячейке, чьи выходы являются выходами блока памяти и триггера. Примеры реализации блока памяти однотактного RS-триггера с парафазным информационным входом с единичным и нулевым спейсером показаны на фиг.9 и 10 соответственно. Они идентичны схемам RS-триггеров на фиг.2.2(а) и фиг.2.2(б) в [3].

Схема блока памяти 1 однотактного самосинхронного RS-триггера с повышенной помехоустойчивостью с парафазным информационным входом с единичным спейсером (фиг.9) содержит два элемента И-НЕ 21-22, входы первого элемента И-НЕ 21 подключены к первому I1 входу и второму выходу Q2 блока памяти, входы второго элемента И-НЕ 22 подключены к первому выходу Q1 и второму I2 входу блока памяти, выходы первого 21 и второго 22 элементов И-НЕ подключены к первому Q1 и второму Q2 выходам блока памяти соответственно.

Схема блока памяти 1 однотактного самосинхронного RS-триггера с повышенной помехоустойчивостью с парафазным информационным входом с нулевым спейсером (фиг.10) содержит два элемента ИЛИ-НЕ 23-24, входы первого элемента ИЛИ-НЕ 23 подключены к первому I1 входу и второму выходу Q2 блока памяти, входы второго элемента ИЛИ-НЕ 24 подключены к первому выходу Q1 и второму I2 входу блока памяти, выходы первого 23 и второго 24 элементов ИЛИ-НЕ подключены к первому Q1 и второму Q2 выходам блока памяти соответственно.

В двухтактных самосинхронных RS-триггерах блок памяти 1 традиционно содержит две бистабильные ячейки, включенные последовательно. Схемы блока памяти двухтактного RS-триггера для парафазного информационного входа с нулевым и единичным спейсером показаны на фиг.11 и 12 соответственно.

Схема блока памяти 1 двухтактного самосинхронного RS-триггера с повышенной помехоустойчивостью с парафазным информационным входом с нулевым спейсером (фиг.11) содержит два элемента ИЛИ-НЕ 25-26 и два элемента ИЛИ-И-НЕ 27-28, первый вход первого элемента ИЛИ-НЕ 25 подключен к первому I1 входу блока памяти и первому входу первой группы входов ИЛИ первого элемента ИЛИ-И-НЕ 27, выход первого элемента ИЛИ-НЕ 25 соединен с первым входом второго элемента ИЛИ-НЕ 26, вторым входом первой группы входов ИЛИ первого элемента ИЛИ-И-НЕ 27 и третьим выходом блока памяти U1, второй вход второго элемента ИЛИ-НЕ 26 подключен ко второму входу I2 блока памяти и второму входу первой группы входов ИЛИ второго элемента ИЛИ-И-НЕ 28, выход второго элемента ИЛИ-НЕ 26 соединен со вторым входом первого элемента ИЛИ-НЕ 25, первым входом первой группы входов ИЛИ второго элемента ИЛИ-И-НЕ 28 и четвертым выходом U2 блока памяти, выход первого элемента ИЛИ-И-НЕ 27 подключен к входу второй группы входов ИЛИ второго элемента ИЛИ-И-НЕ 28 и первому выходу блока памяти Q1, выход второго элемента ИЛИ-И-НЕ 28 соединен с входом второй группы входов ИЛИ первого элемента ИЛИ-И-НЕ 27 и вторым выходом блока памяти Q2.

Схема блока памяти 1 двухтактного самосинхронного RS-триггера с повышенной помехоустойчивостью с парафазным информационным входом с единичным спейсером (фиг.12) содержит два элемента И-НЕ 29-30 и два элемента И-ИЛИ-НЕ 31-32, первый вход первого элемента И-НЕ 29 подключен к первому I1 входу блока памяти и первому входу первой группы входов И первого элемента И-ИЛИ-НЕ 31, выход первого элемента И-НЕ 29 соединен с первым входом второго элемента И-НЕ 30, вторым входом первой группы входов И первого элемента И-ИЛИ-НЕ 31 и третьим выходом блока памяти U1, второй вход второго элемента И-НЕ 30 подключен ко второму входу I2 блока памяти и второму входу первой группы входов И второго элемента И-ИЛИ-НЕ 32, выход второго элемента И-НЕ 30 соединен со вторым входом первого элемента И-НЕ 29, первым входом первой группы входов И второго элемента И-ИЛИ-НЕ 32 и четвертым выходом U2 блока памяти, выход первого элемента И-ИЛИ-НЕ 31 подключен к входу второй группы входов И второго элемента И-ИЛИ-НЕ 32 и первому выходу блока памяти Q1, выход второго элемента И-ИЛИ-НЕ 32 соединен с входом второй группы входов И первого элемента И-ИЛИ-НЕ 31 и вторым выходом блока памяти Q2.

Блок памяти может иметь дополнительные входы синхронного сброса и установки (входы предустановки), не требующие индикации. На реализацию блоков пре-индикации и индикации они не оказывают никакого влияния.

Однако на практике часто требуется зафиксировать и окончание предустановки триггера и всей схемы в целом. В этом случае необходимо использовать самосинхронный сброс или установку.

На фиг.13 представлена схема однотактного самосинхронного RS-триггера с повышенной помехоустойчивостью с парафазным информационным входом со спейсером и входом самосинхронной предустановки (сброса или установки). Она отличается от схемы на фиг.1 наличием входа предустановки 33, подключенного к третьему входу I3 блока памяти 1 и пятому входу X5 блока пре-индикации 10.

На фиг.14 представлена схема двухтактного самосинхронного RS-триггера с повышенной помехоустойчивостью с парафазным информационным входом со спейсером и входом самосинхронной предустановки (сброса или установки). Она отличается от схемы на фиг.2 наличием входа предустановки 33, подключенного к третьему входу I3 блока памяти 1 и седьмому входу Х7 блока пре-индикации 10.

Предустановка осуществляется при спейсере на парафазном информационном входе подачей на вход предустановки уровня сигнала, обратного по отношению к спейсеру парафазного входа. Схема блока памяти однотактного самосинхронного RS-триггера реализуется одинаковым образом для синхронной и самосинхронной предустановки.

На фиг.15 показана схема блока памяти 1 однотактного самосинхронного RS-триггера с повышенной помехоустойчивостью с парафазным информационным входом с нулевым спейсером и входом предустановки. Она отличается от схемы на фиг.10 тем, что введены третий вход блока памяти, являющийся входом предустановки, I3 и третий вход во втором элементе ИЛИ-НЕ 24, соединенные друг с другом.

Пусть парафазный вход блока памяти I1, I2 находится в состоянии спейсера (I1=I2=0) и бистабильная ячейка на элементах 23 и 24 хранит состояние Q1=0, Q2=1. Подача на вход предустановки высокого уровня, обратного по отношению к входному спейсеру, I3=1, устанавливает бистабильную ячейку в состояние Q1=1, Q2=0, противоположное исходному.

На фиг.16 показана схема блока памяти 1 однотактного самосинхронного RS-триггера с повышенной помехоустойчивостью с парафазным информационным входом с единичным спейсером и входом предустановки. Она отличается от схемы на фиг.9 тем, что введены третий вход блока памяти, являющийся входом предустановки, I3 и третий вход во втором элементе И-НЕ 22, соединенные друг с другом.

Пусть парафазный вход блока памяти I1, I2 находится в состоянии спейсера (I1=I2=1) и бистабильная ячейка на элементах 21 и 22 хранит состояние Q1=1, Q2=0. Подача на вход предустановки низкого уровня, обратного по отношению к входному спейсеру, I3=0, устанавливает бистабильную ячейку в состояние Q1=0, Q2=1, противоположное исходному.

Для двухтактного самосинхронного RS-триггера блоки памяти с синхронной и самосинхронной предустановкой реализуются различными схемами.

На фиг.17 приведена схема блока памяти 1 двухтактного самосинхронного RS-триггера с повышенной помехоустойчивостью с парафазным информационным входом с нулевым спейсером и входом синхронной предустановки. Она отличается от схемы на фиг.11 тем, что введены третий вход блока памяти, являющийся входом синхронной предустановки, I3 триггера и третий вход во втором элементе ИЛИ-НЕ 26, соединенные друг с другом.

На фиг.18 приведена схема блока памяти 1 двухтактного самосинхронного RS-триггера с повышенной помехоустойчивостью с парафазным информационным входом с единичным спейсером и входом синхронной предустановки. Она отличается от схемы на фиг.12 тем, что введены третий вход блока памяти, являющийся входом синхронной предустановки, I3 триггера и третий вход во втором элементе И-НЕ 30, соединенные друг с другом.

На фиг.19 приведена схема блока памяти 1 двухтактного самосинхронного RS-триггера с повышенной помехоустойчивостью с парафазным информационным входом с нулевым спейсером и входом самосинхронной предустановки. Она отличается от схемы на фиг.17 тем, что в первую группу входов ИЛИ второго элемента ИЛИ-И-НЕ 28 введен третий вход, соединенный с третьим входом I3 блока памяти.

На фиг.20 приведена схема блока памяти 1 двухтактного самосинхронного RS-триггера с повышенной помехоустойчивостью с парафазным информационным входом с единичным спейсером и входом самосинхронной предустановки. Она отличается от схемы на фиг.18 тем, что в первую группу входов И второго элемента И-ИЛИ-НЕ 32 введен третий вход, соединенный с третьим входом I3 блока памяти.

Для RS-триггера с повышенной помехоустойчивостью с синхронной предустановкой блоки пре-индикации и индикации используются те же самые, что и для RS-триггера без предустановки. Для RS-триггера с самосинхронной предустановкой блок пре-индикации усложняется.

На фиг.21 показана схема блока пре-индикации однотактного самосинхронного RS-триггера с повышенной помехоустойчивостью с парафазным информационным входом с нулевым спейсером и входом самосинхронной предустановки. Схема содержит элемент И-НЕ 34 и элемент ИЛИ-И-НЕ 35, входы элемента И-НЕ 34 подключены к первому X1 и третьему Х3 входам блока пре-индикации, а его выход соединен со вторым выходом Y2 блока пре-индикации, входы первой группы входов ИЛИ элемента ИЛИ-И-НЕ 35 подключены ко второму Х2 и пятому Х5 входам блока пре-индикации, вход второй группы входов ИЛИ элемента ИЛИ-И-НЕ 35 соединен с четвертым входом Х4 блока пре-индикации, выход элемента ИЛИ-И-НЕ 35 подключен к первому выходу Y1 блока пре-индикации.

На фиг.22 показана схема блока пре-индикации однотактного самосинхронного RS-триггера с повышенной помехоустойчивостью с парафазным информационным входом с единичным спейсером и входом самосинхронной предустановки. Схема содержит элемент ИЛИ-НЕ 36 и элемент И-ИЛИ-НЕ 37, входы элемента ИЛИ-НЕ 36 подключены к первому X1 и третьему Х2 входам блока пре-индикации, а его выход соединен со вторым выходом Y2 блока пре-индикации, входы первой группы входов И элемента И-ИЛИ-НЕ 37 подключены ко второму Х2 и пятому Х5 входам блока пре-индикации, вход второй группы входов И элемента И-ИЛИ-НЕ 37 соединен с четвертым входом Х4 блока пре-индикации, выход элемента И-ИЛИ-НЕ 37 подключен к первому выходу Y1 блока пре-индикации.

На фиг.23 показана схема блока пре-индикации двухтактного самосинхронного RS-триггера с повышенной помехоустойчивостью с парафазным информационным входом с нулевым спейсером и входом самосинхронной предустановки. Схема отличается от схемы на фиг.7 тем, что в блок пре-индикации введен седьмой вход Х7, а во второй элемент ИЛИ-НЕ 18 введен четвертый вход, подключенный к седьмому входу Х7 блока пре-индикации.

На фиг.24 показана схема блока пре-индикации для двухтактного самосинхронного RS-триггера с повышенной помехоустойчивостью с парафазным информационным входом с единичным спейсером и входом самосинхронной предустановки. Схема отличается от схемы на фиг.8 тем, что в блок пре-индикации введен седьмой вход Х7, а во второй элемент И-НЕ 20 введен четвертый вход, подключенный к седьмому входу X7 блока пре-индикации.

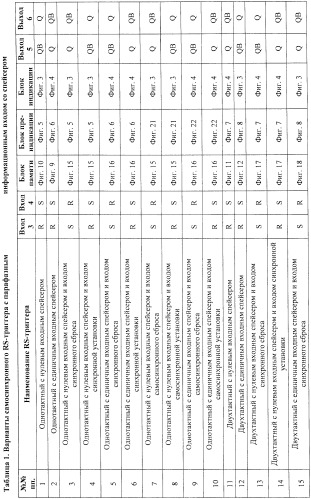

Описанные выше структурные схемы и схемы блоков памяти, пре-индикации и индикации охватывают различные варианты реализации самосинхронного RS-триггера с повышенной помехоустойчивостью с парафазным информационным входом со спейсером в зависимости от спецификации входов триггера. Таблица 1 представляет комбинации блоков самосинхронного RS-триггера с парафазным информационным входом со спейсером и спецификаций входных и выходных сигналов, образующие конкретные реализации триггера.

Рассмотренные варианты реализации самосинхронного RS-триггера характеризуются наличием спейсера у информационного входного сигнала, что позволяет организовать управление триггером: перевод его в фазу обновления состояния информационного выхода или в фазу хранения этого состояния только за счет изменения состояния информационного входного сигнала.

На практике, однако, в качестве информационного входа триггера часто используется парафазный сигнал без спейсера. Он имеет только два статически устойчивых состояния, в которых две составляющие этого сигнала принимают взаимоинверсные значения. В этом случае для успешного управления триггером требуется дополнительный сигнал, называемый сигналом управления или сигналом разрешения записи. Это однофазный сигнал, имеющий спейсерное состояние (спейсер) и рабочее (активное) состояние. При спейсере на входе разрешения записи однотактный RS-триггер хранит состояние парафазного информационного выхода, а двухтактный RS-триггер переписывает состояние входной бистабильной ячейки в выходную, обновляя состояние своего парафазного информационного выхода.

Схема однотактного самосинхронного RS-триггера с повышенной помехоустойчивостью с входом разрешения записи идентична схеме на фиг.13. Отличие заключается только в том, что вход 33 является входом разрешения записи, а не самосинхронной предустановки.

Схема двухтактного самосинхронного RS-триггера с повышенной помехоустойчивостью с входом разрешения записи идентична схеме на фиг.14. Отличие заключается только в том, что вход 33 является входом разрешения записи, а не самосинхронной предустановки.

Блок индикации в схемах однотактного и двухтактного RS-триггера с повышенной помехоустойчивостью с входом разрешения записи реализуется схемой, идентичной схеме блока индикации однотактного и двухтактного RS-триггера с повышенной помехоустойчивостью с парафазным со спейсером информационным входом соответственно с таким же типом входного спейсера и представлен на фиг.3 и 4.

На фиг.25 приведена схема блока памяти однотактного самосинхронного RS-триггера с повышенной помехоустойчивостью с входом разрешения записи с нулевым спейсером. Схема содержит два элемента И-ИЛИ-НЕ 38-39, первые входы первых групп входов И первого 38 и второго 39 элементов И-ИЛИ-НЕ подключены соответственно к первому I1 и второму I2 входам блока памяти, вторые входы первых групп входов И первого 38 и второго 39 элементов И-ИЛИ-НЕ соединены с третьим I3 входом блока памяти, выход первого элемента И-ИЛИ-НЕ 38 подключен к первому выходу Q1 блока памяти и входу второй группы входов И второго элемента И-ИЛИ-НЕ 39, выход которого соединен со вторым выходом Q2 блока памяти и входом второй группы входов И первого элемента И-ИЛИ-НЕ 38.

Схема на фиг.25 работает следующим образом. При высоком уровне сигнала на входе I3 блок памяти запоминает информацию с входов I1 и I2. При низком уровне (спейсере) сигнала на входе I3 блок памяти хранит состояние своих выходов Q1 и Q2.

На фиг.26 показана схема блока памяти однотактного самосинхронного RS-триггера с повышенной помехоустойчивостью с входом разрешения записи с единичным спейсером. Схема содержит два элемента ИЛИ-И-НЕ 40-41, первые входы первых групп входов ИЛИ первого 40 и второго 41 элементов ИЛИ-И-НЕ подключены соответственно к первому I1 и второму I2 входам блока памяти, вторые входы первых групп входов ИЛИ первого 40 и второго 41 элементов ИЛИ-И-НЕ соединены с третьим I3 входом блока памяти, выход первого элемента ИЛИ-И-НЕ 40 подключен к первому выходу Q1 блока памяти и входу второй группы входов ИЛИ второго элемента ИЛИ-И-НЕ 41, выход которого соединен со вторым выходом Q2 блока памяти и входом второй группы входов ИЛИ первого элемента ИЛИ-И-НЕ 40.

Схема на фиг.26 работает следующим образом. При низком уровне сигнала на входе I3 блок памяти запоминает информацию с входов I1 и I2. При высоком уровне (спейсере) сигнала на входе I3 блок памяти хранит состояние своих выходов Q1 и Q2.

На фиг.27 приведена схема блока памяти двухтактного самосинхронного RS-триггера с повышенной помехоустойчивостью с входом разрешения записи с нулевым спейсером. Схема содержит два элемента И-ИЛИ-НЕ 42-43 и два элемента ИЛИ-И-НЕ 44-45, первые входы первых групп входов И первого 42 и второго 43 элементов И-ИЛИ-НЕ подключены соответственно к первому I1 и второму I2 входам блока памяти, вторые входы первых групп входов И первого 42 и второго 43 элементов И-ИЛИ-НЕ соединены с третьим I3 входом блока памяти и со вторыми входами первых групп входов ИЛИ первого 44 и второго 45 элементов ИЛИ-И-НЕ, выход первого элемента И-ИЛИ-НЕ 42 подключен к первому входу первой группы входов ИЛИ первого элемента ИЛИ-И-НЕ 44, входу второй группы входов И второго элемента И-ИЛИ-НЕ 43 и третьему выходу блока памяти U1, выход второго элемента И-ИЛИ-НЕ 43 соединен с первым входом первой группы входов ИЛИ второго элемента ИЛИ-И-НЕ 45, входом второй группы входов И первого элемента И-ИЛИ-НЕ 42 и четвертым выходом блока памяти U2, выход первого элемента ИЛИ-И-НЕ 44 подключен к первому выходу Q1 блока памяти и входу второй группы входов ИЛИ второго элемента ИЛИ-И-НЕ 45, выход которого соединен со вторым выходом Q2 блока памяти и входом второй группы входов ИЛИ первого элемента ИЛИ-И-НЕ 44.

Схема фиг.27 работает следующим образом. При высоком уровне сигнала на входе I3 блок памяти записывает информацию с входов I1 и I2 в первую бистабильную ячейку на элементах 42 и 43. При низком уровне (спейсере) сигнала на входе I3 блок памяти хранит состояние первой бистабильной ячейки и переписывает его во вторую бистабильную ячейку на элементах 44 и 45.

На фиг.28 приведена схема блока памяти двухтактного самосинхронного RS-триггера с повышенной помехоустойчивостью с входом разрешения записи с единичным спейсером. Схема содержит два элемента ИЛИ-И-НЕ 46-47 и два элемента И-ИЛИ-НЕ 48-49, первые входы первых групп входов ИЛИ первого 46 и второго 47 элементов ИЛИ-И-НЕ подключены соответственно к первому I1 и второму I2 входам блока памяти, вторые входы первых групп входов ИЛИ первого 46 и второго 47 элементов ИЛИ-И-НЕ соединены с третьим I3 входом блока памяти и со вторыми входами первых групп входов И первого 48 и второго 49 элементов И-ИЛИ-НЕ, выход первого элемента ИЛИ-И-НЕ 46 подключен к первому входу первой группы входов И первого элемента И-ИЛИ-НЕ 48, входу второй группы входов ИЛИ второго элемента ИЛИ-И-НЕ 47 и третьему выходу блока памяти U1, выход второго элемента ИЛИ-И-НЕ 47 соединен с первым входом первой группы входов И второго элемента И-ИЛИ-НЕ 49, входом второй группы входов ИЛИ первого элемента ИЛИ-И-НЕ 46 и четвертым выходом блока памяти U2, выход первого элемента И-ИЛИ-НЕ 48 подключен к первому выходу Q1 блока памяти и входу второй группы входов И второго элемента И-ИЛИ-НЕ 49, выход которого соединен со вторым выходом Q2 блока памяти и входом второй группы входов И первого элемента И-ИЛИ-НЕ 48.

Схема фиг.28 работает следующим образом. При низком уровне сигнала на входе I3 блок памяти записывает информацию с входов I1 и I2 в первую бистабильную ячейку на элементах 46 и 47. При высоком уровне (спейсере) сигнала на входе I3 блок памяти хранит состояние первой бистабильной ячейки и переписывает его во вторую бистабильную ячейку на элементах 48 и 49.

На фиг.29 представлена схема блока пре-индикации однотактного самосинхронного RS-триггера с повышенной помехоустойчивостью с входом разрешения записи с нулевым спейсером. Схема содержит два элемента И-НЕ 50-51, первые входы первого 50 и второго 51 элементов И-НЕ подключены к первому X1 и второму Х2 входам блока пре-индикации соответственно, вторые входы первого 50 и второго 51 элементов И-НЕ соединены с третьим Х3 и четвертым Х4 входами блока пре-индикации соответственно, третьи входы первого 50 и второго 51 элементов И-НЕ подключены к пятому входу X5 блока пре-индикации, выходы первого 50 и второго 51 элементов И-НЕ соединены со вторым Y2 и первым Y1 выходами блока пре-индикации соответственно.

На фиг.30 представлена схема блока пре-индикации однотактного самосинхронного RS-триггера с повышенной помехоустойчивостью с входом разрешения записи с единичным спейсером. Схема содержит два элемента ИЛИ-НЕ 52-53, первые входы первого 52 и второго 53 элементов ИЛИ-НЕ подключены к первому X1 и второму Х2 входам блока пре-индикации соответственно, вторые входы первого 52 и второго 53 элементов ИЛИ-НЕ соединены с третьим Х3 и четвертым Х4 входами блока пре-индикации соответственно, третьи входы первого 52 и второго 53 элементов ИЛИ-НЕ подключены к пятому входу X5 блока пре-индикации, выходы первого 52 и второго 53 элементов ИЛИ-НЕ соединены со вторым Y2 и первым Y1 выходами блока пре-индикации соответственно.

На фиг.31 представлена схема блока пре-индикации двухтактного самосинхронного RS-триггера с повышенной помехоустойчивостью с входом разрешения записи с единичным спейсером. Схема содержит два элемента ИЛИ-И-НЕ 54-55, первые входы первых групп входов ИЛИ первого 54 и второго 55 элементов ИЛИ-И-НЕ подключены к первому X1 и второму Х2 входам блока пре-индикации соответственно, вторые входы первых групп входов ИЛИ первого 54 и второго 55 элементов ИЛИ-И-НЕ соединены с седьмым входом блока пре-индикации Х7, входы вторых групп входов ИЛИ первого 54 и второго 55 элементов ИЛИ-И-НЕ подключены к пятому Х5 и шестому Х6 входам блока пре-индикации соответственно, входы третьих групп входов ИЛИ первого 54 и второго 55 элементов ИЛИ-И-НЕ соединены с третьим Х3 и четвертым X4 входами блока пре-индикации соответственно, выходы первого 54 и второго 55 элементов ИЛИ-И-НЕ соединены со вторым Y2 и первым Y1 выходами блока пре-индикации соответственно.

На фиг.32 показана схема блока пре-индикации двухтактного самосинхронного RS-триггера с повышенной помехоустойчивостью с входом разрешения записи с нулевым спейсером. Схема содержит два элемента И-ИЛИ-НЕ 56-57, первые входы первых групп входов И первого 56 и второго 57 эле