Обнаружение преамбул и синхронизация в ofdma-системах беспроводной связи

Иллюстрации

Показать всеИзобретение относится к системам беспроводной связи с множественным доступом с ортогональным частотным разделением каналов (OFDMA) - повышение точности обнаружения преамбулы и синхронизации. Для этого символьная корреляция последовательности символов вычисляется в окне корреляции с помощью одной из корреляции временной области и корреляции частотной области. Последовательность символов принимается согласно способу беспроводной связи с множественным доступом с ортогональным частотным разделением каналов (OFDMA). Символ верифицируется из символьной корреляции. Символ является одним из символа преамбулы и символа данных. 5 н. и 22 з.п. ф-лы, 10 ил.

Реферат

Родственная заявка

Данная заявка притязает на приоритет предварительной заявки, поданной 7 ноября 2006 года, порядковый номер 60/857528, озаглавленной "Preamble detection and synchronization in OFDMA wireless communication systems".

Область техники, к которой относится изобретение

Варианты осуществления изобретения относятся к системам беспроводной связи с множественным доступом с ортогональным частотным разделением каналов (OFDMA), а более конкретно к обнаружению преамбул и синхронизации в OFDMA-системе.

Уровень техники

Среди различных методик передачи информации мультиплексирование с ортогональным частотным разделением каналов (OFDM) считается наиболее перспективным вариантом из-за его устойчивости к межсимвольным помехам, а также высокой эффективности использования спектра.

OFDMA - это многопользовательское OFDM, которое дает возможность осуществлять множественный доступ по одному каналу. В системе с дуплексом с временным разделением каналов OFDMA (TDD) структура кадра конструируется из передач базовой станции (BS) и мобильной абонентской станции (MSS). Базовые станции передают информацию в обслуживаемые мобильные абонентские станции через радиосигналы нисходящей линии связи (DL). Мобильные станции (MS) или абонентские станции (SS) передают информацию в обслуживающие базовые станции через радиосигналы восходящей линии связи (UL). OFDMA распределяет поднесущие между пользователями таким образом, чтобы все активные пользователи могли передавать и принимать одновременно в одном канале.

На основе текущего заданного стандарта WiMAX, IEEE 802.16E, первым символом передачи по нисходящей линии связи является преамбула. Она используется для начальной синхронизации мобильными станциями. Чтобы передавать и принимать кадры, базовая станция и мобильная станция должны добиваться взаимной синхронизации. Чтобы добиваться взаимной синхронизации, MS должна обнаруживать начальную позицию преамбулы, передаваемой от BS.

Существующие методики для синхронизации преамбулы имеют ряд недостатков. Одна основная схема обнаружения преамбул основана на корреляции между циклическим префиксом и последней частью OFDM-символа. Символы в циклическом префиксе копируются из последней части OFDM-символа. Позиция циклического префикса может быть оценена посредством вычисления корреляции между принимаемой последовательностью и ее задержанной версией. Даже если мощность сигнала преамбулы относительно выше мощности обычного символа OFDM-данных, что означает то, что CP-корреляция из преамбулы имеет более высокую выходную корреляцию, по-прежнему трудно отличать преамбулу от обычных OFDM-данных.

Одно возможное решение этой проблемы состоит в том, чтобы верифицировать, исходит ли обнаруженный CP из преамбулы или символа данных. Одна процедура верификации применяет стандарт WiMAX. В стандарте WiMAX предусмотрено 114 псевдошумовых (PN) последовательностей, используемых для преамбулы из различных базовых станций и различных секторов. Верификация может быть выполнена посредством вычисления взаимной корреляции принимаемой последовательности со всеми доступными PN-последовательностями. Эта методика требует высоких вычислительных затрат при выполнении взаимной корреляции. Помимо этого, оценка сдвига частоты на основе циклического префикса не позволяет удалять целочисленный сдвиг частоты, что приводит к тому, что модулированная последовательность сдвигается от одной поднесущей к другой поднесущей. Это дополнительно существенно повышает общие вычисления.

Другая методика состоит в том, чтобы выполнять обнаружение на основе сопряженной симметрии во временной области. Эта методика требует большого числа комплексных умножений для верификации каждой позиции.

Еще одна методика основана на свойстве повторяемости преамбулы. В стандарте WiMAX последовательность преамбул модулируется равномерно на каждой 3-й поднесущей. Сигналы из одного блока коррелируются с сигналами из любого из других двух блоков. Хотя эта схема может быть эффективной в односотовом окружении, она неэффективна в многосотовом окружении, поскольку преамбулы из различных базовых станций модулируются на различных наборах поднесущих.

Сущность изобретения

Вариантом осуществления изобретения является методика для обнаружения преамбул и синхронизации. Символьная корреляция последовательности символов вычисляется в окне корреляции с помощью одного из корреляции временной области и корреляции частотной области. Последовательность символов принимается согласно способу беспроводной связи с множественным доступом с ортогональным частотным разделением каналов (OFDMA). Символ верифицируется из символьной корреляции. Символ является одним из символа преамбулы и символа данных.

Краткое описание чертежей

Варианты осуществления изобретения могут стать более понятными посредством ссылки на последующее описание и прилагаемые чертежи, которые используются для того, чтобы иллюстрировать варианты осуществления изобретения. На чертежах:

фиг.1 является схемой, иллюстрирующей систему согласно одному варианту осуществления изобретения.

Фиг.2 является схемой, иллюстрирующей детектор преамбул/синхронизатор согласно одному варианту осуществления изобретения.

Фиг.3 является схемой, иллюстрирующей корреляции временной области и частотной области согласно одному варианту осуществления изобретения.

Фиг.4 является схемой, иллюстрирующей коррелятор частотной области согласно одному варианту осуществления изобретения.

Фиг.5 является схемой, иллюстрирующей верификатор согласно одному варианту осуществления изобретения.

Фиг.6 является блок-схемой последовательности операций способа, чтобы проиллюстрировать процесс для того, чтобы обнаруживать преамбулу и синхронизироваться согласно одному варианту осуществления изобретения.

Фиг.7A является блок-схемой последовательности операций способа, чтобы проиллюстрировать процесс вычисления символьной корреляции с помощью корреляции временной области согласно одному варианту осуществления изобретения.

Фиг.7B является блок-схемой последовательности операций способа, чтобы проиллюстрировать процесс вычисления символьной корреляции с помощью корреляции частотной области согласно одному варианту осуществления изобретения.

Фиг.8 является блок-схемой последовательности операций способа, чтобы проиллюстрировать процесс верификации символа согласно одному варианту осуществления изобретения.

Фиг.9 является схемой, иллюстрирующей подсистему обработки для того, чтобы реализовать обнаружение преамбул и синхронизацию согласно одному варианту осуществления изобретения.

Подробное описание изобретения

Вариантом осуществления изобретения является методика для обнаружения преамбул и синхронизации. Символьная корреляция последовательности символов вычисляется в окне корреляции с помощью одного из корреляции временной области и корреляции частотной области. Последовательность символов принимается согласно способу беспроводной связи с множественным доступом с ортогональным частотным разделением каналов (OFDMA). Символ верифицируется из символьной корреляции. Символ является одним из символа преамбулы и символа данных.

В последующем описании изложены многочисленные конкретные детали. Однако понятно, что варианты осуществления изобретения могут быть применены на практике без этих конкретных деталей. В других случаях хорошо известные схемы, структуры и методики не показаны, чтобы не затруднять понимание данного описания.

Один вариант осуществления изобретения может быть описан как процесс, который обычно изображается как блок-схема, блок-схема последовательности операций способа, структурная схема или функциональная схема. Хотя блок-схема последовательности операций способа может описывать операции как последовательный процесс, многие операции могут выполняться параллельно или одновременно. Помимо этого, порядок операций может быть переопределен. Процесс завершается, когда его операции закончены. Процесс может соответствовать способу, программе, процедуре, способу производства или изготовления и т.д.

Варианты осуществления изобретения включают в себя способ обнаружения временной синхронизации в системе беспроводной связи OFDMA. Способ включает в себя две фазы: первая фаза используется для приблизительного обнаружения границ OFDM-символа на основе корреляции циклического префикса; а вторая фаза используется для того, чтобы верифицировать, является текущий символ символом OFDM-преамбулы или символом OFDM-данных. Вторая фаза также может использоваться для того, чтобы оценивать точную границу символа. Процедура верификации основана на сопряженной симметрии OFDM-преамбулы, модулированной в соответствии с двухпозиционной фазовой манипуляцией (BPSK). Предусмотрено два альтернативных подхода для этой процедуры: схема обработки временной области и схема обработки частотной области. Чтобы определять, является ли текущий символ модулированным согласно BPSK OFDM-символом, максимум выходной корреляции и сумма числа максимальных выходных корреляций сравниваются со своими соответствующими предварительно установленными пороговыми значениями. Кроме того, вторая фаза может быть применена к обнаружению сигналов и оценке границ символов для модулированных согласно BPSK OFDM-символов.

Фиг.1 является схемой, иллюстрирующей систему 100 согласно одному варианту осуществления изобретения. Система 100 включает в себя базовую станцию (BS) 110 и N мобильных станций (MS) 1401-140N. Отметим, что система 100 может включать в себя большее или меньшее число компонентов, чем указано выше.

BS 110 является станцией, установленной в фиксированном или мобильном местоположении, чтобы обмениваться данными с N MS 1401-140N в режиме беспроводной связи через радиочастотную (RF) передачу. Беспроводная связь может соответствовать стандарту общемировой совместимости широкополосного беспроводного доступа (WiMAX). Местоположение может быть в разреженной или плотно заполненной области или может быть для применения в автотранспортных средствах. BS 110 включает в себя BS-процессор 120 и передающее/приемное BS-устройство 130.

BS-процессор 120 включает в себя требуемые компоненты для операций BS. Он может включать в себя генератор для того, чтобы предоставлять источники синхросигналов или синхросигналы в различные компоненты в таком модуле, как аналого-цифровой преобразователь (ADC), цифроаналоговый преобразователь (DAC) и другие логические схемы; один или более процессоров, таких как процессор цифровых сигналов (DSP), для того чтобы осуществлять различные функции или выполнять программы; модули или схемы автоматической регулировки усиления (AGC), автоматического регулирования частоты (AFC) и канального кодирования/декодирования и т.д. BS-процессор 120 включает в себя формирователь 125 BS-символов для того, чтобы формировать последовательность символов для передачи в N MS 1401-140N.

Передающее/приемное BS-устройство 130 может включать в себя передающий и приемный модуль, чтобы передавать и принимать RF-сигналы. Оно может включать в себя высокомощную антенну. Антенна может быть установлена на крыше, вышке или вершине в зависимости от типа или ландшафта и требуемой зоны покрытия.

N станций MS 1401-140N могут включать в себя любое устройство MS, такое как переносной телефонный аппарат, сотовый телефон, персональное цифровое устройство (PDA), портативный компьютер, дорожный компьютер, или любое устройство, которое допускает выполнение функциональности MS в сети беспроводной связи. Каждая из N MS 1401-140N может подписываться на услуги мобильной связи, предоставляемые посредством BS 110. Каждая из N MS 1401-140N может включать в себя радиочастотное (RF) приемное устройство для того, чтобы принимать радиосигнал, переносящий последовательность символов, от BS 110 согласно способу беспроводной связи с множественным доступом с ортогональным частотным разделением каналов (OFDMA), детектор преамбул и синхронизатор i (i=1, …, N) для того, чтобы обнаруживать символы преамбулы и синхронизировать кадры, модуль удаления циклического префикса (CP) для того, чтобы удалять CP, процессор быстрого преобразования Фурье (FFT) для того, чтобы вычислять FFT, канальный компенсатор, модуль оценки канала, декодер, модуль обратного перемежения и другие схемы или модули для того, чтобы выполнять функции приема. Каждая из N MS 1401-140N также может включать в себя канальный кодер и модуль перемежения, модуль преобразования согласно двухпозиционной фазовой манипуляции (BPSK), процессор обратного FFT (IFFT), процессор обработки циклического префикса и кодирования с взвешиванием и передающее RF-устройство, а также другие схемы или модули для того, чтобы выполнять функции передачи.

BS 110 и N MS 1401-140N обмениваются данными друг с другом согласно заранее заданному протоколу или стандарту связи. В одном варианте осуществления стандартом связи является стандарт Института инженеров по электронике и радиотехнике (IEEE) 802.16e или стандарт Европейского института стандартизации в области телекоммуникаций (ETSI) Общегородская радиосеть с высокой производительностью (HiperMAN) 1.3.2. MS-детектор преамбул/синхронизатор 145i предоставляет эффективное обнаружение преамбулы для кадровой синхронизации. BS 110 и N MS 1401-140N могут включать признаки управления доступом к среде передачи (MAC) и физического уровня (PHY) в типичную систему WiMAX. Система WiMAX использует схему множественного доступа с ортогональным частотным разделением каналов (OFDMA) для окружений с многолучевым распространением.

Фиг.2 является схемой, иллюстрирующей детектор преамбул/синхронизатор 145i согласно одному варианту осуществления изобретения. Для краткости, нижний индекс "I" может быть отброшен. Детектор преамбул/синхронизатор 145 включает в себя коррелятор 210 и верификатор 240. Детектор преамбул/синхронизатор 145 может включать в себя большее или меньшее число компонентов, чем указано выше. Помимо этого, он может быть реализован посредством аппаратных средств, микропрограммного обеспечения или программного обеспечения либо любой комбинации вышеозначенного.

Коррелятор 210 вычисляет символьную корреляцию последовательности символов в окне корреляции L с использованием одного из коррелятора 220 временной области и коррелятора 230 частотной области. Последовательность символов принимается согласно способу беспроводной связи OFDMA. Последовательность символов может представлять любые символы, формируемые посредством передающего устройства (к примеру, BS 110). Символы могут формировать циклический префикс (CP), используемый в преамбуле, или могут представлять символы данных, которые являются частью информационного сообщения.

Коррелятор 220 временной области вычисляет символьную корреляцию во временной области с использованием сопряженной симметричной последовательности в окне верификации K. Окно верификации является меньшим, чем окно корреляции, т.е. его длина меньше, чем у окна корреляции L. Окно верификации K может быть представлено посредством минимального индекса -K w и максимального индекса K w, где длина окна K=2K w+1. Например, если K w=3, то окно верификации K имеет индексы -3, -2, -1, 0, 1, 2, 3.

Коррелятор 230 частотной области вычисляет символьную корреляцию в частотной области посредством преобразования корреляции в циркулярную свертку. Циркулярная свертка может быть вычислена во временной области или в частотной области. Свертка частотной области является более эффективной вследствие доступности быстрого преобразования Фурье (FFT) для быстрого вычисления преобразования Фурье (FT). Кроме того, вычисление FFT типично уже доступно в приемном устройстве MS 140. Следовательно, дополнительные аппаратные средства или программное обеспечение могут не требоваться для вычислений FFT.

Верификатор 240 соединен с коррелятором 210 для того, чтобы верифицировать символ из символьной корреляции. Символ является одним из символа преамбулы и символа данных. Если это символ преамбулы, то кадровая синхронизация может быть получена.

Обнаруженный символ, будь то символ преамбулы или символ данных, может затем обрабатываться посредством постпроцессора 250. Постпроцессор 250 может включать другие компоненты приемного устройства в MS 140 для того, чтобы выполнять задачи приемного устройства, такие как удаление CP, восстановление данных с помощью FFT, частотная коррекция канала, оценка канала, декодирование, обратное перемежение и т.д.

Фиг.3 является схемой, иллюстрирующей корреляции 320 и 330 временной области и частотной области согласно одному варианту осуществления изобретения. Корреляции выполняются для принимаемой последовательности символов 310.

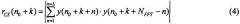

При условии последовательности x(n) корреляция последовательности x(n) вычисляется согласно следующему выражению:

где x(n) - это принимаемая последовательность во временной области, а N FFT - это число точек в вычислении FFT.

Сопряженная симметрия во временной области может быть описана как:

где y * - это комплексно-сопряженное y.

Из этого обнаружение преамбул на основе сопряженной симметрии может моделироваться следующим образом:

где L - это длина или размер окна корреляции, которая меньше N FFT/2.

В корреляции временной области при допущении, что n 0 - это начальная позиция полезной части последовательности символов, полученных из обнаружения на основе CP, уравнение (3) может модифицироваться следующим образом:

где k=-K W,…, K W, а K=2K W+1 - это длина окна верификации.

Корреляция временной области, следовательно, вычисляет только (2K W+1) корреляций сопряженной симметрии вместо всех корреляций L сопряженной симметрии. Соответственно, число вычислений меньше, чем при стандартной методике.

Корреляция временной области вычисляет символьную корреляцию с помощью уравнения (4). Это вычисление может быть проиллюстрировано графически посредством корреляции 320 временной области, показанной на фиг.3. При корреляции 320 временной области принимаемая последовательность и ее сопряженная симметрия сдвигаются в противоположных направлениях.

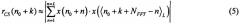

При корреляции частотной области корреляция, заданная в уравнении (4), может быть преобразована в циркулярную свертку следующим образом. Уравнение (4) может рассматриваться как корреляция двух последовательностей S1 и S2. Для каждого отличного значения k последовательность S1 может быть сдвинута влево или вправо, тогда S2 может быть сдвинута вправо или влево на основе знака k. Тем не менее, большинство элементов в различной последовательности являются неизменными, когда k намного меньше L. На основе этого наблюдения уравнение (4) может быть аппроксимировано следующим образом:

где обозначает по модулю L.

Из уравнения (5) можно видеть, что последовательность S1 является фиксированной для различных значений k, тогда как последовательность S2 циркулярно сдвигается на основе значения k. Это может быть проиллюстрировано графически посредством корреляции 330 частотной области.

Уравнение (5) может рассматриваться как циркулярная свертка двух последовательностей. Без потери общности n 0 может считаться равным нулю для простоты. Последовательности S1 и S2 могут быть перезаписаны следующим образом:

где RCS - это свертка S1 и S2. Тогда:

S1 - это первая последовательность в последовательности символов x(n)=[x(1) x(2) …, x(N FFT-1), x(N FFT)]. S2 - это переупорядоченная последовательность из второй последовательности S'2=[x(N FFT-L), x(N FFT-(L+1)) …, x(N FFT-1), x(N FFT)]. Следует отметить, что хотя корреляция частотной области использует два FFT и одно IFFT, она не представляет дополнительных вычислительных затрат для приемного устройства в MS 140, поскольку операции FFT и IFFT уже реализованы в приемо-передающем устройстве OFDM.

Помимо этого, корреляция частотной области увеличивает размер окна верификации без увеличения вычислительной сложности. При корреляции временной области сложность вычисления пропорциональна к размеру окна верификации в K w. При корреляции частотной области размер окна верификации может быть такого размера, как L/4.

Кроме того, методика корреляции частотной области увеличивает выигрыш при обработке при затратах с относительно низкой сложностью. Выигрыш при обработке пропорционален размеру окна корреляции L. Когда размер окна увеличивается с L до 2L, алгоритм обработки временной области требует дополнительных (2K w+1)L комплексных вычислений, тогда как методика корреляции частотной области требует только L дополнительных комплексных вычислений. Как пояснено выше, дополнительные операции, связанные с FFT/IFFT, могут быть проигнорированы, поскольку они не вводят новые аппаратные средства для приемного устройства.

Кроме того, методики корреляции в вариантах осуществления изобретения предоставляют точную оценку границы символа без дополнительных затрат. Традиционная оценка границы основана на циклическом префиксе, где корреляционная функция является треугольником. Граница оценивается на основе позиции треугольного пика. Из-за различных помех оценка границы является не очень точной. С другой стороны, корреляция на основе сопряженной симметрии является дельта-функцией, что означает, что показатель синхронизации имеет гораздо более высокое пиковое значение в корректной позиции символьной синхронизации, чем значения в других позициях. Следовательно, он может предоставлять гораздо более точную оценку границы, чем схема на основе CP.

Фиг.4 является схемой, иллюстрирующей коррелятор 230 частотной области, показанный на фиг.2, согласно одному варианту осуществления изобретения. Коррелятор 230 частотной области включает в себя модуль 410 свертки и модуль 460 обратного FT. Коррелятор 230 частотной области может включать в себя большее или меньшее число компонентов, чем указано выше.

Модуль 410 свертки частотной области вычисляет циркулярную свертку частотной области для последовательности символов. Он включает в себя первый модуль 420 FT, оператор 430 переупорядочения и комплексного сопряжения, второй модуль 440 FT, оператор 445 комплексного сопряжения и умножитель 450. Первый модуль 420 FT вычисляет первую FT-последовательность из первой последовательности S1 в последовательности символов, имеющей длину окна корреляции L. Оператор 430 переупорядочения и комплексного сопряжения выполняет операцию переупорядочения и комплексного сопряжения для второй последовательности S'2 в последовательности символов. Он может включать в себя модуль преобразования индексов, который преобразует индекс в индекс симметрии, как показано в уравнениях (6b) и (7). Второй модуль 440 FT вычисляет вторую FT-последовательность из переупорядоченной и комплексно-сопряженной второй последовательности, имеющей длину окна корреляции L. Оператор 445 комплексного сопряжения выполняет операцию комплексного сопряжения для вывода второго FT 440. Умножитель 450 умножает первую FT-последовательность и комплексно-сопряженную вторую FT-последовательность, чтобы предоставлять циркулярную свертку частотной области.

Модуль 460 обратного преобразования Фурье (FT) соединен с модулем 410 свертки для того, чтобы вычислять обратное преобразование Фурье (FT) циркулярной свертки, чтобы предоставлять символьную корреляцию. Как правило, первый и второй модули FT используют FFT для того, чтобы выполнять вычисления FT. Модуль 460 обратного FT использует IFFT для того, чтобы выполнять вычисление обратного FT.

Фиг.5 является схемой, иллюстрирующей верификатор 240, показанный на фиг.2, согласно одному варианту осуществления изобретения. Верификатор 240 включает в себя пиковый детектор 510, сумматор 520, первый и второй модули 530 и 540 сравнения и детектор 550. Верификатор 240 может включать в себя большее или меньшее число компонентов, чем указано выше.

Пиковый детектор 510 определяет максимальное значение символьной корреляции в максимальной позиции k 0 515. Пиковый детектор 510 также определяет K наибольших значений при символьной корреляции, где K - это заранее определенное положительное целое число. Пиковый детектор 510, следовательно, может использоваться для того, чтобы выполнять две функции: одна заключается в том, чтобы определять максимальное значение, а другая заключается в том, чтобы определять K наибольших значений, которые включают в себя максимальное значение. Сумматор 520 вычисляет сумму K наибольших значений символьной корреляции. K наибольших значений имеют максимальное значение в максимальной позиции k 0 515. Первый модуль сравнения 530 сравнивает максимальное значение с первым пороговым значением TH1 535. Второй модуль сравнения 540 сравнивает сумму со вторым пороговым значением TH2 545.

Детектор 550 может обнаруживать символ как символ преамбулы в максимальной позиции k 0, если максимальное значение превышает первое пороговое значение TH1. Когда k 0≤L/2, индекс, соответствующий начальной позиции полезной части преамбулы, находится в правой стороне обнаруженной границы символа на основе CP-обнаружения или индекс (n 0+k 0/2). Когда k 0>L/2, индекс, соответствующий начальной позиции полезной части преамбулы, находится в левой стороне обнаруженной границы символа на основе CP-обнаружения или индекс (n 0-(L-k 0)/2). Детектор 550 также может обнаруживать символ как символ преамбулы, если сумма превышает второе пороговое значение TH2. Начальная позиция вычисляется на основе k 0, как в случае первого порогового значения.

Детектор 550 может обнаруживать символ как символ данных или объявлять ошибку верификации, если максимальное значение не превышает первое пороговое значение TH1 535 и сумма не превышает второе пороговое значение TH2 545. Детектор 550 может быть логической схемой, которая объявляет символ обнаруженным как символ преамбулы, если, по меньшей мере, один из модулей 530 и 540 сравнения указывает, что или максимальное значение больше TH1, или сумма больше TH2. Если оба из модулей сравнения 530 и 540 указывают то, что ни одно из пороговых значений не превышено, то он объявляет, что верификация завершилась ошибкой или символ преамбулы не обнаружен.

Фиг.6 является блок-схемой последовательности операций способа, чтобы проиллюстрировать процесс 600 для того, чтобы обнаруживать преамбулу и синхронизироваться согласно одному варианту осуществления изобретения.

После начала процесс 600 вычисляет символьную корреляцию последовательности символов в окне корреляции L с помощью одного из корреляции временной области и корреляции частотной области (этап 610). Последовательность символов принимается согласно способу беспроводной связи с множественным доступом с ортогональным частотным разделением каналов (OFDMA). Затем процесс 600 верифицирует символ из символьной корреляции (этап 620) и после этого завершается. Символ является одним из символа преамбулы и символа данных. Верификация должна верифицировать, есть ли символ преамбулы в последовательности. Если преамбула не обнаружена, верификация формирует результат ошибки и процесс ожидает следующего обнаружения.

Фиг.7A является блок-схемой последовательности операций способа, чтобы проиллюстрировать процесс 610, показанный на фиг.6, для того чтобы вычислять символьную корреляцию с помощью корреляции временной области согласно одному варианту осуществления изобретения. Процесс 610 вычисляет символьную корреляцию с помощью сопряженной симметричной последовательности в окне верификации K. Окно верификации K меньше окна корреляции L.

После начала процесс 610 инициализирует индекс k как -Kw (этап 710). Затем процесс 610 вычисляет символьную корреляцию RCS(k) с помощью уравнения (4) (этап 715). Далее процесс 610 обновляет индекс k, к примеру задает k=k+1 (этап 720). Затем процесс 610 определяет, превышает ли k наибольший индекс Kw (этап 725). Если нет, процесс 610 возвращается к этапу 715, чтобы продолжить вычислять символьную корреляцию. В противном случае процесс 610 завершается.

Фиг.7B является блок-схемой последовательности операций способа, чтобы проиллюстрировать процесс 610, показанный на фиг.6, для того чтобы вычислять символьную корреляцию с помощью корреляции частотной области согласно одному варианту осуществления изобретения.

После начала процесс 610 вычисляет циркулярную свертку частотной области последовательности символов (этап 730). Затем процесс 610 вычисляет обратное преобразование Фурье (FT) циркулярной свертки, чтобы предоставлять символьную корреляцию (этап 760), и после этого завершается.

Процесс 730 может быть выполнен следующим образом. Сначала процесс 730 вычисляет первую FT-последовательность из первой последовательности в последовательности символов, имеющей длину окна корреляции L (этап 735). Первая последовательность - это последовательность S1, показанная в уравнении (6a). После этого процесс 730 определяет переупорядоченную и комплексно-сопряженную вторую последовательность в последовательности символов (этап 740). Вторая последовательность - это последовательность S2. Это может влечь за собой выполнение переупорядочения индексного преобразования для второй последовательности и операцию комплексного сопряжения для переупорядоченной второй последовательности. Переупорядоченная вторая последовательность - это последовательность S2 в уравнении (6b). Затем процесс 730 вычисляет вторую FT-последовательность переупорядоченной и комплексно-сопряженной второй последовательности, имеющей длину окна корреляции L (этап 745). Далее процесс 730 выполняет операцию комплексного сопряжения для второй FT-последовательности (этап 750). Затем процесс 730 умножает первую FT-последовательность и комплексно-сопряженную вторую FT-последовательность, чтобы предоставлять циркулярную свертку частотной области (этап 750), и после этого завершается.

Фиг.8 является блок-схемой последовательности операций способа, чтобы проиллюстрировать процесс 620, показанный на фиг.6, для того чтобы верифицировать символ согласно одному варианту осуществления изобретения.

После начала процесс 620 определяет максимальное значение Cmax символьной корреляции в максимальной позиции k0 (этап 810). Затем процесс 620 вычисляет сумму значений S символьной корреляции в позициях вокруг центральной позиции kc (этап 820). Затем процесс 620 сравнивает максимальное значение с первым пороговым значением TH1 (этап 830). Далее процесс 620 сравнивает сумму со вторым пороговым значением TH2 (этап 840). Отметим, что порядок этапов 830 и 840 является несущественным.

После этого процесс 620 определяет, больше ли максимальное значение Cmax первого порога TH1 или больше ли сумма S второго порогового значения TH2 (этап 850). Если так, процесс 620 определяет символ как символ преамбулы в максимальной позиции k0 (если Cmax больше первого порогового значения TH1) или в центральной позиции (если сумма S больше второго порогового значения TH2) и после этого завершается. Иначе, т.е. если максимальное значение Cmax не превышает первое пороговое значение и сумма S не превышает второе пороговое значение, процесс 620 определяет символ как символ данных или объявляет ошибку верификации. Процесс 620 затем завершается.

Фиг.9 является схемой, иллюстрирующей процессор 900, чтобы реализовать обнаружение преамбул и синхронизацию 145i, показанные на фиг.1, согласно одному варианту осуществления изобретения. Процессор 900 включает в себя процессор 910, контроллер запоминающего устройства (MC) 920, основное запоминающее устройство 930, контроллер ввода-вывода (IOC) 940, межкомпонентное соединение 945, интерфейс 950 запоминающего устройства большой емкости, устройства 9471-947K ввода-вывода (I/O) и сетевую интерфейсную плату (NIC) 960. Процессор 900 может включать в себя большее или меньшее число компонентов, чем указано выше.

Процессор 910 представляет центральный процессор архитектуры любого типа, такой как процессоры, использующие технологии hyper threading, безопасности, сетевые, цифровые мультимедийные технологии, одноядерные процессоры, многоядерные процессоры, встроенные процессоры, мобильные процессоры, микроконтроллеры, цифровые процессоры сигналов, суперскалярные компьютеры, векторые процессоры, компьютеры с архитектурой "один поток команд - много потоков данных" (SIMD), компьютеры со сложным набором команд (CISC), компьютеры с сокращенным набором команд (RISC), архитектуру с системой команд сверхбольшой разрядности (VLIW) или гибридную архитектуру.

MC 920 предоставляет управление и конфигурирование запоминающего устройства и устройств ввода-вывода, таких как основное запоминающее устройство 930 и IOC 940. MC 920 может быть интегрирован в набор микросхем, который интегрирует несколько видов функциональности, таких как графика, мультимедиа, изолированный режим выполнения, интерфейс шины "хост-периферийное-устройство", управление запоминающим устройством, управление питанием и т.д. MC 920 или функциональность контроллера запоминающего устройства в MC 920 может быть интегрирована в процессоре 910. В некоторых вариантах осуществления контроллер запоминающего устройства, внутренний или внешний для процессора 910, может работать во всех ядрах или процессорах в процессоре 910. В других вариантах осуществления он может включать в себя различные части, которые могут работать отдельно для различных ядер или процессоров в процессоре 910.

Основное запоминающее устройство 930 хранит системный код и данные. Основное запоминающее устройство 930 типично осуществлено с помощью динамической оперативной памяти (DRAM), статической оперативной памяти (SRAM) или любых других типов памяти, включающих в себя те, которые не нужно обновлять. Основное запоминающее устройство 930 может включать в себя несколько каналов запоминающих устройств, таких как DRAM. DRAM могут включать в себя устройства с двойной скоростью передачи данных (DDR2) с полосой пропускания в 8,5 гигабайтов в секунду (Гб/с). В одном варианте осуществления запоминающее устройство 930 может включать в себя модуль 935 обнаружения преамбул/синхронизации. Модуль 935 обнаружения преамбул/синхронизации может выполнять все или некоторые из функций, описанных выше.

IOC 940 имеет ряд функциональностей, которые предназначены, чтобы поддерживать функции ввода/вывода. IOC 940 также может быть объединен в набор микросхем вместе или отдельно от MC 920, чтобы выполнять функции ввода/вывода. IOC 940 может включать в себя ряд интерфейсных функций и функций ввода/вывода, например интерфейс шины межкомпонентного соединения периферийных компонентов (PCI), интерфейс процессора, контроллер прерывания, контроллер прямого доступа к памяти (DMA), логику управления питанием, таймер, шину управления системой (SMBus), интерфейс универсальной последовательной шины (USB), интерфейс запоминающего устройства большой емкости, интерфейс с низким числом выводов (LPC), беспроводное межкомпонентное соединение, прямой мультимедийный интерфейс (DMI) и т.д.

Межкомпонентное соединение 945 предоставляет интерфейс с периферийными устройствами. Межкомпонентное соединение 945 может иметь тип "точка-точка" или подключаться к нескольким устройствам. Для ясности показаны не все межкомпонентные соединения. Предполагается, что межкомпонентное соединение 945 может включать в себя любое межкомпонентное соединение или шину, такую как межкомпонентное соединение периферийных компонентов (PCI), PCI Express, универсальная