Устройство для сопряжения источника и приемника информации

Иллюстрации

Показать всеИзобретение относится к автоматике и вычислительной технике и может быть использовано в локальных вычислительных сетях. Техническим результатом является расширение функциональных возможностей устройства для сопряжения источника и приемника информации за счет обеспечения доступа к двум общим шинам с динамически меняющимся интервалом передачи. Он достигается тем, что принципы работы данного изобретения сводятся к реализации алгоритма интервально-маркерного метода доступа к двум общим шинам с динамически меняющимся интервалом передачи. В устройство дополнительно введены второй блок буферной памяти, схема приема сигналов со второй шины, схема передачи сигналов во вторую шину и схема обработки сигналов с обеих шин в управляющем блоке, а также соответствующие связи между указанными элементами. 12 ил.

Реферат

Изобретение относится к автоматике и вычислительной технике и может быть использовано в локальных вычислительных сетях (ЛВС) в качестве станции ЛВС, реализующей интервально-маркерный метод доступа к двум общим шинам с динамически меняющимся интервалом передачи.

Наиболее близким к предлагаемому изобретению техническим решением является устройство для сопряжения источника и приемника информации [1].

Недостатком известного устройства является ограниченные функциональные возможности.

Целью предлагаемого изобретения является расширение функциональных возможностей устройства.

Поставленная цель достигается тем, что в устройство, содержащее входной регистр, блок элементов И, первый, второй и третий элементы задержки, первый и второй элементы ИЛИ, схему сравнения, первый и второй счетчики адреса, триггер, первый и второй элементы И, блок памяти (БП), содержащий первый и второй дешифраторы, блок элементов ИЛИ, N информационных регистров, N блоков элементов И первой группы, N блоков элементов И второй группы, информационный вход устройства, вход стробирования записи устройства, вход стробирования чтения устройства, вход начальной установки устройства, информационный выход устройства, выход "Готовность записи" устройства и выход "Готовность чтения" устройства, причем первый вход первого элемента ИЛИ является входом начальной установки устройства, выход первого элемента ИЛИ соединен со входами установки первого счетчика адреса, триггера и с установочными входами N информационных регистров, первый вход блока элементов И является информационным входом устройства, второй вход блока элементов И соединен со входом первого элемента задержки и является входом стробирования записи устройства, выход блока элемента И соединен с информационным входом входного регистра, выход которого соединен с соответствующими информационными входами N блоков элементов И первой группы, выходы которых соединены с входами данных N информационных регистров, выходы которых соединены с информационными входами N блоков элементов И второй группы, выходы которых соединены с соответствующими входами блока элементов ИЛИ, выход которого является информационным выходом устройства, выходы первого счетчика адреса соединены со входами первого дешифратора, выходы которого соединены с соответствующими стробирующими входами N блоков элементов И второй группы, выход первого элемента задержки соединен с первым входом первого элемента И, выход которого соединен с соответствующими первыми стробирующими входами N блоков элементов И первой группы и с входом второго элемента задержки, выход которого соединен со счетным входом второго счетчика адреса, выход переполнения которого соединен с единичным входом триггера, прямой и инверсный выходы которого соединены соответственно с первым входом второго элемента ИЛИ и вторым входом первого элемента И, инверсный выход триггера является выходом готовности записи устройства, выход второго элемента ИЛИ соединен с первым входом второго элемента И, второй вход которого является входом стробирования чтения устройства, а выход второго элемента ИЛИ является выходом готовности чтения устройства, выход второго элемента И соединен с вторыми стробирующими входами N блоков элементов И второй группы и с входом третьего элемента задержки, выход которого соединен со счетным входом первого счетчика адреса, выход переполнения которого соединен со вторым входом первого элемента ИЛИ, выход которого соединен с установочным входом второго счетчика адреса, информационные выходы которого соединены с входами второго дешифратора адреса и с первой группой входов схемы сравнения, вторая группа входов которой соединена с информационными выходами первого счетчика адреса, выход схемы сравнения соединен с вторым входом второго элемента ИЛИ, выходы второго дешифратора соединены с соответствующими вторыми стробирующими входами N блоков элементов И первой группы, второй блок буферной памяти (ББП2), блок приемника (ПРМ), блок передатчика (ПРД) и управляющий блок (УУ), первый информационный вход устройства, первый информационный выход устройства, вход стробирования чтения устройства, первый вход начальной установки устройства, вход кода адреса устройства, вход кода "маркер" устройства, вход кода "конец сообщения" устройства, вход кода длины сообщения устройства, вход "код интервала" устройства, выход "сообщение передано" устройства, выход "восстановить таймер" устройства, второй информационный вход устройства, вход стробирования записи устройства, второй вход начальной установки устройства, второй информационный выход устройства, причем информационный вход ПРМ является первым информационным входом устройства, вход кода "конец сообщения" ПРМ соединен со входом кода "конец сообщения" ПРД и является входом кода конца сообщения устройства, вход кода "маркер" ПРМ соединен с входом кода "маркер" ПРД и является входом кода маркера устройства, вход кода адреса ПРМ является входом кода адреса устройства, информационный выход ПРМ соединен с информационным входом первого блока буферной памяти (ББП1), выход стробирования записи ПРМ соединен со входом стробирования записи ББП1, выход "маркер" ПРМ соединен со входом "маркер" УУ, вход стробирования чтения ББП1 является входом стробирования чтения устройства, вход начальной установки ББП1 является первым входом начальной установки устройства, информационный выход ББП1 является первым информационным выходом устройства, вход кода длины сообщения УУ является входом кода длины сообщения устройства, вход "код интервала" УУ является входом кода интервала устройства, выход "сообщение передано" УУ является выходом устройства "сообщение передано", выход "восстановить таймер" УУ является выходом устройства "восстановить таймер", выход "0 счетчика слов" УУ соединен со входом "0 счетчика слов" ПРД, выход ТИ УУ соединен со входом ТИ ПРД, выход "запуск" УУ соединен со входом "запуск" ПРД, выход "передать маркер" УУ соединен со входом "передать маркер" ПРД, выход "0 таймера" УУ соединен со входом "0 таймера" ПРД, информационный вход ББП2 является вторым информационным входом устройства, вход стробирования записи ББП2 является входом стробирования записи устройства, вход начальной установки ББП2 является вторым входом начальной установки устройства, информационный выход ББП2 соединен с информационным входом ПРД, выход стробирования чтения которого соединен со входом стробирования чтения ББП2 и со входом стробирования чтения УУ, информационный вход ПРД является вторым информационным выходом устройства,

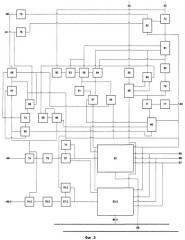

блок приемника содержит блок приема сигналов, буферный регистр, выходной регистр, схему выделения байта "маркер", схему выделения байта "конец сообщения", схему сравнения адресов, триггер разрешения сравнения адресов, триггер приема информации, счетчик байтов, первый, второй и третий элементы задержки, первый, второй и третий элементы И, первый и второй элементы ИЛИ, блок элементов И, информационный вход ПРМ, вход кода "конец сообщения" ПРМ, вход кода адреса ПРМ, информационный выход ПРМ, выход стробирования записи ПРМ, выход "маркер" ПРМ, причем вход блока приема сигналов является информационным входом ПРМ, первый выход которого соединен со входом буферного регистра, выход которого соединен с первым входом схемы выделения байта "маркер", с первым входом схемы выделения байта "конец сообщения", с первым входом схемы сравнения адресов и с первым входом блока элементов И, выход которого соединен со входом выходного регистра, выход которого является информационным выходом ПРМ, второй выход блока приема сигналов соединен со входом первого элемента задержки, выход которого соединен с третьим входом схемы выделения байта "конец сообщения", с третьим входом схемы сравнения адресов, с первым входом первого элемента И и с третьим входом схемы выделения байта "маркер", выход которого является выходом "маркер" ПРМ и соединен с первым входом первого элемента ИЛИ, выход которого соединен со вторым входом триггера разрешения сравнения адресов, выход которого соединен со вторым входом первого элемента И и с четвертым входом схемы сравнения адресов, выход которого соединен со вторым входом триггера приема информации, выход которого соединен с первым входом второго элемента И, выход которого соединен со входом третьего элемента задержки, с третьим входом блока элементов И и со входом счетчика байтов, первый выход которого соединен со вторым входом блока элементов И, второй выход счетчика байтов соединен с первым входом третьего элемента И, выход которого является выходом стробирования записи ПРМ, третий выход блока приема сигналов соединен с первым входом второго элемента ИЛИ, выход которого соединен с первым входом триггера разрешения сравнения адресов, второй вход схемы выделения байта "маркер" является входом кода "маркер" ПРМ, второй вход схемы сравнения адресов является входом кода адреса ПРМ, второй вход схемы выделения байта "конец сообщения" является входом кода "конец сообщения" ПРМ, первый выход схемы выделения байта "конец сообщения" соединен со вторым входом первого элемента ИЛИ и с первым входом триггера приема информации, второй выход схемы выделения байта "конец сообщения" соединен со входом второго элемента задержки, выход которого соединен со вторым входом второго элемента И, выход третьего элемента задержки соединен со вторым входом третьего элемента И, выход первого элемента И соединен со вторым входом второго элемента ИЛИ,

блок передатчика содержит блок формирования манчестерского кода, счетчик байтов, регистр приема информации, триггер передачи, триггер маркера, триггер конца сообщения буферный, триггер конца сообщения, триггер конца передачи, блок элементов И-ИЛИ, одиннадцать элементов И, четыре элемента ИЛИ, два элемента НЕ, шесть элементов задержки, информационный вход ПРД, вход кода "конец сообщения" ПРД, вход кода "маркер" ПРД, вход ТИ ПРД, вход "запуск" ПРД, вход "передать маркер" ПРД, вход "0 таймера" ПРД, вход "0 счетчика слов" ПРД, информационный выход ПРД, выход стробирования чтения ПРД, причем вход регистра приема информации является информационным входом ПРД, выход регистра приема информации соединен с первым входом блока элементов И-ИЛИ, выход которого соединен с первым входом блока формирования манчестерского кода, первый выход которого является информационным выходом ПРД, второй вход блока формирования манчестерского кода является входом ТИ ПРД, третий вход блока формирования манчестерского кода является входом кода "маркер" ПРД, четвертый вход блока формирования манчестерского кода является входом кода "конец сообщения" ПРД, второй выход блока формирования манчестерского кода соединен с третьим входом седьмого элемента И, со вторым входом восьмого элемента И, с первым входом девятого элемента И, с первым входом одиннадцатого элемента И, со вторым входом шестого элемента И, с четвертым входом первого элемента И и с четвертым входом третьего элемента И, выход которого соединен с первым входом второго элемента ИЛИ, выход которого является выходом стробирования чтения ПРД и соединен со входом четвертого элемента задержки, выход которого соединен с третьим входом четвертого элемента И, выход которого соединен с первым входом триггера конца сообщения буферного, первый выход которого соединен с первым входом пятого элемента И, второй выход триггера конца сообщения буферного соединен с первым входом четвертого элемента И и со вторым входом второго элемента И, выход которого соединен со вторым входом второго элемента ИЛИ, вход первого элемента задержки является входом "запуск" ПРД, выход первого элемента задержки соединен с первым входом первого элемента ИЛИ, выход которого соединен с четвертым входом блока элементов И-ИЛИ и со входом второго элемента задержки, выход которого соединен со входом счетчика байтов, с первым входом десятого элемента И и со входом шестого элемента задержки, выход которого соединен с третьим входом второго элемента И и со вторым входом пятого элемента И, выход которого соединен с первым входом триггера конца сообщения, первый выход которого соединен с третьим входом третьего элемента И, со вторым входом седьмого элемента И, с третьим входом девятого элемента И, с седьмым входом блока формирования манчестерского кода и с первым входом шестого элемента И, выход которого соединен со вторым входом триггера конца сообщения буферного и со входом пятого элемента задержки, выход которого соединен со вторым входом триггера конца сообщения, второй выход которого соединен с первым входом первого элемента И, выход которого соединен со вторым входом первого элемента ИЛИ, первый вход четвертого элемента ИЛИ является входом "передать маркер" ПРД выход которого соединен со входом третьего элемента задержки, выход которого соединен с первым входом триггера маркера, выход которого соединен с пятым входом блока формирования манчестерского кода и со вторым входом одиннадцатого элемента И, выход которого соединен со вторым входом триггера маркера, вход первого элемента НЕ является входом "0 таймера" ПРД и соединен с первым входом седьмого элемента И, выход которого соединен со вторым входом третьего элемента ИЛИ, выход которого соединен со вторым входом триггера конца передачи, первый выход которого соединен с первым входом восьмого элемента И, выход которого соединен со вторым входом триггера передачи, со вторым входом четвертого элемента ИЛИ и с первым входом триггера конца передачи, второй выход которого соединен с третьим входом первого элемента И, выход первого элемента НЕ соединен с первым входом третьего элемента И, вход второго элемента НЕ является входом "0 счетчика слов" ПРД и соединен со вторым входом четвертого элемента И и со вторым входом девятого элемента И, выход которого соединен с первым входом третьего элемента ИЛИ, выход второго элемента НЕ соединен со вторым входом третьего элемента И, выход десятого элемента И соединен с первым входом триггера передачи, второй выход которого соединен со вторым входом десятого элемента И, первый выход соединен с шестым входом блока формирования манчестерского кода и со вторым входом первого элемента И, первый выход счетчика байтов соединен со вторым входом блока элементов И-ИЛИ, второй выход счетчика байтов соединен с третьим входом блока элементов И-ИЛИ, третий выход счетчика байтов соединен с первым входом второго элемента И и с третьим входом пятого элемента И,

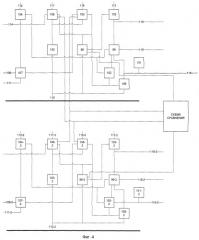

управляющий блок содержит генератор тактовых импульсов, шесть элементов И, счетчик слов, счетчик логического кольца, счетчик интервального времени, элемент задержки, вход кода длины сообщения УУ, вход "код интервала" УУ, вход "маркер" УУ, вход стробирования чтения УУ, выход "сообщение передано" УУ, выход "восстановить таймер" УУ, выход "0 счетчика слов" УУ, выход ТИ УУ, выход "запуск" УУ, выход "передать маркер" УУ, выход "0 таймера" УУ, причем первый вход счетчика слов является входом кода длины сообщения УУ, второй вход счетчика слов является входом стробирования чтения УУ, второй выход счетчика слов соединен с первым входом четвертого элемента И, первый выход счетчика слов соединен с первым входом пятого элемента И, с первым входом третьего элемента И и является выходом "0 счетчика слов" УУ, первый вход счетчика интервального времени является входом кода интервала УУ, первый выход счетчика интервального времени соединен с первым входом первого элемента И и со вторым входом третьего элемента И, выход которого является выходом "сообщение передано" УУ, вход шестого элемента И является входом "маркер" УУ и соединен со входом элемента задержки и со входом счетчика логического кольца, первый выход которого соединен с третьим входом пятого элемента И, с третьим входом четвертого элемента И, со вторым входом первого элемента И и со вторым входом шестого элемента И, выход которого соединен с третьим входом счетчика интервального времени, второй выход которого является выходом "0 таймера" УУ и соединен со вторым входом второго элемента И, выход которого является выходом "восстановить таймер" УУ, выход элемента задержки соединен со вторым входом четвертого элемента И и со вторым входом пятого элемента И, выход которого является выходом "передать маркер" УУ, выход четвертого элемента И является выходом "запуск" УУ, второй выход счетчика логического кольца соединен с первым входом второго элемента И, выход генератора тактовых импульсов является выходом ТИ УУ и соединен с третьим входом первого элемента И, выход которого соединен со вторым входом счетчика интервального времени, дополнительно введены третий блок буферной памяти (ББПЗ), третий информационный вход устройства, третий информационный выход устройства, второй вход кода адреса устройства, вход кода "маркер-2" устройства, вход кода "конец сообщения-2" устройства, второй вход кода длины сообщения устройства, вход "код интервала-2" устройства, выход "восстановить таймер-2" устройства, второй вход стробирования записи устройства, причем второй информационный вход ПРМ является вторым информационным входом устройства, вход кода "конец сообщения-2" ПРМ соединен со входом кода "конец сообщения" ПРД и является входом кода конца сообщения устройства, вход кода "маркер-2" ПРМ соединен с входом кода "маркер" ПРД и является входом кода маркера устройства, второй вход кода адреса ПРМ является вторым входом кода адреса устройства, второй информационный выход ПРМ соединен с информационным входом третьего блока буферной памяти (ББП3), второй выход стробирования записи ПРМ соединен со входом стробирования записи ББПЗ, второй выход "маркер-2" ПРМ соединен со входом "маркер-2" УУ, вход стробирования чтения ББП3 является вторым входом стробирования чтения устройства, вход начальной установки ББП3 является третьим входом начальной установки устройства, информационный выход ББП3 является информационным выходом устройства, второй вход кода длины сообщения УУ является вторым входом кода длины сообщения устройства, вход "код интервала-2" УУ является вторым входом кода интервала устройства, выход "сообщение передано-2" УУ является выходом устройства "сообщение передано-2", выход "восстановить таймер-2" УУ является выходом устройства "восстановить таймер-2", выход "0 счетчика слов-2" УУ соединен со входом "0 счетчика слов" ПРД, выход ТИ-2 УУ соединен со входом ТИ ПРД, выход "запуск-2" УУ соединен со входом "запуск" ПРД, выход "передать маркер-2" УУ соединен со входом "передать маркер-2" ПРД, выход "0 таймера-2" УУ соединен со входом "0 таймера" ПРД, второй информационный вход ПРД является третьим информационным выходом устройства,

блок приемника содержит второй блок приема сигналов, второй буферный регистр, второй выходной регистр, вторую схему выделения байта "маркер", вторую схему выделения байта "конец сообщения", вторую схему сравнения адресов, второй триггер разрешения сравнения адресов, второй триггер приема информации, второй счетчик байтов, четвертый, пятый и шестой элементы задержки, четвертый, пятый и шестой элементы И, второй и третий элементы ИЛИ, второй блок элементов И, второй информационный вход ПРМ, вход кода "конец сообщения-2" ПРМ, второй вход кода адреса ПРМ, второй информационный выход ПРМ, второй выход стробирования записи ПРМ, выход "маркер-2" ПРМ, причем второй вход блока приема сигналов является вторым информационным входом ПРМ, первый выход которого соединен со входом буферного регистра, выход которого соединен с первым входом схемы выделения байта "маркер-2", с первым входом схемы выделения байта "конец сообщения-2", с первым входом второй схемы сравнения адресов и с первым входом второго блока элементов И, выход которого соединен со входом второго выходного регистра, выход которого является вторым информационным выходом ПРМ, второй выход второго блока приема сигналов соединен со входом четвертого элемента задержки, выход которого соединен с третьим входом схемы выделения байта "конец сообщения-2", с третьим входом второй схемы сравнения адресов, с первым входом четвертого элемента И и с третьим входом схемы выделения байта "маркер-2", выход которого является выходом "маркер-2" ПРМ и соединен с первым входом четвертого элемента ИЛИ, выход которого соединен со вторым входом второго триггера разрешения сравнения адресов, выход которого соединен со вторым входом четвертого элемента И и с четвертым входом второй схемы сравнения адресов, выход которого соединен со вторым входом второго триггера приема информации, выход которого соединен с первым входом пятого элемента И, выход которого соединен со входом шестого элемента задержки, с третьим входом второго блока элементов И и со входом второго счетчика байтов, первый выход которого соединен со вторым входом второго блока элементов И, второй выход второго счетчика байтов соединен с первым входом шестого элемента И, выход которого является вторым выходом стробирования записи ПРМ, третий выход второго блока приема сигналов соединен с первым входом пятого элемента ИЛИ, выход которого соединен с первым входом второго триггера разрешения сравнения адресов, выход четвертого элемента И соединен со вторым входом пятого элемента ИЛИ, второй вход второй схемы выделения байта "маркер-2" является входом кода "маркер-2" ПРМ, второй вход второй схемы сравнения адресов является вторым входом кода адреса ПРМ, вход схемы выделения байта "конец сообщения-2" является входом кода "конец сообщения-2" ПРМ, первый выход схемы выделения байта "конец сообщения-2" соединен со вторым входом четвертого элемента ИЛИ и с первым входом второго триггера приема информации, второй выход схемы выделения байта "конец сообщения-2" соединен со входом пятого элемента задержки, выход которого соединен со вторым входом пятого элемента И, выход шестого элемента задержки соединен со вторым входом шестого элемента И, выход четвертого элемента И соединен со вторым входом пятого элемента ИЛИ,

блок передатчика содержит второй блок формирования манчестерского кода, двенадцатый элемент И, пятый элемент ИЛИ, седьмой элемент задержки, второй триггер маркера, вход «передать маркер-2», причем первый вход пятого элемента ИЛИ является входом «передать маркер-2», выход которого соединен со входом седьмого элемента задержки, выход которого соединен с первым входом второго триггера маркер, выход которого соединен с пятым входом второго блока формирования манчестерского кода и со вторым выходом двенадцатого элемента И, выход которого соединен со вторым входом второго триггера маркера,

управляющий блок содержит второй генератор тактовых импульсов, еще шесть элементов И, второй счетчик слов, второй счетчик логического кольца, второй счетчик интервального времени, второй элемент задержки, второй вход кода длины сообщения УУ, вход "код интервала-2" УУ, вход "маркер-2" УУ, второй вход стробирования чтения УУ, выход "сообщение передано-2" УУ, выход "восстановить таймер-2" УУ, выход "0 счетчика слов-2" УУ, выход ТИ-2 УУ, выход "запуск-2" УУ, выход "передать маркер-2" УУ, выход "0 таймера-2" УУ, причем первый вход второго счетчика слов является вторым входом кода длины сообщения УУ, второй вход счетчика слов является вторым входом стробирования чтения УУ, второй выход второго счетчика слов соединен с первым входом десятого элемента И, первый выход второго счетчика слов соединен с первым входом одиннадцатого элемента И, с первым входом девятого элемента И и является выходом "0 счетчика слов-2" УУ, первый вход второго счетчика интервального времени является вторым входом кода интервала УУ, первый выход второго счетчика интервального времени соединен с первым входом седьмого элемента И и со вторым входом девятого элемента И, выход которого является выходом "сообщение передано-2" УУ, вход двенадцатого элемента И является входом "маркер-2" УУ и соединен со входом второго элемента задержки и со входом второго счетчика логического кольца, первый выход которого соединен с третьим входом одиннадцатого элемента И, с третьим входом десятого элемента И, со вторым входом седьмого элемента И и со вторым входом двенадцатого элемента И, выход которого соединен с третьим входом второго счетчика интервального времени, второй выход которого является выходом "0 таймера-2" УУ и соединен со вторым входом восьмого элемента И, выход которого является выходом "восстановить таймер-2" УУ, выход второго элемента задержки соединен со вторым входом десятого элемента И со вторым входом одиннадцатого элемента И, выход которого является выходом "передать маркер-2" УУ, выход десятого элемента И является выходом "запуск-2" УУ, второй выход второго счетчика логического кольца соединен с первым входом восьмого элемента И, выход второго генератора тактовых импульсов является выходом ТИ-2 УУ и соединен с третьим входом седьмого элемента И, выход которого соединен со вторым входом второго счетчика интервального времени

Сравнительный анализ показал, что заявленное изобретение отличается наличием четырех дополнительных блоков, расположенных в такой последовательности, которая приводит к техническому результату.

Анализ патентной литературы показал, что до даты подачи отсутствовали устройства с указанной совокупностью существенных признаков, что говорит о новизне заявляемого технического решения.

Поиск технических решений в смежных областях техники не позволил выявить отличительные признаки заявляемого технического решения, что соответствует критерию "изобретательский уровень".

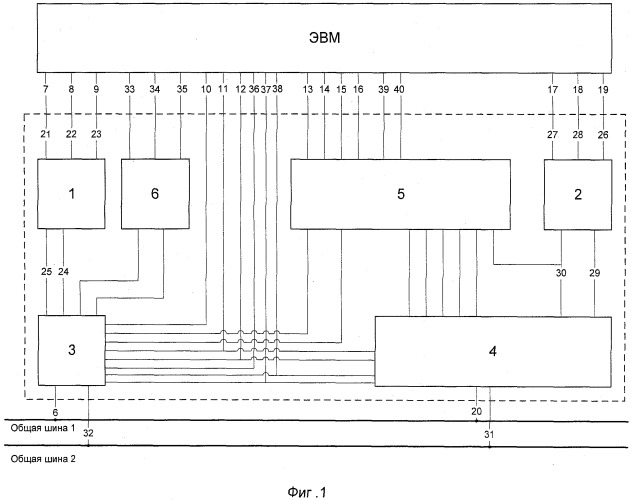

На фиг.1 представлена функциональная схема устройства для сопряжения источника и приемника информации, на фиг.2 - функциональная схема блока приемника, на фиг.3 - функциональная схема блока передатчика, на фиг.4 - функциональная схема управляющего блока.

Устройство для сопряжения источника и приемника информации (фиг.1) содержит первый блок буферной памяти (ББП1) 1, второй блок буферной памяти (ББП2) 2, третий блок буферной памяти (ББП3), блок приемника (ПРМ) 3, блок передатчика (ПРД) 4, управляющий блок (УУ) 5, первый информационный вход 6 устройства, третий информационный вход 32 устройства, первый информационный выход 7 устройства, третий информационный выход 31 устройства, четвертый информационный выход 33 устройства, вход стробирования чтения 8 устройства, вход стробирования чтения 34 устройства, первый вход начальной установки 9 устройства, третий вход начальной установки 35 устройства, вход кода адреса 10 устройства, вход кода адреса 37 устройства, вход кода маркера 11 устройства, вход кода маркера 36 устройства, вход кода конца сообщения 12 устройства, вход кода конца сообщения 38 устройства, вход кода длины сообщения 13 устройства, вход кода длины сообщения 39 устройства, вход кода интервала 14 устройства, вход кода интервала 40 устройства, выход "сообщение передано" 15 устройства, выход "восстановить таймер" 16 устройства, вход стробирования записи 17 устройства, второй вход начальной установки 18 устройства, второй информационный вход 19 устройства, второй информационный выход 20 устройства, причем информационный вход ПРМ является первым информационным входом 6 устройства, вход кода "конец сообщения" ПРМ соединен со входом кода "конец сообщения" ПРД и является входом кода конца сообщения 12 устройства, вход кода "конец сообщения-2" ПРМ соединен со входом кода "конец сообщения" ПРД и является входом кода конца сообщения 38 устройства, вход кода "маркер" ПРМ соединен с входом кода "маркер" ПРД и является входом кода маркера 11 устройства, вход кода "маркер-2" ПРМ соединен с входом кода "маркер" ПРД и является входом кода маркера 36 устройства, вход кода адреса ПРМ является входом кода адреса 10 устройства, вход кода адреса ПРМ является входом кода адреса 37 устройства, информационный выход ПРМ соединен с информационным входом 25 ББП1, второй информационный выход ПРМ соединен с информационным входом ББП3, выход стробирования записи ПРМ соединен со входом стробирования записи ББП1, второй выход стробирования записи ПРМ соединен со входом стробирования записи ББП3, выход "маркер" ПРМ соединен со входом "маркер" УУ, выход "маркер-2" ПРМ соединен со входом "маркер-2" УУ, вход стробирования чтения 22 ББП1 является входом стробирования чтения 8 устройства, вход стробирования чтения 22 ББП3 является входом стробирования чтения устройства, вход начальной установки 23 ББП1 является первым входом начальной установки 9 устройства, третий вход начальной установки ББП3 является третьим входом начальной установки 35 устройства, информационный выход 21 ББП1 является первым информационным выходом 7 устройства, информационный выход ББП3 является четвертым информационным выходом 33 устройства, вход кода длины сообщения УУ является входом кода длины сообщения 13 устройства, второй вход кода длины сообщения УУ является входом кода длины сообщения 39 устройства, вход "код интервала" УУ является входом кода интервала 14 устройства, вход "код интервала-2" УУ является входом кода интервала 40 устройства, выход "сообщение передано" УУ является выходом 15 устройства "сообщение передано", выход "восстановить таймер" УУ является выходом 16 устройства "восстановить таймер", выход "0 счетчика слов" УУ соединен со входом "0 счетчика слов" ПРД, выход "0 счетчика слов-2" УУ соединен со входом "0 счетчика слов" ПРД, выход ТИ УУ соединен со входом ТИ ПРД, выход ТИ-2 УУ соединен со входом ТИ ПРД, выход "запуск" УУ соединен со входом "запуск" ПРД, выход "запуск-2" УУ соединен со входом "запуск" ПРД, выход "передать маркер" УУ соединен со входом "передать маркер" ПРД, выход "передать маркер-2" УУ соединен со входом "передать маркер-2" ПРД, выход "0 таймера" УУ соединен со входом "0 таймера" ПРД, выход "0 таймера-2" УУ соединен со входом "0 таймера" ПРД, информационный вход 26 ББП2 является вторым информационным входом 19 устройства, вход стробирования записи 27 ББП2 является входом стробирования записи 17 устройства, вход начальной установки 28 ББП2 является вторым входом начальной установки 18 устройства, информационный выход 29 ББП2 соединен с информационным входом ПРД, выход стробирования чтения которого соединен со входом стробирования чтения 30 ББП2 и со входом стробирования чтения УУ, информационный выход ПРД является вторым информационным выходом 20 устройства, второй информационный выход ПРД является вторым информационным выходом 31 устройства, блок приемника содержит компаратор, блок приема сигналов 31, буферный регистр 32 и, выходной регистр 33, схему выделения байта "маркер" 34, схему выделения байта "конец сообщения" 35, схему сравнения адресов 36, триггер разрешения сравнения адресов 37, триггер приема информации 38, счетчик байтов 39, элементы задержки 40, 41, 42, элементы И 43, 44, 45, элементы ИЛИ 46, 47, блок элементов И 48, информационный вход 49 ПРМ, вход кода "конец сообщения" 50 ПРМ, вход кода адреса 52 ПРМ, вход кода маркера 51 ПРМ, информационный выход 53 ПРМ, выход стробирования записи 54 ПРМ, выход "маркер" 55 ПРМ, причем вход блока приема сигналов 31 является информационным входом 49 ПРМ, первый выход которого соединен с первым входом компаратора, первый выход которого соединен со входом буферного регистра 32, выход которого соединен с первым входом схемы выделения байта "маркер" 34, с первым входом схемы выделения байта "конец сообщения" 35, с первым входом схемы сравнения адресов 36 и с первым входом блока элементов И 48, выход которого соединен со входом выходного регистра 33, выход которого является информационным выходом 53 ПРМ, второй выход блока приема сигналов соединен со входом элемента задержки 40, выход которого соединен с третьим входом схемы выделения байта "конец сообщения" 35, с третьим входом схемы сравнения адресов 36, с первым входом элемента И 43 и с третьим входом схемы выделения байта "маркер" 34, выход которого является выходом "маркер" 55 ПРМ и соединен с первым входом элемента ИЛИ 46, выход которого соединен со вторым входом триггера разрешения сравнения адресов 37, выход которого соединен со вторым входом элемента И 43 и с четвертым входом схемы сравнения адресов 36, выход которого соединен со вторым входом триггера приема информации 38, выход которого соединен с первым входом элемента И 44, выход которого соединен со входом элемента задержки 42, с третьим входом блока элементов И 48 и со входом счетчика байтов 39, первый выход которого соединен со вторым входом блока элементов И 48, второй выход счетчика байтов 39 соединен с первым входом элемента И 45, выход которого является выходом стробирования записи 54 ПРМ, третий выход блока приема сигналов соединен с первым входом элемента ИЛИ 47, выход которого соединен с первым входом триггера разрешения сравнения адресов 37, выход элемента И 43 соединен со вторым входом элемента ИЛИ 47, второй вход схемы выделения байта "маркер" 34 является входом кода "маркер" 51 ПРМ, второй вход схемы сравнения адресов 36 является входом кода адреса 52 ПРМ, второй вход схемы выделения байта "конец сообщения" 35 является входом кода "конец сообщения" 50 ПРМ, первый выход схемы выделения байта "конец сообщения" 35 соединен со вторым входом элемента ИЛИ 46 и с первым входом триггера приема информации 38, второй выход схемы выделения байта "конец сообщения" 35 соединен со входом элемента задержки 41, выход которого соединен со вторым входом элемента И 44, выход элемента задержки 42 соединен со вторым входом элемента И 45, выход элемента И 43 соединен со вторым входом элемента ИЛИ 47, блок приема сигналов 31-2, буферный регистр 32-2 и, выходной регистр 33-2, схему выделения байта "маркер-2" 34-2, схему выделения байта "конец сообщения-2" 35-2, схему сравнения адресов 36-2, триггер разрешения сравнения адресов 37-2, триггер приема информации 38-2, счетчик байтов 39-2, элементы задержки 40-2, 41-2, 42-2, элементы И 43-2, 44-2, 45-2, элементы ИЛИ 46-2, 47-2, блок элементов И 48-2, информационный вход 49-2 ПРМ, вход кода "конец Сообщения-2" 50-2 ПРМ, вход кода адреса 52-2 ПРМ, вход кода маркера 51-2 ПРМ, информационный выход 53-2 ПРМ, выход стробирования записи 54-2 ПРМ, выход "маркер-2" 55-2 ПРМ, причем вход блока приема сигналов 31-2 является информационным входом 49-2 ПРМ, первый выход которого соединен со вторым входом компаратора, второй выход которого соединен со входом буферного регистра 32-2, выход которого соединен с первым входом схемы выделения байта "маркер-2" 34-2, с первым входом схемы выделения байта "конец сообщения-2" 35-2, с первым входом схемы сравнения адресов 36-2 и с первым входом блока элементов И 48-2, выход которого соединен со входом выходного регистра 33-2, выход которого является информационным выходом 53-2 ПРМ, второй выход блока приема сигналов соединен со входом элемента задержки 40-2, выход которого соединен с третьим входом схемы выделения байта "конец сообщения-2" 35-2, с третьим входом схемы сравнения адресов 36-2, с первым входом элемента И 43-2 и с третьим входом схемы выделения байта "маркер-2" 34-2, выход которого является выходом "маркер-2" 55-2 ПРМ и соединен с первым входом элемента ИЛИ 46-2, выход которого соединен со вторым входом триггера разрешения сравнения адресов 37-2, выход которого соединен со вторым входом элемента И 43-2 и с четвертым входом второй схемы сравнения адресов 36-2, выход которого соединен со вторым входом триггера приема информации 38-2, выход которого соединен с первым входом элемента И 44-2, выход которого соединен со входом элемента задержки 42-2, с третьим входом блока элементов И 48-2 и со входом счетчика байтов 39-2, первый выход которого соединен со вторым входом блока элементов И 48-2, второй выход счетчика байтов 39-2 соединен с первым входом элемента И 45-2, выход которого является выходом стробирования записи 54-2 ПРМ, третий выход блока приема сигналов соединен с первым входом элемента ИЛИ 47-2, выход которого соединен с первым входом триггера разрешения сравнения адресов 37-2, выход элемента И 43-2 соединен со вторым входом элемента ИЛИ 47-2, второй вход схемы выделения байта "маркер-2" 34-2 является входом кода "маркер-2" 51-2 ПРМ, второй вход схемы сравнения адресов 36-2 является входом кода адреса 52-2 ПРМ, второй вход схемы выделения байта "конец сообщения-2" 35-2 является входом кода "конец сообщения-2" 50-2 ПРМ, первый выход схемы выделения байта "конец сообщения-2" 35-2 соединен со вторым входом элемента ИЛИ 46-2 и с первым входом триггера приема информации 38-2, второй выход схемы выделения байта "конец сообщения-2" 35-2 соединен со входом элемента задержки 41-2, выход которого соединен со вторым входом элемента И 44-2, выход элеме