Способ передачи информации на основе хаотически формируемых ансамблей дискретных многоуровневых ортогональных сигналов

Иллюстрации

Показать всеИзобретение относится к области передачи информации и может быть использовано при передаче сообщений в широкополосных системах радиосвязи с кодовым разделением каналов. Технический результат заключается в повышении структурной скрытности системы передачи информации с кодовым разделением каналов за счет использования ансамблей ортогональных сигналов, хаотически формируемых на основе собственных векторов диагональной положительно определенной симметрической матрицы размерностью N. Указанный технический результат достигается тем, что для передачи сообщений, сменяемых от одного информационного символа к другому, применяют ортогональные кодовые комбинации, в качестве которых используют ансамбли дискретных ортогональных сигналов, формируемые путем расчета собственных чисел и собственных векторов диагональной положительно определенной симметрической матрицы, диагональными коэффициентами которой являются хаотически формируемые числовые последовательности. 3 ил.

Реферат

Область техники, к которой относится изобретение

Изобретение относится к области передачи информации и может быть использовано при передаче сообщений в широкополосных системах радиосвязи с кодовым разделением каналов.

Уровень техники

Известен способ многостанционного доступа с кодовым разделением каналов в системах передачи данных (см. Громаков Ю.А. Стандарты и системы подвижной радиосвязи. - М.: АОЗТ «Эко-трендз КО», 1996), суть которого заключается в расширении спектра частот на основе использования 64 видов последовательностей, сформированных по закону функций Уолша. Базовая станция может передавать информацию по 64 каналам одновременно. В каждом канале при передаче информации используется одна из 64 последовательностей Уолша. При изменении бита информационного сообщения фаза используемой последовательности Уолша изменяется на 180 градусов. Поскольку применяемые последовательности взаимно ортогональны, то взаимные помехи между каналами передачи базовой станции отсутствуют.

Информационные сигналы передаются на фоне специального синхронизирующего сигнала, структура которого формируется по закону случайных последовательностей максимальной длины. Синхронизирующий сигнал служит для введения передатчика базовой станции и приемника абонентской станции в цикловую фазу, а его манипуляция на этапе вхождения в связь обеспечивает передачу служебной информации.

Недостатком этого способа является то, что сигналы Уолша имеют регулярную структуру, которая заранее известна и поэтому широкополосная система радиосвязи с кодовым разделением каналов, построенная на основе этого способа, будет обладать низкой структурной скрытностью.

Известен генератор функций Попенко-Турко (см. патент СССР №1753464 А1, кл. G06F 1/02 от 07.08.1992), позволяющий генерировать дискретные ортогональные базисные функции, содержащий матрицу вычислителей, группу блоков деления, группы блоков элементов «И», матрицу операционных блоков, элементы задержки, блок синхронизации, регистр сдвига, блоки памяти и кольцевой регистр сдвига.

Недостатком этого генератора является отсутствие возможности генерирования хаотических ансамблей ортогональных сигналов (собственных векторов) различной структуры.

Наиболее близким по технической сущности к предлагаемому способу является способ, используемый в системе передачи данных с кодовым разделением каналов (см. патент Российской Федерации №2234191, кл. Н04В 7/216, H04L 9/26 от 24.07.2001), который включает операцию одновременной передачи сложных широкополосных сигналов на основе нелинейных последовательностей де Брейна со сменой формы последовательности в процессе передачи сообщения от одного информационного символа к другому.

Последовательности де Брейна так же как и словари Уолша обладают свойством ортогональности в точке, а большое разнообразие словарей де Брейна и наличие нелинейных операций в алгоритме формирования данного класса последовательностей позволяет использовать их в системах с многостанционным доступом для кодового уплотнения канала передачи.

Отличительным признаком этого способа является применение в каналах передачи сообщений, сменяемых от одного информационного символа к другому, ортогональных кодовых словарей де Брейна, каждое кодовое слово которых может быть построено путем суммирования по модулю два сигналов, снимаемых с разрядов регистра сдвига с нелинейными обратными связями по одному, по два и так далее до m включительно, где m - число разрядов регистра сдвига, функция обратных связей, которого задается соотношением:

,

где - разрешенный набор двоичных чисел, определяющий порядок подключения прямых и инверсных выходов элементов памяти регистра сдвига;

d - число разрешенных двоичных наборов, необходимых для генерирования максимального периода последовательности L, равного 2m;

Несмотря на то, что количество ортогональных сигналов, формируемых на основе кодовых словарей де Брейна, больше числа ортогональных сигналов Уолша размерности N, однако их количество является конечным для любой размерности N, что позволяет сделать вывод об их низкой структурной скрытности.

Целью изобретения является. разработка способа и устройства, позволяющего повысить структурную скрытность системы передачи информации с кодовым разделением каналов.

Раскрытие изобретения

Задачей предлагаемого изобретения является повышение уровня структурной скрытности широкополосных систем радиосвязи с кодовым разделением каналов.

Технический результат

Технический результат, который может быть достигнут с помощью предлагаемого изобретения, заключается в том, что для передачи сообщений, сменяемых от одного информационного символа к другому, предлагается использовать сформированные стохастическим образом ортогональные системы сигналов, описываемые собственными векторами диагональных положительно определенных симметрических матриц размерностью N. При этом используется свойство ортогональности собственных векторов, заключающееся в том, что собственные векторы, соответствующие различным собственным значениям нормального оператора, попарно ортогональны (см. Г.Корн, Т.Корн. Справочник по математике (для научных работников и инженеров). - М.: Издательство «Наука», 1974. - С.436).

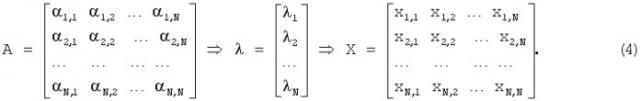

Известно, что всякий ненулевой вектор х называется собственным вектором матрицы λ, если найдется такое число λ, что будет выполняться равенство:

Это число λ называется собственным значением матрицы А, соответствующим собственному вектору х.

Если в пространстве выбран определенный базис, то уравнение (1) для собственных векторов и собственных значений линейного преобразования можно записать в матричной форме:

Всякий ненулевой столбец Х, для которого выполняется равенство (2), называется собственным вектором матрицы А, соответствующим собственному значению λ.

Собственный вектор матрицы А - это столбец вида (3), составленный из координат собственного вектора линейного преобразования в выбранном базисе.

Собственные векторы вещественной диагональной симметрической матрицы, отвечающие различным собственным значениям, ортогональны, т.е. их скалярное произведение равно нулю (см. Клиот-Дашинский М.И.Алгебра матриц и векторов. 3-е изд., стер., / - СПб.: Издательство «Лань», 2001. - 160 с. - (Учебники для вузов. Специальная литература)).

Из всего выше сказанного следует, что для любой вещественной диагональной симметрической матрицы А соотношение (4) существует набор собственных значений и каждому собственному значению соответствует собственный вектор X, который попарно ортогонален с любым из векторв ансамбля.

При этом расширение информационной последовательности происходит таким образом, что если информационный бит равен единице, то используется ортогональный сигнал инверсной структуры, а если информационный бит равен нулю, то используется ортогональный сигнал прямой структуры (см. Столингс В. Беспроводные линии связи и сети.: Пер. с англ. - М.: Издательский дом «Вильямс», 2003. - С.213).

Нелинейность формируемых структур сигналов достигается за счет того, что на каждом такте передачи информации расширяющая последовательность в виде одного из сигналов ортогональной системы сигналов, описываемых собственными векторами диагональных положительно определенных симметрических матриц, формируется путем стохастического задания набора диагональных коэффициентов, положительно определенной симметрической матрицы А (вида 4), генератором случайных положительных чисел.

Для достижения названного технического результата в передающую аппаратуру базовой станции наиболее близкого технического решения (см. патент Российской Федерации №2234191, кл. Н04В 7/216, H04L 9/26 от 24.07.2001), состоящую из N, равное 2m-1 каналов, каждый из которых содержит блок цифровой информации, подключенный к первому входу модулятора каждого из каналов, а вторые m входов подключены к выходу генератора де Брейна, причем выходы каждого канала подключены к объединителю блока формирования группового сигнала, выход которого подключен к первому входу модулятора, второй вход которого соединен с выходом генератора псевдослучайного сигнала синхронизации, а выход является выходом блока формирования группового сигнала, который через блок фазовой модуляции и усилитель мощности подключен к передающей антенне, причем первый вход генератора псевдослучайного сигнала синхронизации блока формирования группового сигнала одновременно соединен с первым выходом блока служебной информации, с первым входом генератора де Брейна и первым входом блока перестройки структуры сигнала, а второй вход генератора псевдослучайного сигнала синхронизации одновременно соединен с выходом генератора тактовых импульсов и четвертым входом блока перестройки структуры сигнала, при этом второй выход блока служебной информации одновременно подключен ко второму входу генератора де Брейна и второму входу блока перестройки структуры сигнала, а третий выход блока служебной информации параллельно подключен к входу блока цифровой информации и третьему входу блока перестройки структуры сигнала, первый выход которого подключен к третьему входу генератора де Брейна, второй к четвертому входу генератора де Брейна, третий к пятому входу генератора де Брейна, а четвертые d(m-1) входов подключены к шестым соответствующим входам генератора де Брейна, дополнительно введены блок формирования хаотических ансамблей ортогональных сигналов, содержащий матрицу вычислителей, блоки деления, блоки элемента «И» и блок синхронизации, причем с 1-го по N-й выходы блока генерации сигналов управления итерационным процессом, происходящим в блоке формирования хаотических ансамблей ортогональных сигналов, соединены со вторыми входами с 1-го по N-й вычислитель первой строки матрицы, второй вход вычислителя i-й (i=1, N-1, где N - порядок квадратной симметрической матрицы коэффициентов) строки матрицы соединен с вторым информационным входом соответствующего вычислителя -й строки матрицы, выход вычислителя i-го столбца матрицы соединен с информационным входом соответствующего вычислителя -го столбца матрицы, третьи информационные входы вычислителей первого столбца матрицы соединены с входом логического нуля блока формирования хаотических ансамблей ортогональных сигналов, регистр сдвига, первый и второй блоки памяти, матрицу операционных блоков, кольцевой регистр сдвига, причем выход вычислителя -й строки -го столбца матрицы соединен с первыми входами делителя блоков деления, вход делимого j-го блока деления соединен с вторым входом вычислителя j-й строки (N-i+1)-го столбца матрицы, выход j-го блока деления соединен с первым входом j-го блока элементов «И», вторые входы блоков элементов «И» соединены с выходом i-го разряда регистра сдвига, выходы блока синхронизации соединены соответственно с тактовыми входами операционных блоков матрицы, с тактовым входом элемента задержки, с входом разрешения сдвига регистра сдвига, с входами разрешения записи первого блока памяти, с входами разрешения записи второго блока памяти, с тактовыми входами первого и второго блоков памяти, с входами разрешения считывания первого и второго блоков памяти и входом разрешения сдвига кольцевого регистра сдвига, вторые выходы вычислителей последней строки матрицы соединены с 1-го по N-й информационный вход второго блока памяти, первый информационный вход операционного блока i-й строки первого столбца матрицы соединен с i-м выходом второго блока памяти, первые выходы операционных блоков i-й строки S-x(S=i, N-1) столбцов матрицы соединены с (N-i+1)-м информационным входом второго блока памяти, первый информационный вход операционного блока k-й (k=1, N-2) строки М-го (М=2, N-1) столбца матрицы соединен с первым выходом операционного блока (k+1)-й строки (M-1)-го столбца матрицы, первый информационный вход операционного блока (Р-2)-й строки М-го столбца матрицы подключен к выходу элемента задержки, информационный вход которого подключен к второму выходу операционного блока -й строки -го столбца матрицы, второй информационный вход операционного блока М-й строки i-го столбца матрицы подключен к второму выходу операционного блока (М-1)-й строки i-го столбца матрицы, входы значения компонент исходной матрицы блока формирования хаотических ансамблей ортогональных сигналов соединены с информационными входами первого блока памяти, выходы которого соединены с третьими информационными входами вычислителей соответствующих строк матрицы, k-й выход второго блока памяти соединен с k-м дополнительным информационным входом первого блока памяти, выходы разрядов кольцевого регистра сдвига соединены с соответствующими входами разрешения считывания второго блока памяти, выходы которого являются выходами блока формирования ансамблей хаотических ортогональных сигналов, генератор случайных положительных чисел (ГСПЧ), вход которого соединен с выходом блока синхронизации, а информационные с 1-го по N-й выходы ГСПЧ являются информационными с 1-го по N-й входами второго запоминающего устройства, элемент «И», а также запоминающие устройства каждого из каналов, на первый вход которых подается информационная последовательность, а на второй управляющий сигнал с элемента «И». Причем в каждом канале передающей аппаратуры исключен блок перестройки структуры сигнала, генератор де Брейна, блок служебной информации и соответствующие связи этих устройств; приемную аппаратуру абонентской станции, содержащую блок высокочастотной селекции, вход которого соединен с приемной антенной, а выход одновременно подключен к первому входу блока обнаружения сигнала синхронизации и первому входу блока корреляционной обработки, выход которого через блок выделения информации подключен к блоку получения информации, причем первый выход блока обнаружения сигнала синхронизации через блок поиска и первый вход генератора копии сигнала синхронизации подключен ко второму входу блока обнаружения сигнала синхронизации, выход которого подключен ко входу блока выделения служебной информации, первый выход блока выделения служебной информации одновременно подключен к первым входам блока перестройки структуры сигнала и генератору копии сигнала де Брейна, второй выход блока выделения служебной информации параллельно подключен ко вторым входам генератора копии сигнала де Брейна и блока перестройки структуры сигнала, а третий выход к третьему входу блока перестройки структуры сигнала, четвертый вход которого одновременно соединен с выходом генератора тактовых импульсов, со вторым входом генератора копии сигнала синхронизации и вторым входом блока выделения информации, при этом первый, второй и третий выходы блока перестройки структуры сигнала подключены соответственно к третьему, четвертому и пятому входам генератора копии сигнала де Брейна, а четвертые d(m-1) выходы к шестым входам генератора копии сигнала де Брейна, выход которого подключен ко второму входу блока корреляционной обработки, дополнительно введены блок формирования хаотических ансамблей ортогональных сигналов, содержащий матрицу вычислителей, блоки деления, блоки элементов «И» и блок синхронизации, причем с 1-го по N-й выходы блока генерации копий сигналов управления итерационным процессом, происходящим в блоке формирования копий хаотических ансамблей ортогональных сигналов, соединены со вторыми входами с 1-го по N-й вычислитель первой строки матрицы, второй вход вычислителя i-й строки матрицы соединен с вторым информационным входом вычислителя (i+1)-й строки матрицы, выход вычислителя г-го столбца матрицы соединен с вторым информационным входом вычислителя (i+1)-го столбца матрицы, третьи информационные входы вычислителей первого столбца матрицы соединены с входом логического нуля блока формирования копий ансамблей хаотических ортогональных сигналов, регистр сдвига, первый и второй блоки памяти, матрицу операционных блоков, элемент задержки и кольцевой регистр сдвига, причем выход вычислителя (i+1)-й строки (i+1)-го столбца матрицы соединен с первыми входами делителя блоков деления, вход делимого j-го блока деления (j=1, N-1) соединен с вторым входом вычислителя j-й строки (N-i+1)-го столбца матрицы, выход j-го блока деления соединен с первым входом j-го блока элементов «И», вторые входы блоков элементов «И» соединены с выходом i-го разряда регистра сдвига, выходы блока синхронизации соединены соответственно с тактовыми входами операционных блоков матрицы, с тактовым входом элемента задержки, с входом разрешения сдвига регистра сдвига, с входами разрешения записи первого блока памяти, с входами разрешения записи второго блока памяти, с тактовыми входами первого и второго блоков памяти, с входами разрешения считывания первого и второго блоков памяти и входом разрешения сдвига кольцевого регистра сдвига, выходы j-x блоков элементов «И» с первой по (N-1) соединены с первым информационным входом вычислителя (j+1)-й строки j-го столбца матрицы, вторые выходы вычислителей последней строки матрицы соединены с информационными входами второго блока памяти, первый информационный вход операционного блока i-й строки первого столбца матрицы соединен с i-м выходом второго блока памяти, первые выходы операционных блоков i-й строки S-x(S=i, N-1) столбцов матрицы соединены с (N-i+1)-м информационным входом группы второго блока памяти, первый информационный вход операционного блока k-й (k=1, N-2) строки М-го (М=2, N-1) столбца матрицы соединен с первым выходом операционного блока (k+1)-й строки (М-1)-го столбца матрицы, первый информационный вход операционного блока (N-2)-й строки М-го столбца матрицы подключен к выходу элемента задержки, информационный вход которого подключен к второму выходу операционного блока (N-1)-й строки (M-1)-го столбца матрицы, второй информационный вход операционного блока М-й строки i-го столбца матрицы подключен к второму выходу операционного блока (М-1)-й строки i-го столбца матрицы, входы значения компонент исходной матрицы блока формирования копий хаотических ансамблей ортогональных сигналов соединены с информационными с 1-го по N-й входами первого блока памяти, выходы которого соединены с первыми информационными входами с 1-го по N-й вычислитель соответствующей строки матрицы, выходы с 1-го по N-й разрядов кольцевого регистра сдвига соединены с 1-го по N-й входами разрешения считывания второго блока памяти, генератор случайных положительных чисел (ГСПЧ), управляющий вход которого соединен с выходом блока синхронизации, а информационные с 1-го по N-й выходы являются информационными с 1-го по N-й входами запоминающего устройства, элемент «И», а также запоминающее устройство каждого из каналов, на первый вход которого подается управляющий сигнал, а на второй - копии ансамблей ортогональных сигналов. Причем в каждом канале приемной аппаратуры исключен блок перестройки структуры сигнала, блок выделения служебной информации, генератор копии сигнала де Брейна и соответствующие связи этих устройств.

Краткое описание чертежей

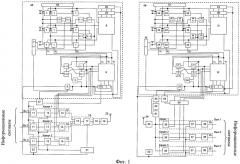

На фиг.1 показана структурная схема приемопередающей аппаратуры устройства передачи информации на основе хаотически формируемых ансамблей дискретных многоуровневых ортогональных сигналов.

На фиг.2 показаны временные диаграммы принципа функционирования устройства передачи информации на основе хаотически формируемых ансамблей дискретных многоуровневых ортогональных сигналов, где: а) сигналы тактового генератора, б) сигнал, поступающий в первый канал связи Sинф.1(t), в) сигнал, поступающий во второй канал связи Sинф.2(t), г) сигнал, поступающий в третий канал связи Sинф.3(t), д) ортогональный хаотический сигнал, поступающий в первый канал связи S1(t), е) ортогональный хаотический сигнал, поступающий во второй канал связи S2(t), ё) ортогональный хаотический сигнал, поступающий в третий канал связи S3(t), ж) промодулированный информационный сигнал на выходе первого канала, з) промодулированный информационный сигнал на выходе второго канала, и) промодулированный информационный сигнал на выходе третьего канала.

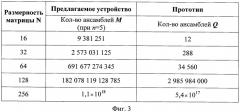

На фиг.3 представлен сравнительный анализ количества ансамблей ортогональных сигналов, формируемых устройством передачи информации на основе хаотически формируемых ансамблей дискретных многоуровневых ортогональных сигналов и прототипом.

Осуществление изобретения

Предлагаемый способ осуществляется в следующей последовательности: сначала с помощью вспомогательного синхронизирующего сложного сигнала передающая аппаратура базовой станции и приемная аппаратура каждой из 2m-1 абонентских станций вводится в цикловую фазу. Затем, посредством манипуляции вспомогательного сигнала синхронизации на каждый канал передается служебная информация (единый начальный блок для всех абонентских станций). После выполнения указанной процедуры начинается одновременная передача всем абонентам цифровой информации, при этом каждому биту информации фиксированного канала ставится в соответствие сложный сигнал, структура которого зависит от значений коэффициентов диагональной положительно определенной симметрической матрицы, которые формируются генератором случайных положительных чисел, причем расширение информационной последовательности происходит в случае, если информационный бит равен единице за счет использования ортогонального сигнала инверсной структуры, в случае если информационный бит равен нулю за счет использования ортогонального сигнала прямой структуры (см. Столингс В. Беспроводные линии связи и сети.: Пер. с англ. - М.: Издательский дом «Вильямс», 2003. - С.213).

После передачи очередного информационного бита на передающей и приемной стороне производится синхронная смена коэффициентов диагональной положительно определенной симметрической матрицы, поступающих от идентичных ГСПЧ в приемной и передающей стороне, на основе которых происходит расчет сформированных стохастическим образом ортогональных систем сигналов, описываемых собственными векторами диагональных положительно определенных симметрических матриц. При этом сигнал, используемый на приемной стороне для корреляционной обработки, будет иметь структуру, совпадающую с сигналом, излучаемым передатчиком, и, следовательно, может быть использован для обработки информационного потока, адресованного получателю цифровой информации.

Устройство содержит в передающей аппаратуре (фиг.1) N=2m-1 каналов 12, каждый из которых состоит из запоминающего устройства 11, второй вход которого связан с первым выходом блока элемента «И» 47, второй выход которого подключен к управляющему входу блока синхронизации 6, причем вход блока элемента «И» 47 связан с управляющим выходом старшего разряда кольцевого регистра сдвига 10, вход которого связан с блоком синхронизации 6, выход которого подключен к входу регистра сдвига 7, выходы которого, в свою очередь, связаны с вторыми входами блоков элемента «И» 3, а выходы блока памяти 8 являются первыми входами вычислителей 1, причем на второй вход N-го (N - размерность матрицы коэффициентов) вычислителя подается сигнал с N-го выхода блока генерации сигналов управления итерационным процессом 50, а третьи входы вычислителей 1 первого столбца матрицы соединены с входом логического нуля блока формирования хаотических ансамблей ортогональных сигналов, с выходов вычислителей 1 сигналы поступают на первый и второй входы блоков деления 2 и через первые входы блоков элемента «И» 3 поступают на вторые входы первого и второго столбцов матрицы вычислителей 1, вторые выходы вычислителей 1.3.1, 1.3.2, 1.3.3 подключены к информационным с 1-го по N-й вход блока памяти 9, информационные с 1-го по (N-1)-й выходы которого связаны с первыми входами операционных блоков 4 первого столбца, причем выход операционного блока 4 первого столбца и первой строки подключен к N-му входу блока памяти 9, а выходы операционных блоков 4 первого столбца i-й (i=2, N-1) строки подключены к первым входам операционных блоков 4 j-го (j=2, N-1) столбца i-й (i=1, N-1) строки, при этом операционные блоки каждого из столбцов соединены между собой, вторые входы операционных блоков 4 связаны с выходом блока синхронизации 6, причем второй выход операционного блока 4 (N-1)-й строки первого столбца связан со вторым входом элемента задержки 5, первый вход которого связан с выходом блока синхронизации 6, а выход подключен к первому операционному блоку 4 (N-1)-й строки (N-1)-го столбца, при этом информационные выходы операционных блоков 4 j-го (j=N-l) столбца i-й (i=1, N-1) строки подключены к информационным с 2-го по N-й входам блока памяти 9, при этом синхроимпульсы с блока синхронизации 6 одновременно поступают на вход кольцевого регистра сдвига 10, управляющие входы блоков памяти 8 и 9, управляющий вход генератора случайных положительных чисел 22 и запоминающее устройство 23, информационные входы которого с 1-го по N-й подключены к информационным с 1-го по N-й выходам генератора случайных положительных чисел 22, а информационные с 1-го по N-й выходы подключены к информационным входам блока памяти 8, первый управляющий выход кольцевого регистра сдвига 10 подключен к входу блока элемента «И» 47, а вторые с 1-го по N-й выходы связаны с 1-го по N-й управляющий вход блока памяти 9, причем выход запоминающего устройства 11 подключен к первому входу блока цифровой информации 13, второй вход которого связан с вторым выходом генератора сигналов синхронизации 21, выход блока цифровой информации 13 подключен к первому входу модулятора 14 каждого из каналов передачи 12, а второй вход модулятора 14 связан с информационными выходами блока памяти 9, выход каждого N-го модулятора 14 является выходом каждого N-го канала 12, который через объединитель входов 15 блока формирования группового сигнала 16 подключен к первому входу модулятора 17 блока формирования группового сигнала 16, второй вход которого соединен с первым выходом генератора сигналов синхронизации 21, а выход является выходом блока формирования группового сигнала 16, который через блок фазовой модуляции 18 и усилитель мощности 19 подключен к передающей антенне 20, причем вход генератора сигналов синхронизации 21 подключен к выходу генератора тактовых импульсов 52, который параллельно подключен к тактовому входу блока синхронизации 6; приемную аппаратуру (фиг.1), содержащую блок высокочастотной селекции 40, вход которого соединен с приемной антенной 39, а выход подключен к первому входу блока обнаружения сигнала синхронизации 41 и вторым входам блока корреляционной обработки 36 каждого из 2m-1 каналов 35, причем выход блока корреляционной обработки 36 подключен к первому входу блока выделения информации 37, второй вход которого связан с выходом генератора тактовых импульсов 53, причем выход блока обнаружения сигнала синхронизации 41 через блок поиска 42 соединен с входом генератора копий сигналов синхронизации 43, первый выход которого подключен к второму входу блока обнаружения сигнала синхронизации 41, второй - к управляющему входу блока синхронизации 29, выход которого связан с управляющим входом регистра сдвига 30, выходы которого являются вторыми входами соответствующих блоков элементов «И» 26, а третий выход генератора копий сигналов синхронизации 43 соединен с первым управляющим входом блока элемента «И» 44, выход которого подключен к управляющему входу запоминающего устройства 34, информационные с 1-го по N-й входы которого подключены к информационным с 1-го по N-й выходам блока памяти 32, причем выход блока синхронизации 29 подключен к управляющему входу блока памяти 31, информационные с 1-го по N-й выходы которого являются первыми входами вычислителей 24, причем на второй вход каждого N-го (N - размерность матрицы коэффициентов) вычислителя 24 подается сигнал с N-го выхода блока генерации сигналов управления итерационным процессом 51, который полностью идентичен сигналу, вырабатываемому блоком генерации сигналов управления итерационным процессом 50 на передающей стороне, а третьи входы вычислителей 24 первого столбца матрицы соединены с входом логического нуля блока формирования копий хаотических ансамблей ортогональных сигналов, причем с выходов вычислителей 24 сигналы поступают на первый и второй входы блоков деления 25 и через первые входы блоков элемента «И» 26 поступают на вторые входы первого и второго столбцов матрицы вычислителей 24, вторые выходы вычислителей 24.3.1, 24.3.2, 24.3.3 подключены к информационным с 1-го по N-й вход блока памяти 32, информационные с 1-го по (N-1)-й выходы которого связаны с первыми входами операционных блоков 27 первого столбца, причем выход операционного блока 27 первого столбца и первой строки подключен к N-му входу блока памяти 32, а выходы операционных блоков 27 первого столбца j-й (i=2, N-1) строки подключены к первым входам операционных блоков 27 j-го (j=2, N-1) столбца i-й (i=1, N-1) строки, при этом операционные блоки каждого из столбцов соединены между собой, вторые входы операционных блоков 27 связаны с выходом блока синхронизации 29, причем второй выход операционного блока 27 (N-1)-й строки первого столбца связан со вторым входом элемента задержки 28, первый вход которого связан с выходом блока синхронизации 29, а выход подключен к первому операционному блоку 27 (N-1)-й строки (N-1)-го столбца, при этом информационные выходы операционных блоков 27 j-го (j=N-1) столбца i-й (i=1, N-1) строки подключены к информационным с 2-го по N-й входам блока памяти 32, при этом синхроимпульсы с блока синхронизации 29 одновременно поступают на вход кольцевого регистра сдвига 33, на управляющий вход блока памяти 31 и 32, управляющий вход генератора случайных положительных чисел 45 и запоминающее устройство 46, информационные входы которого с 1-го по N-й подключены к информационным с 1-го по N-й выходам генератора случайных положительных чисел 45, а информационные выходы с 1-го по N-й подключены к информационным с 1-го по N-й входам блока памяти 31, при этом управляющий выход кольцевого регистра сдвига 33 подключен к второму входу блока элемента «И» 44, выход которого связан с управляющим входом запоминающего устройства 34, N-й выход которого подключен к второму входу N-го блока корреляционной обработки 36 каждого из каналов 35, вторые управляющие выходы кольцевого регистра 33 с 1-го по N-й связаны с 1-го по N-й управляющий вход блока памяти 32, причем выход каждого из блоков корреляционной обработки 36 подключен к первому входу блока выделения информации 37, второй вход которого подключен к выходу генератора тактовых импульсов 53, который параллельно подключен к тактовому входу блока синхронизации 29 и тактовому входу генератора копий сигналов синхронизации 43, при этом выход блока выделения информации 37 связан с входом блока приема информации 38.

Устройство работает следующим образом. Информационные сигналы поступают в запоминающее устройство 11 каждого из каналов передачи 12 и хранятся в нем до момента получения управляющего сигнала с блока элемента «И» 47, свидетельствующего о завершении этапа формирования стохастическим образом ортогональной системы сигналов, описываемых собственными векторами диагональных положительно определенных симметрических матриц размерностью N в блоке формирования хаотических ансамблей ортогональных сигналов 48. Затем информационный бит каждого из каналов 12 через блок цифровой информации 13 подается в модулятор 14, где он модулируется расширяющей последовательностью, поступающей с блока памяти 9 блока формирования хаотических ансамблей ортогональных сигналов 48. Сигналы, снимаемые с выхода модулятора 14 каждого канала, одновременно подаются в сумматор 15 блока формирования группового сигнала 16, где после их объединения и наложения в модуляторе 17 сигнала синхронизации, поступающего с выхода генератора сигналов синхронизации 21, происходит формирование группового сигнала, спектр которого после переноса в область несущей частоты в блоке фазовой модуляции 18 и усилителе мощности 19 через антенну 20 излучается в эфир. На приемной стороне поступающий сигнал принимается антенной 39 и подвергается предварительной обработке в блоке высокочастотной селекции 40. С выхода этого блока сигнал одновременно подается в блок обнаружения сигнала синхронизации 41 и блоки корреляционной обработки 36 каждого канала 35. При этом блок обнаружения сигнала синхронизации 41 совместно с блоком поиска 42 вводят в синхронизм генератор копии сигналов синхронизации 43. После чего с генератора копий сигналов синхронизации 43 подается управляющий сигнал на блок синхронизации 29 блока формирования копий ансамблей хаотических ортогональных сигналов 49, свидетельствующий о начале формирования копий хаотических ансамблей ортогональных сигналов блоком формирования копий хаотических ансамблей ортогональных сигналов 49. Подача управляющего сигнала на блок элемента «И» 44 с кольцевого регистра сдвига 33 блока формирования копий хаотических ансамблей ортогональных сигналов 49 говорит о завершении этапа формирования ортогональных кодовых последовательностей и записи их в запоминающее устройство 34. После чего под воздействием управляющего сигнала с блока элемента «И» 44 копии хаотических ансамблей ортогональных сигналов подаются с запоминающего устройства 34 на блоки корреляционной обработки 36 каждого из каналов связи 35 и, пройдя через первый вход блока выделения информации 37, на второй вход которого подается копия сигнала синхронизации с генератора копий сигналов синхронизации 43, направляются на вход блока приема информации 38.

При этом на передающей стороне блок формирования хаотических ансамблей ортогональных сигналов 48 функционирует следующим образом: при отсутствии на входе элемента «И» 47 информационного сигнала с кольцевого регистра сдвига 10, активируется работа блока синхронизации 6 блока формирования хаотических ансамблей ортогональных сигналов 48, с выхода которого подается управляющий сигнал на управляющий вход генератора случайных положительных чисел 22 и запоминающее устройство 23, в результате чего происходит генерация и запись случайных коэффициентов матрицы А в блок памяти 8, после этого начинается вычисление 1-го собственного значения и соответствующего ему собственного вектора, которое осуществляется в течение времени нахождения «1» в 1-м разряде регистра сдвига 7, поэтому период поступления тактовых импульсов на тактовый вход регистра сдвига 7 равен времени сходимости итерационного процесса и вычисления оставшейся части компонент собственного вектора.

В течение первого периода работы «1» с выхода первого разряда регистра сдвига 7 поступает на вторые входы блоков элементов «И» 3.1.1 и 3.1.2. На второй вход блока элемента «И» 3.2.1 поступает «0» с выхода второго разряда первого регистра сдвига 7, в результате на выходе блока 3.2.1 формируется «0».

С поступлением последовательности синхроимпульсов с блока синхронизации 6 коэффициенты, находящиеся в первом блоке памяти 8, последовательно поступают на первые входы вычислителей 1 и запоминаются в них. Вычислители так же выполняют функцию накопления каждый раз в случае подачи на их вход нового слагаемого.

На вторые входы вычислителей 1, кроме последнего, подаются произвольные сигналы с блока генерации сигналов управления итерационным процессом 50.

На вторых входах вычислителе