Выходной усилитель

Иллюстрации

Показать всеРеферат

ОП ИСАН И Е

ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

Союз Советских

Соцнелистнческнх

Республик

Зависимое от авт. свидетельства ¹â€”

Кл. 21ат, 36/04

Заявлено 05.III.1968 (№ 1225677/! 8-24) с присоединением заявки ¹â€”

МПК Н 03k

УДК 681.325.65:621.375, .018,756 (088.8) Приоритет

Опубликовано 05Х.1969, Бюллетень )¹ 16

Дата опубликования описания 17.IX.1969

Комитет по двлзи изобретений и открытий при Совете Министров

СССР

В. Кузнецов

Заявитель

ВЫХОДНОЙ УСИЛИТЕЛЬ

Выходной усилитель относится к элементам вычислительной техники и предназначен для работы в логических схемах цифровых вычислительных машин.

Известны выходные усилители, содержащие входную логическую схему, входной транзистор, выходной инвертирующий транзистор, выходной эмиттерный повторитель и дополнительный транзистор. Недостатком этих усилителей является наличие большого тока, проходящего через выходные транзисторы во время переходного процесса.

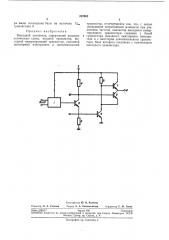

Предложенный выходной усилитель отличается тем, что, с целью уменьшения потребляемой мощности при увеличении часготы, в нем коллектор выходного инвертирующего транзистора соединен с базой транзистора выходного эмиттерного повторителя и с эмиттером дополнительного транзистора, база которого соединена с коллектором выходного транзистора.

Это позволяет исключить прохождение тока через выходной инвертор и выходной эмиттерный повторитель одновременно во время переходного процесса и уменьшить мощность, потребляемую усилителем от источника при высоких частотах работы, Схема предложенного выходного усилителя приведена на чертеже.

Он содержит входную логическую схему 1, которая подключается к базе входного транзистора 2, эмиттер и коллектор которого подключены к резистору 8 и резистору 4 соответственно. К эмиттеру транзистора 2 подключена база выходного инвертирующего транзистора 5, к коллектору которого подключены резистор б, база транзистора 7 выходного эмиттерного повторителя и эмиттер дополнительного транзистора 8. База транзистора 8 подключена к коллектору транзистора 2, а коллектор транзистора 8 соединен с выходом 9 схемы.

Схема работает следующим образом.

При подаче на вход схемы высокого уровня напряжения транзисторы 2, 5 и 8 открыты. На базе транзистора 8 напряжение U,<+U„, на эмиттере напряжение U,, Через транзисторы

5 и 8 протекает ток нагрузки. Транзистор 7 закрыт напряжением U„, так как на базе

20 у него напряжение U,, a на эмиттере — 2U

При подаче на вход схемы низкого уровня. напряжения транзистор 2 закрывается, закрывая транзисторы 5 и 8. Транзистор 7 открывается током через резистор б.

В этой схеме протекание тока одновременно через транзисторы 5 и 7 во время переходного процесса исключено. Этому препятствует включение дополнительного транзистора 8.

При протекании тока через транзистор 8

30 транзистор 7 закрыт — потенциал его эмитте242962

Составитель Ю, Н. Колотов

Техред А. А. Камышникова Корректор С. М. Сигал

Редактор Л. А. Утехина

Заказ 2294)17 Тираж 480 Подписное

ЦНИИПИ Комитета по делам изобретений и открытий при Совете Министров СССР

Москва, Центр, пр. Серова, д. 4

Типография, пр. Сапунова, 2 ра выше потенциала базы на величину U транзистора 8.

Предмет изобретения

Выходной усилитель, содержащий входную логическую схему, входной транзистор, выходной инвертирующий транзистор, выходной эмиттерный повторитель и дополнительный транзистор, отличающийся тем, что, с целью уменьшения потребляемой мощности при увеличении частоты, коллектор выходного инвертирующего транзистора соединен с базой транзистора выходного эмиттерного повторителя и с эмиттером дополнительного транзистора, база которого соединена с коллектором выходного транзистора.