Устройство для распознавания образов

Иллюстрации

Показать всеИзобретение относится к автоматике и вычислительной технике и может быть использовано в системах автоматического распознавания образов для распознавания состояний объектов по значениям их параметров. Техническим результатом является повышение производительности и уровня универсальности устройства за счет автоматизации процесса обучения устройства и распознавания образов при произвольном законе распределения информативных признаков. Устройство для распознавания образов дополнительно содержит таймер, счетчик классов образов, счетчик адресов младших разрядов, дешифратор кода класса образа, буферный регистр, блок памяти распределений информативных признаков, блок сравнения, счетчик значений информативных признаков, элемент задержки и логический элемент И. 7 ил.

Реферат

Изобретение относится к автоматике и вычислительной технике и предназначено для использования в системах автоматического распознавания образов, в частности для распознавания состояний сложных объектов по ряду значений их параметров.

Известно устройство для распознавания образов (патент РФ на изобретение №2306605, опубл. 20.09.2007, БИ №26), используемое для идентификации состояний объектов по значениям их параметров, которое по своей технической сущности является наиболее близким к предлагаемому устройству. Это устройство содержит многоканальный коммутатор, информационные входы которого подключены к информационным входам устройства, аналого-цифровой преобразователь, информационный вход которого подключен к выходу многоканального коммутатора, счетчик адресов, блок памяти, у которого адресные входы младших разрядов подключены к выходу аналого-цифрового преобразователя, а адресные входы старших разрядов блока памяти подключены к выходам счетчика адресов и к адресным входам многоканального коммутатора, блок логических элементов И, в котором первые и вторые входы логических элементов И подключены к соответствующим первым и вторым входам блока логических элементов И, выходы логических элементов И являются выходами блока логических элементов И, блок сдвиговых регистров, в котором информационные входы первых разрядов сдвиговых регистров подключены к соответствующим информационным входам блока сдвиговых регистров, сдвиговые входы сдвиговых регистров подключены к соответствующим сдвиговым входам блока сдвиговых регистров, а выходы последних разрядов сдвиговых регистров подключены к выходам блока сдвиговых регистров, блок управления, первый, второй, третий и четвертый выходы которого подключены соответственно к управляющим входам счетчика адресов, блока памяти, ко второму входу блока логических элементов И и к управляющему входу аналого-цифрового преобразователя, а вход блока управления является управляющим входом устройства, выходы блока памяти подключены непосредственно к соответствующим информационным входам блока сдвиговых регистров и к соответствующим первым входам блока логических элементов И, выходы которого подключены к соответствующим сдвиговым входам блока сдвиговых регистров, выходы которого являются выходами устройства.

Недостатком устройства-прототипа является низкая производительность на этапе обучения устройства, обусловленная неавтоматическим расчетом данных и "ручным" вводом их в блок памяти, а также узкая специализация устройства, обусловленная возможностью распознавания образов только при равномерном законе распределения информативных признаков.

Техническим результатом настоящего изобретения является повышение производительности и уровня универсальности устройства.

Для достижения результата в устройство для распознавания образов, содержащее многоканальный коммутатор, информационные входы которого подключены к информационным входам признаков устройства, аналого-цифровой преобразователь, информационный вход которого подключен к выходу многоканального коммутатора, счетчик адресов старших разрядов, блок памяти коэффициентов ассоциативности признаков, у которого адресные входы младших разрядов подключены к выходу аналого-цифрового преобразователя, а адресные входы старших разрядов блока памяти коэффициентов ассоциативности признаков подключены к выходам счетчика адресов старших разрядов и к адресным входам многоканального коммутатора, блок логических элементов И, в котором первые и вторые входы логических элементов И подключены к соответствующим первым и вторым входам блока логических элементов И, выходы логических элементов И являются выходами блока логических элементов И, блок сдвиговых регистров, в котором информационные входы первых разрядов сдвиговых регистров подключены к соответствующим информационным входам блока сдвиговых регистров, сдвиговые входы сдвиговых регистров подключены к соответствующим сдвиговым входам блока сдвиговых регистров, а выходы последних разрядов сдвиговых регистров подключены к выходам блока сдвиговых регистров, блок управления, первый, второй, третий и четвертый выходы которого подключены соответственно к счетному входу счетчика адресов старших разрядов, к управляющему входу обращения блока памяти коэффициентов ассоциативности признаков, ко второму входу блока логических элементов И и к управляющему входу аналого-цифрового преобразователя, а первый вход блока управления подключен к управляющему входу устройства, выходы блока памяти коэффициентов ассоциативности признаков подключены непосредственно к соответствующим информационным входам блока сдвиговых регистров и к соответствующим первым входам блока логических элементов И, выходы которого подключены к соответствующим сдвиговым входам блока сдвиговых регистров, выходы которого являются выходами устройства, включены таймер, счетчик классов образов, счетчик адресов младших разрядов, дешифратор кода класса образа, буферный регистр, блок памяти распределений информативных признаков, блок сравнения, счетчик значений информативных признаков, элемент задержки и логический элемент И, причем информационные входы счетчика классов образов подключены к дополнительным информационным входам образов устройства, вход предварительной установки и счетный вход счетчика классов образов подключены соответственно к девятому и к тринадцатому выходу блока управления, выходы счетчика классов образов подключены к информационным входам дешифратора кода класса образа и к адресным входам кодов образов блока памяти распределений информативных признаков, а выходы счетчика адресов старших разрядов подключены к адресным входам кодов признаков блока памяти распределений информативных признаков, управляющий вход таймера подключен к дополнительному управляющему входу устройства и ко второму входу блока управления, а выход таймера подключен к третьему входу блока управления, выходы счетчика адресов младших разрядов подключены к адресным входам младших разрядов блоков памяти коэффициентов ассоциативности признаков и памяти распределений информативных признаков, выходы дешифратора кода класса образа подключены к соответствующим информационным входам блока памяти коэффициентов ассоциативности признаков, а информационные выходы блока памяти распределений информативных признаков подключены ко вторым входам блока сравнения и к информационным входам счетчика значений информативных признаков, выходы которого подключены к соответствующим информационным входам блока памяти распределений информативных признаков и к информационным входам буферного регистра, выходы которого подключены к первым входам блока сравнения, выход которого подключен ко входу элемента задержки, первый и второй входы логического элемента И подключены соответственно к выходу элемента задержки и к восьмому выходу блока управления, а выход логического элемента И подключен к управляющему входу буферного регистра и ко входу разрешения дешифрации дешифратора кода класса образа, пятый, шестой, седьмой, десятый, одиннадцатый и двенадцатый выходы блока управления подключены соответственно к управляющему входу обращения блока памяти распределений информативных признаков, ко входу предварительной установки счетчика значений информативных признаков, к счетному входу счетчика значений информативных признаков, к управляющему входу счетчика адресов младших разрядов, к управляющим входам чтения/записи блоков памяти коэффициентов ассоциативности признаков и памяти распределений информативных признаков.

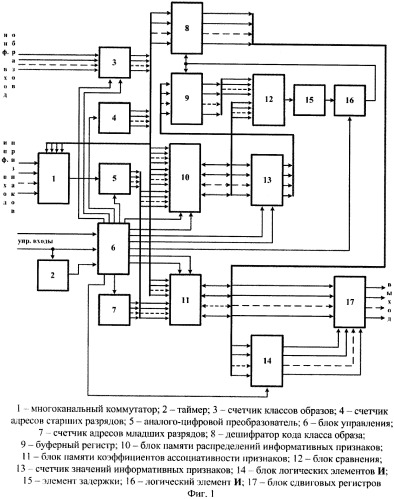

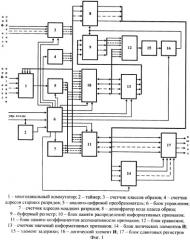

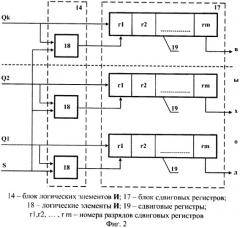

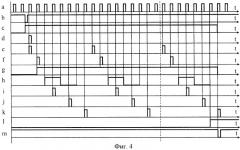

На фиг.1 представлена структурная схема предлагаемого устройства, на фиг.2 - структурные схемы блока логических элементов И и блока сдвиговых регистров, на фиг.3 для пояснения принципа работы предлагаемого устройства и, как пример реализации блока управления, представлена структурная схема блока управления. На фиг.4 - временная диаграмма формирования сигналов на выходе блока управления при выполнении первой операции режима обучения устройства, на фиг.5 - временная диаграмма формирования сигналов на выходе блока управления при выполнении второй операции режима обучения устройства, на фиг.6 - временная диаграмма формирования сигналов на выходе блока управления в режиме распознавания, а на фиг.7 для иллюстрации принципа работы предлагаемого устройства представлена таблица определения коэффициентов принадлежности значений признаков.

Устройство содержит многоканальный коммутатор 1, таймер 2, счетчик классов образов 3, счетчик адресов старших разрядов 4, аналого-цифровой преобразователь 5, блок управления 6, счетчик адресов младших разрядов 7, дешифратор кода класса образа 8, буферный регистр 9, блок памяти распределений информативных признаков 10, блок памяти коэффициентов ассоциативности признаков 11, блок сравнения 12, счетчик значений информативных признаков 13, блок логических элементов И 14, элемент задержки 15, логический элемент И 16, блок сдвиговых регистров 17, причем информационные входы многоканального коммутатора 1 подключены к информационным входам признаков устройства, информационный вход аналого-цифрового преобразователя 5 подключен к выходу многоканального коммутатора 1, адресные входы младших разрядов блока памяти коэффициентов ассоциативности признаков 11 подключены к выходу аналого-цифрового преобразователя 5, а адресные входы старших разрядов блока памяти коэффициентов ассоциативности признаков 11 подключены к выходам счетчика адресов старших разрядов 4 и к адресным входам многоканального коммутатора 1, выходы блока памяти коэффициентов ассоциативности признаков 11 подключены непосредственно к информационным входам блока сдвиговых регистров 17 и к соответствующим первым входам блока логических элементов И 14, вторые входы которого объединены и подключены к третьему выходу блока управления 6, а выходы подключены к соответствующим сдвиговым входам блока сдвиговых регистров 17, информационные входы счетчика классов образов 3 подключены к дополнительным информационным входам образов устройства, вход предварительной установки и счетный вход счетчика классов образов 3 подключены соответственно к девятому и к тринадцатому выходу блока управления 6, выходы счетчика классов образов 3 подключены к информационным входам дешифратора кода класса образа 8 и к адресным входам кодов образов блока памяти распределений информативных признаков 10, а выходы счетчика адресов старших разрядов 4 подключены к адресным входам кодов признаков блока памяти распределений информативных признаков 10, управляющий вход таймера 2 подключен к дополнительному управляющему входу устройства и ко второму входу блока управления 6, а выход таймера подключен к третьему входу блока управления 6, выходы счетчика адресов младших разрядов 7 подключены к адресным входам младших разрядов блоков памяти коэффициентов ассоциативности признаков 11 и памяти распределений информативных признаков 10, выходы дешифратора кода класса образа 8 подключены к соответствующим информационным входам блока памяти коэффициентов ассоциативности признаков 11, а информационные выходы блока памяти распределений информативных признаков 10 подключены ко вторым входам блока сравнения 12 и к информационным входам счетчика значений информативных признаков 13, выходы которого подключены к соответствующим информационным входам блока памяти распределений информативных признаков 10 и к информационным входам буферного регистра 9, выходы которого подключены к первым входам блока сравнения 12, выход которого подключен ко входу элемента задержки 15, первый и второй входы логического элемента И 16 подключены соответственно к выходу элемента задержки 15 и к восьмому выходу блока управления 6, а выход логического элемента И 16 подключен к управляющему входу буферного регистра 9 и ко входу разрешения дешифрации дешифратора кода класса образа 8, первый, второй, третий, четвертый, пятый, шестой, седьмой, десятый, одиннадцатый и двенадцатый выходы блока управления 6 подключены соответственно к управляющему входу счетчика адресов старших разрядов 4, к управляющему входу обращения блока памяти коэффициентов ассоциативности признаков 11, ко второму входу блока логических элементов И 14, к управляющему входу аналого-цифрового преобразователя 5, к управляющему входу обращения блока памяти распределений информативных признаков 10, ко входу предварительной установки счетчика значений информативных признаков 13, к счетному входу счетчика значений информативных признаков 13, к управляющему входу счетчика адресов младших разрядов 7, к управляющим входам чтения/записи блоков памяти коэффициентов ассоциативности признаков 11 и памяти распределений информативных признаков 12, а входы блока управления 6 являются управляющими входами устройства.

Блок логических элементов И 14, как показано на фиг.2, содержит логические элементы И 18, число которых равно числу распознаваемых классов образов k, причем первые входы логических элементов И 18 через первые входы блока логических элементов И 14 подключены к соответствующим информационным входам блока сдвиговых регистров 17 и к соответствующим выходам блока памяти коэффициентов ассоциативности признаков 11 Q1-Qk, где Q1 соответствует младшему разряду информационного слова блока памяти коэффициентов ассоциативности признаков 11, a Qk - старшему разряду. Вторые входы логических элементов И 18 блока логических элементов И 14 подключены к объединенным вторым входам блока логических элементов И 14 и к третьему управляющему выходу S блока управления 6, а выходы логических элементов И 18 блока логических элементов И 14 через соответствующие выходы блока логических элементов И 14 подключены к соответствующим сдвиговым входам блока сдвиговых регистров 17. Блок сдвиговых регистров 17, как показано на фиг.2, как и в известном устройстве, содержит k m-разрядных сдвиговых регистров 19, где m соответствует порогу распознавания, причем информационные входы первых разрядов сдвиговых регистров 19 блока сдвиговых регистров 17 подключены к выходам устройства. Под порогом распознавания в предлагаемом устройстве так же, как и в известном устройстве, понимается минимальное число положительных проверок m на принадлежность значений проверяемых признаков на максимум оценки распределения значений для некоторого класса образов, по достижении которого принимается решение о принадлежности проверяемой совокупности признаков данному классу. Этот термин достаточно широко используется в научно-технической литературе, например в работе Козлова Ю.М. "Адаптация и обучение в робототехнике" (- М.: Наука, 1990) на странице 221, а также в статье Тельных А., Когана А. и др. "Идентификация личности. Как это делается" (журнал "Компьютерра", №10, 1999 г.).

Блок управления, как показано на фиг.3, содержит логический элемент И-НЕ 20, триггеры запуска-останова 21, 22, 23, генератор тактовых импульсов 24, логические элементы И 25, 26, 27, а также блоки формирования и распределения управляющих сигналов 28, 29, 30, причем установочный вход триггера запуска-останова 21 подключен к управляющему входу устройства U1, выход - к первому входу логического элемента И 25, вторые входы логических элементов И 25, 26, 27 объединены и подключены к выходу генератора тактовых импульсов 24, а выход логического элемента И 25 подключен ко входу блока формирования и распределения управляющих сигналов 28, установочный вход триггера запуска-останова 22 подключен к дополнительному управляющему входу устройства U2, выход - к первому входу логического элемента И 26, выход которого подключен ко входу блока формирования и распределения управляющих сигналов 29, установочный вход триггера запуска-останова 23 подключен к выходу логического элемента И-НЕ 20, выход - к первому входу логического элемента И 27, выход которого подключен ко входу блока формирования и распределения управляющих сигналов 30, первый, второй, третий, четвертый, пятый и шестой выходы блока формирования и распределения управляющих сигналов 28 подключены соответственно к первому, четвертому, второму, одиннадцатому, третьему выходам блока управления 6 и к сбросовому входу триггера запуска-останова 21, первый, второй, третий, четвертый, пятый, шестой, седьмой и восьмой выходы блока формирования и распределения управляющих сигналов 29 подключены соответственно к первому, девятому, четвертому, пятому, двенадцатому, шестому, седьмому выходам блока управления 6 и к первому входу логического элемента И-НЕ 20, второй вход которого подключен к выходу таймера 2 T, а выход - к сбросовому входу триггера запуска-останова 22, первый, второй, третий, четвертый, пятый, шестой, седьмой, восьмой и девятый выходы блока формирования и распределения управляющих сигналов 30 подключены соответственно к первому, десятому, тринадцатому, пятому, двенадцатому, второму, одиннадцатому, восьмому выходам блока управления 6 и к сбросовому входу триггера запуска-останова 23.

На фиг.4 - временные диаграммы первой операции режима обучения устройства: "a", "b", "c", "d", "e", "f", "g", "h", "i", "j" "k", "l" и "m" представляют процессы формирования и поступления сигналов соответственно: с выхода генератора тактовых импульсов 24, на дополнительном управляющем входе устройства U2, на первом входе логического элемента И 26, на первом, втором, третьем, четвертом, пятом, шестом, седьмом, восьмом выходах блока формирования и распределения управляющих сигналов 29, с выхода таймера 2 T и с выхода логического элемента И-НЕ 20.

На фиг.5 - временные диаграммы второй операции режима обучения устройства: "a", "b", "c", "d", "e", "f, "g", "h", "k", "l", "m", "n", "i" и "j" представляют процессы формирования и поступления сигналов соответственно: с выхода генератора тактовых импульсов 23, на выходе логического элемента И-НЕ 20, на первом входе логического элемента И 27, на первом, втором, третьем, четвертом, пятом, шестом, седьмом, восьмом, девятом выходах блока формирования и распределения управляющих сигналов 30, с выхода блока сравнения 12 и с выхода элемента задержки 15.

На фиг.6 - временные диаграммы режима распознавания: "a", "b", "c", "d", "e", "f", "g", "h" и "i" представляют процессы формирования и поступления сигналов соответственно: с выхода генератора тактовых импульсов 24, на управляющем входе устройства U1, на первом входе логического элемента И 25, на первом, втором, третьем, четвертом, пятом и шестом выходах блока формирования и распределения управляющих сигналов на этапе распознавания 28.

На фиг.7 для иллюстрации принципа работы предлагаемого устройства представлена таблица определения коэффициентов принадлежности значений для трех признаков с кодами "01", "10" и "11" и трех классов образов с кодами "01", "10" и "11". В каждой ячейке таблицы содержится гистограмма оценок распределений значений признаков P(s) для конкретного класса образа. В нижней части таблицы представлены коэффициенты принадлежности значений признаков s1-s8, соответствующие каждому значению признака для каждого класса образа. Определение коэффициентов производится с учетом соотношений значений оценок распределений P(s) для одного признака для всех классов образов. При этом единичное значение коэффициента присваивается образу с максимальным значением P(s), а коэффициенты, принадлежащие остальным классам образов, принимают нулевое значение.

Предлагаемое устройство работает в двух режимах: обучения и распознавания. Режим обучения состоит из двух операций: первая операция - регистрация распределений информативных признаков и вторая операция - формирование коэффициентов ассоциативности признаков.

В режиме выполнения первой операции режима обучения предлагаемое устройство работает следующим образом. В исходном состоянии таймер 2, буферный регистр 9, все сдвиговые регистры 19 блока сдвиговых регистров 17 обнулены, а все разряды счетчика классов образов 3, счетчика адресов старших разрядов 4, счетчика адресов младших разрядов 7 и счетчика значений информативных признаков 13 содержат единицы. Каждая ячейка блока памяти распределений информативных признаков 10 содержит оценку распределения значения признака, соответствующего конкретному значению признака распознавания для соответствующего кода признака и кода класса образов. Причем старшие разряды адреса каждой ячейки блока памяти распределений информативных признаков 10 определяют код признака и код класса образов, являющийся и кодом адреса страницы блока памяти распределений информативных признаков 10. В каждой странице хранятся оценки распределений значений признаков, соответствующие значениям признака для соответствующего кода признака и кода класса образов. Запуск устройства для выполнения первой операции режима обучения производится подачей на дополнительный управляющий вход U2 (фиг.3) блока управления 6 и на вход таймера 2 сигнала "пуск 2". Таймер устанавливает длительность времени регистрации распределений признаков в режиме обучения. На дополнительный информационный вход образов подключен код первого класса образов, который заносится в счетчик классов образов 3 по сигналу предварительной установки с девятого выхода блока управления 6. При этом в счетчик адресов старших разрядов 4 из блока управления 6 поступает счетный импульс, который обнуляет все разряды счетчика адресов старших разрядов 4 для выбора первого информационного канала устройства, к которому подключен первый информативный признак, и выбора первой страницы блока памяти распределений информативных признаков 10. По управляющему сигналу с четвертого выхода блока управления 6 на управляющий вход аналого-цифрового преобразователя 5 производится преобразование аналогового сигнала первого признака в цифровой код, который поступает на адресные входы младших разрядов блока памяти распределений информативных признаков 10. По совокупному адресу, сформированному из кодов адреса счетчика классов образов 3, счетчика адресов старших разрядов 4 и кода с выхода аналого-цифрового преобразователя 5, по сигналам обращения и чтения, поступающим с пятого и двенадцатого выходов блока управления 6 на управляющие входы обращения и чтения/записи блока памяти распределений информативных признаков 10, значение с выхода блока памяти распределений информативных признаков 10, соответствующее оцифрованному значению информативного признака для первого кода признака и первого кода класса образов, поступает на информационные входы счетчика значений информативных признаков 13. На вход предварительной установки счетчика значений информативных признаков 13 с шестого выхода блока управления 6 поступает управляющий сигнал занесения оценки распределения значения признака с выхода блока памяти распределений информативных признаков 10. Далее с седьмого выхода блока управления 6 на счетчик значений информативных признаков 13 поступает счетный импульс, который инкрементирует оценку распределения значения признака. Сформированная оценка распределения значения признака с выхода счетчика значений информативных признаков 13 поступает на информационные входы блока памяти распределений информативных признаков 10. По сигналу записи, поступающему с двенадцатого выхода блока управления 6 на управляющий вход чтения/записи блока памяти распределений информативных признаков 10, оценка распределения значения признака заносится в блок памяти распределений исходных данных 10. Процедура регистрации распределений информативных признаков для первого кода класса образов завершается по управляющему сигналу Т (фиг.3) с выхода таймера 2. Затем аналогично осуществляется регистрация распределений информативных признаков для второго кода класса образов, которая завершается по управляющему сигналу Т (фиг.3) с выхода таймера 2. Обучение устройства для распознавания образов производится по окончании регистрации всех признаков и классов образов по конечному состоянию счетчика классов образов 3 при k=8 соответствует 111 и счетчика адресов старших разрядов 4 при n=8 соответствует 111.

В режиме выполнения второй операции режима обучения предлагаемое устройство работает следующим образом. Выполнение второй операции режима обучения производится автоматически блоком управления 6 по завершению выполнения первой операции режима обучения. При этом в счетчик адресов старших разрядов 4 и в счетчик классов образов 3 из блока управления 6 поступают импульсы, которые обнуляют содержимое счетчиков адресов старших разрядов 4 и классов образов 3, для выбора первых страниц блоков памяти распределений информативных признаков 10 и памяти коэффициентов ассоциативности признаков 11. В счетчик адресов младших разрядов 7 из блока управления 6 поступает импульс, который обнуляет содержимое счетчика адресов младших разрядов 6 для выбора первых ячеек блоков памяти распределений информативных признаков 10 и коэффициентов ассоциативности признаков 11. По управляющим сигналам обращения и чтения из блока памяти распределений информативных признаков 10, поступающим с пятого и двенадцатого выхода блока управления 6, производится считывание оценки распределения значения признака с выхода блока памяти распределений информативных признаков 10, которое поступает на вход буферного регистра 9 и на второй вход блока сравнения 12. В случае когда в процессе сравнения значение, поступившее с выхода блока памяти распределений информативных признаков 10, больше значения максимального числа, поступившего из буферного регистра 9, на выходе блока сравнения 12 появляется управляющий сигнал положительного уровня, который поступает через элемент задержки 15 на первый вход логического элемента И 16. Управляющий сигнал для занесения информации в буферный регистр 9 и разрешения дешифрации кода класса образа в дешифраторе кода класса образа 8 формируется логическим элементом И 16 при совпадении на его входах единичного кода от элемента задержки 15 и сигнала с восьмого выхода блока управления 6. При этом в буферный регистр 9 заносится новое максимальное значение с выхода блока памяти распределений информативных признаков 10. В случае когда в процессе сравнения значение, поступившее с выхода блока памяти распределений информативных признаков 10, меньше или равно значению максимального числа, поступившего из буферного регистра 9, на выходе блока сравнения 12 появляется сигнал отрицательного уровня, запрещающий изменение содержимого буферного регистра 9. Далее по управляющим сигналам обращения и записи в блок памяти коэффициентов ассоциативности признаков 11, по сигналу разрешения дешифрации, унарный код, соответствующий максимальному значению принадлежности признака соответствующему коду класса образов, с выхода дешифратора кода класса образа 8 поступает на соответствующие информационные входы блока памяти коэффициентов ассоциативности признаков 11. Далее процесс работы устройства аналогичен режиму с первыми страницами блоков памяти распределений информативных признаков 10 и памяти коэффициентов ассоциативности признаков 11.

В режиме распознавания предлагаемое устройство работает следующим образом. В исходном состоянии таймер 2, счетчик классов образов 3, счетчик адресов младших разрядов 7, буферный регистр 9, счетчик значений информативных признаков 13, все сдвиговые регистры 19 блока сдвиговых регистров 17 обнулены, а все разряды счетчика адресов старших разрядов 4 содержат единицы. Каждая ячейка блока памяти коэффициентов ассоциативности признаков 11 содержит данные о кодах классов образов, соответствующих конкретному значению признака распознавания. Причем старшие разряды адреса каждой ячейки блока памяти коэффициентов ассоциативности признаков 11 определяют код наименования признака, являющийся и кодом адреса страницы блока памяти коэффициентов ассоциативности признаков 11. В каждой странице хранятся коды классов образов по адресам, соответствующим значениям данного признака во всем диапазоне его изменения. Число информационных разрядов блока памяти коэффициентов ассоциативности признаков 11 соответствует числу распознаваемых классов образов k, причем первый (младший) разряд содержит не код принадлежности (0 или 1) оцифрованного значения признака первому классу образов, как в известном устройстве, а код принадлежности (0 или 1) максимальной оценки распределения данного значения признака первому классу образов, второй разряд - код принадлежности максимальной оценки распределения данного значения признака второму классу образов и так далее. Например, наличие единицы в младшем разряде информационного кода свидетельствует о том, что значение признака, соответствующее адресу, по которому хранится эта единица, имеет максимальную оценку распределения значения данного признака для первого класса образов. Наличие нуля в младшем разряде информационного кода свидетельствует о том, что значение признака, соответствующее адресу, по которому хранится этот ноль, не имеет максимальной оценки распределения значения данного признака для первого класса образов. Запуск устройства в режиме распознавания образов производится подачей на управляющий вход U1 (фиг.3) блока управления 6 сигнала "пуск 1". При этом в счетчик адресов старших разрядов 4 поступает счетный импульс, который обнуляет все разряды счетчика адресов старших разрядов 4 для выбора первого информационного канала устройства, к которому подключен первый признак распознавания, и выбора первой страницы блока памяти коэффициентов ассоциативности признаков 11. Далее по управляющему сигналу, поступающему с четвертого выхода блока управления 6 на управляющий вход аналого-цифрового преобразователя 5, производится преобразование аналогового сигнала первого признака в цифровой код, который поступает на адресные входы младших разрядов блока памяти коэффициентов ассоциативности признаков 11. По совокупному адресу, сформированному из кода адреса счетчика адресов старших разрядов 4 и цифрового кода с выхода аналого-цифрового преобразователя 5, по сигналам обращения и чтения, поступающим со второго и одиннадцатого выхода блока управления 6 на управляющий вход блока памяти коэффициентов ассоциативности признаков 11, коды классов образов, соответствующие оцифрованному значению первого признака, с выхода блока памяти коэффициентов ассоциативности признаков 11 поступают на информационные входы блока сдвиговых регистров 17 и на первые входы блока логических элементов И 14. Далее на объединенные вторые входы блока логических элементов И 14 с третьего выхода блока управления 6 поступает управляющий сигнал занесения-сдвига для сдвиговых регистров 19, на информационных входах первых разрядов которых установлен единичный код, поступивший из блока памяти коэффициентов ассоциативности признаков 11. Сигнал занесения-сдвига на сдвиговом входе сдвигового регистра 19 формируется логическим элементом И 18 блока логических элементов И 14 при совпадении на его входах единичного кода из блока памяти коэффициентов ассоциативности признаков 11 и сигнала с третьего выхода блока управления 6. По сигналу занесения-сдвига единичные коды классов образов через информационные входы первых разрядов сдвиговых регистров 19 блока сдвиговых регистров 17 заносятся в сдвиговые регистры 19. При этом порядковый номер каждого сдвигового регистра 19 блока сдвиговых регистров 17 соответствует порядковому номеру информационного разряда блока памяти коэффициентов ассоциативности признаков 11, начиная с младшего разряда, и соответственно номеру класса образов. На этом завершается процедура проверки значения первого признака на соответствие для всех классов образов. Далее аналогично по сигналам блока управления 6 через многоканальный коммутатор 1 к информационному входу аналого-цифрового преобразователя 5 подключается информационный канал второго признака распознавания, а на адресные входы старших разрядов блока памяти коэффициентов ассоциативности признаков 11 поступает код адреса, определяющий вторую страницу блока памяти коэффициентов ассоциативности признаков 11. Далее процесс работы устройства аналогичен режиму с первым информативным признаком.

Идентификация класса образа производится по окончании ввода всех признаков распознавания по конечному состоянию последних разрядов сдвиговых регистров 19 блока сдвиговых регистров 17. Наличие единичного кода в последнем разряде сдвигового регистра 19 блока сдвиговых регистров 17 свидетельствует о принадлежности исследуемых признаков распознавания классу образов, соответствующему порядковому номеру этого сдвигового регистра.

При наличии ситуаций, когда в процессе распознавания получаются максимальные оценки распределений значений различных признаков для различных классов образов, в предлагаемом устройстве ошибки распознавания не происходит, поскольку результат распознавания формируется по большинству признаков. Для этого число разрядов m сдвиговых регистров 19 блока сдвиговых регистров 17 выбирается с учетом возможного числа таких ситуаций, причем должны выдерживаться соотношения: m≥s+1 и s≥]n/2[ при m<n, где функционал в обратных квадратных скобках означает целую часть отношения. Например, для учета однократного выхода при n=3, число разрядов сдвигового регистра m=2. Если в качестве примеров принять s, равное 2, 3 или 4, то с учетом вышеприведенных соотношений минимальные значения параметра m будут равны соответственно 3, 4 или 5, при этом минимальные значения n будут равны соответственно 4, 6 или 8.

Принципы работы логических элементов И 18 блока логических элементов И 14 и сдвиговых регистров 19 блока сдвиговых регистров 17, приведенных на фиг.2, представлены в описании работы предлагаемого устройства.

Блок управления 6, структурная схема которого представлена на фиг.3, при выполнении первой операции режима обучения работает следующим образом. В исходном состоянии триггеры пуска-останова 21, 22, 23 обнулены, на первом входе логического элемента И 26 установлен отрицательный уровень, и импульсы с выхода генератора тактовых импульсов 24, представленные на временной диаграмме "a" фиг.4, не поступают на выход логического элемента И 26. При подаче на дополнительный управляющий вход U2 устройства сигнала "пуск 2", который поступает в виде импульса отрицательной полярности так, как показано на временной диаграмме "b" на фиг.4, триггер пуска-останова 22 переключается в единичное состояние. Это отражено на временной диаграмме "c". При этом импульсы генератора тактовых импульсов 24 поступают на вход блока формирования и распределения управляющих сигналов 29, который выдает последовательно на девятый, первый, четвертый, пятый, двенадцатый, шестой и седьмой выходы блока управления 6 сигналы занесения кода класса образа в счетчик классов образов 3 так, как показано на диаграмме "d", сигналы изменения адреса в счетчике адресов старших разрядов 4 так, как показано на диаграмме "e", сигналы запуска аналого-цифрового преобразователя 5, представленные на диаграмме "f", сигналы обращения к блоку памяти распределений информативных признаков 10, представленные на диаграмме "g", сигналы чтения и записи в блок памяти распределений информативных признаков 10 так, как показано на диаграмме "h", сигналы занесения и инкремента значения в счетчике значений информативных признаков 13, представленные на диаграммах "i" и "j". По окончании регистрации значений информативных признаков для соответствующего кода класса образов блок формирования и распределения управляющих сигналов 29 на свой восьмой выход подает сигналы сброса триггера пуска-останова 22, которые поступают на вход логического элемента И-НЕ 20. На втором входе логического элемента И-НЕ 20 установлен отрицательный уровень, и импульсы с выхода блока формирования и распределения управляющих сигналов 29, представленные на временной диаграмме "k" фиг.4, не поступают на выход логического элемента И-НЕ 20. Регистрация распределений информативных признаков завершается по управляющему сигналу Т с выхода таймера 2. При этом на второй вход логического элемента И-НЕ 20 подается управляющий сигнал так, как показано на временной диаграмме "l" на фиг.4, триггер пуска-останова 22 переключается в исходное состояние так, как показано на временной диаграмме "m" на фиг.4, а триггер пуска-останова 23 автома