Способ оцифровки аналоговой величины, оцифровывающее устройство, осуществляющее указанный способ, и детектор электромагнитного излучения, содержащий такое устройство

Иллюстрации

Показать всеИзобретение предназначено для оцифровки аналоговой величины (VE), выходящей из детектора электромагнитного излучения, содержащего матрицу смежно расположенных элементарных датчиков. Достигаемый технический результат - увеличение точности преобразования. Способ заключается в выполнении первой фазы интегрирования упомянутой аналоговой величины с использованием каскада (410) интегратора; в интегрировании (VS) до первого числового значения (В) посредством двоичного счетчика (442) и элемента (441) памяти, соединенного с выходом (440) упомянутого каскада (420) компаратора; в преобразовании первого числового значения (В) в аналоговый сигнал (VDAC) посредством аналого-цифрового преобразователя (451); в вычитании упомянутого аналогового сигнала (VDAC) из оцифровываемой аналоговой величины (VE); в усилении сигнала (VE-VDAC), с коэффициентом усиления, отображающим упомянутое первое числовое значение (В); в выполнении второй фазы (303) интегрирования, с использованием упомянутого каскада (410) интегратора, для получения второго числового значения (М), пропорционального аналоговому сигналу, и формирования второго двоичного числа, отображающего младшие биты; в добавлении упомянутого первого (В) и второго (М) числовых значений для формирования числа (N), отображающего упомянутую интегрируемую аналоговую величину (VE). 3 н. и 9 з.п. ф-лы, 5 ил.

Реферат

Область техники, к которой относится изобретение

Настоящее изобретение относится к способу выполнения преобразования аналоговых величин в цифровые сигналы, причем упомянутые величины, в частности, производятся детектором электромагнитного излучения. Настоящее изобретение относится также к устройству для выполнения такого преобразования.

Поэтому в общем смысле настоящее изобретение относится к применению детекторов электромагнитного излучения и к конструкции и работе их схемы считывания.

Уровень техники

Известен вариант, когда детекторы электромагнитного излучения составлены из множества смежно расположенных элементарных датчиков, формирующих матрицу, с множеством строк и столбцов. Взаимодействия падающего электромагнитного излучения с этими элементарными датчиками, называемыми также пикселями, производят вариации электрической величины в соответствии с потоком энергии падающего излучения.

Микроболометрическая инфракрасная отображающая сетчатка - один из примеров такого детектора. В этом случае детектор работает как термистор, чувствительный к тепловому излучению, которое измеряется интегрированием тока, проходящего через него при действии данного смещающего напряжения в течение данного периода времени, посредством схемы считывания, связанной с элементарными датчиками.

Проинтегрированные заряды формируют при этом аналоговые сигналы или величины. Для упрощения электрических интерфейсов с электроникой, внешней относительно схемы считывания, эти аналоговые величины преобразуются в цифровые сигналы для восстановления двумерного изображения, адекватного наблюдаемой картине.

Известно, что рабочая характеристика детектора, а следовательно, и качество данных, которые он выдает (цифровые изображения, например), зависят, в частности, от характеристик преобразования в цифровые сигналы аналоговых величин, отображающих взаимодействия между падающим излучением и элементарными датчиками. На предшествующем уровне техники известны по существу три принципа преобразования аналоговых величин в цифровые сигналы, объединенные в схеме считывания.

Во-первых, существуют детекторы, для которых единственное устройство преобразования, или преобразователь, последовательно оцифровывает аналоговые данные, переданные каждым из датчиков, составляющих матрицу. Обычно считывание таких детекторов выполняется последовательно, посредством сканирования строк и затем столбцов. При этом продолжительность, или время, аналого-цифрового преобразования в лучшем случае равна времени считывания элементарного датчика детектирующей матрицы.

В соответствии со вторым принципом преобразования каждый столбец детектора снабжен устройством преобразования. Время аналого-цифрового преобразования при этом в лучшем случае равно времени считывания строки детектора.

В соответствии с третьим принципом преобразования каждый датчик детектора снабжен таким устройством преобразования. При этом время аналого-цифрового преобразования в лучшем случае равно общему времени считывания всех датчиков матрицы.

Выбор принципа преобразования и, следовательно, соответствующего устройства или способа может быть сделан в соответствии с такими критериями, как, например, время преобразования устройства преобразования, его разрешение, его размер, его потребляемая мощность и т.д.

В частности, во втором варианте, в котором каждый столбец матрицы имеет свое собственное устройство преобразования, его размер должен быть уменьшен до шага повторения двух смежных столбцов пикселей, а в третьем варианте размер должен быть уменьшен в обоих измерениях до шага повторения элементарного пикселя. Шаг повторения фактически представляет собой расстояние между двумя смежными датчиками и обычно соответствует размеру пикселя окончательного цифрового изображения.

Кроме того, когда применяется множество устройств преобразования с высокой разрешающей способностью на одной и той же схеме, каждое из устройств преобразования может быть чувствительным к электрическим возмущениям, создаваемым соседними устройствами преобразования. Фактически чем выше разрешение преобразователя, тем меньше разность напряжения, соответствующая двум последовательным цифровым значениям, и, следовательно, она более чувствительна к внешним возмущениям. Эта чувствительность обусловлена, в частности, конструкцией устройств преобразования, которые электрически не независимы, а, наоборот, имеют общую подложку и те же самые рамки, или те же самые источники питания.

С другой стороны, выбор архитектуры устройств преобразования, число которых велико, расположение и компоновка электронных компонентов должны быть определены для минимизации общего потребления энергии схемой считывания. Фактически, кроме того, что для бортовых электронных систем инфракрасного отображения, например, энергосбережение является очень важным требованием, важно также ограничить рассеяние в фокальной плоскости, поскольку матрица детектора в принципе чувствительна к тепловому окружению.

Среди принципов преобразования, осуществленных в архитектуре преобразователей предшествующего уровня техники, можно отметить принцип, обозначаемый как "преобразование напряжение-время". Этот способ заключается в длительном интегрировании аналоговой величины, напряжения, пока оно не достигнет опорного значения. Интегрирование прерывается при достижении этого опорного значения, обозначая окончание фактической фазы интегрирования. В случае интегрирования, выполненного обычной интегрирующей матрицей с отдельным линейно изменяющимся сигналом с одной крутизной, время, необходимое аналоговой величине для достижения опорного значения, прямо пропорционально значению этой аналоговой величины.

Фактически, поскольку интегрирующая сборка имеет единственную крутизну, изменение аналоговой величины за время интегрирования линейно. При этом, как известно, достаточно измерить время интегрирования как множество временных периодов счета для преобразования значения этой аналоговой величины, то есть оцифровать ее. Таким образом, простой счет числа опорных тактовых импульсов, измеряющих это время, непосредственно предоставляет числовое значение проинтегрированной аналоговой величины.

Для определения окончания счета дифференциальное устройство сравнивает аналоговую величину с опорным значением; когда их различие пренебрежимо мало и меняет знак, этот компаратор передает сигнал для установления текущего цифрового значения счетчика и тем самым определяет значение аналоговой величины.

Практически, как известно, когда счетчик принимает импульс от тактового генератора, он увеличивает двоичное число на одну единицу. Следовательно, число посчитанных битов зависит от требуемого разрешения устройства преобразования, то есть числа шагов дискретизации, используемых для выборки максимальной аналоговой величины.

Таким образом, для устройства преобразования, использующего 2N шагов дискретизации для выборки интегрируемой аналоговой величины, счетчик должен содержать N подсчитываемых битов. Время преобразования аналоговой величины таким преобразователем в этом случае находится между нулем и максимальным значением 2N/fh-, где fh - тактовая частота. Таким образом, если P отображает число импульсов, подаваемых тактовым генератором до тех пор, пока аналоговая величина не достигнет опорного значения каскада компаратора, P равно цифровому значению сигнала, и время преобразования сигнала составляет P/fh.

Однако такой способ преобразования имеет недостатки, возможно, ограничивающие рабочие параметры такого аналого-цифрового преобразователя. Таким образом, для увеличения его разрешения и/или снижения его времени преобразования необходимо использовать генератор тактовых импульсов с более высокой частотой. Фактически, с одной стороны, имеется технологический предел для максимальной частоты тактового генератора, а с другой, известно, что потребление мощности преобразователя увеличивается с этой частотой и может стать неприемлемым для некоторых приложений.

Одно из решений этой проблемы в технике предшествующего уровня заключается в увеличении числа угловых коэффициентов интегрирования преобразователя и, следовательно, в разработке устройств преобразования с единственным линейно изменяющимся сигналом с множественным наклоном. Таким образом, в случае устройства преобразования с единственным линейно изменяющимся сигналом с двойным наклоном первый угловой коэффициент интегрирования используется для определения числа P, соответствующего значению входной аналоговой величины с большим шагом дискретизации. И наоборот, второй угловой коэффициент используется для преобразования с малым шагом дискретизации, причем оставшаяся часть определяется разностью между входным аналоговым значением и высоким аналоговым значением, соответствующим точно числу P. Эта оставшаяся часть, или остаток, соответствует низкому значению аналоговой величины.

Обычно делается различие между первым числовым значением, закодированным битами, называемыми "старшие" биты, и вторым числовым значением, закодированным битами, называемыми "младшие" биты. Из-за неправильного обращения с языком интегрированные аналоговые величины определяются таким же образом (самый существенный и наименее существенный), как и числовые значения (биты), которые отображают их после этапа оцифровки. В контексте настоящего патента числовое значение означает двоичные числа, составленные из "0" и "1".

Таким образом, число N битов на преобразователе разбивается на два "субчисла", то есть число, соответствующее старшим битам, обозначается NMSB (MSB для "старших битов"), и число, соответствующее младшим битам, обозначается NLSB (LSB для "младших битов"). По определению, сумма этих двух чисел NMSB и NLSB равна N, то есть общему числу битов, относящихся к устройству преобразователя.

Известно, что способ интегрирования с двумя угловыми коэффициентами призван снизить время преобразования для детектора. Фактически, в зависимости от значения интегрируемой аналоговой величины, это время изменяется между нулем и максимальным значением (2NMSB+2NLSB)/fh. Поэтому это время оказывается короче максимального времени 2N/fh, необходимого для устройства преобразования с единственным наклоном.

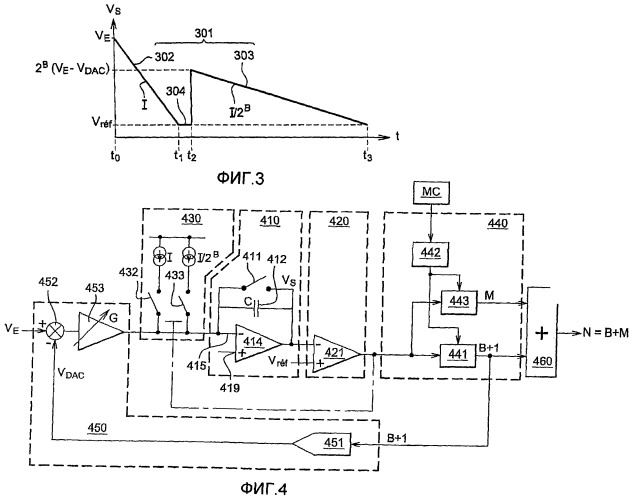

На Фиг.1 показан график, иллюстрирующий способ преобразования предшествующего уровня техники с единственным линейно изменяющимся сигналом с двойным наклоном. На этом графике ось X отображает время t, а ось Y отображает выходное напряжение VS, то есть аналоговую величину, произведенную взаимодействиями между датчиками и излучением в момент его обработки схемой интегратора.

В соответствии с таким способом преобразования с единственным линейно изменяющимся сигналом с двойным угловым коэффициентом, кривая 101 показывает интегрирование входного напряжения VE, вводимого в схему интегратора. Кривая 101 содержит наклон, называемый большим, 102, и наклон, называемый малым, 103. В контексте настоящего патента "большой" означает наклон с большим абсолютным значением углового коэффициента, тогда как "малый" означает наклон с угловым коэффициентом с малым абсолютным значением. Таким образом, большой наклон 102 отображает фазу интегрирования старших битов (большие аналоговые величины), тогда как низкий наклон 103 отображает фазу интегрирования младших битов (малые аналоговые величины).

По определению, каждая фаза интегрирования имеет место в течение временного интервала, ограниченного двумя моментами, которые соответственно формируют нижнюю границу и верхнюю границу этого временного интервала. Первая фаза интегрирования t0-t1 (большой наклон 102) прерывается синхронно с частотой тактового генератора fh, когда проинтегрированное напряжение VE превысит опорное значение Vref, то есть когда различие между проинтегрированным напряжением VE и опорным значением Vref исчезает. Это условие тем самым определяет верхнюю границу t1 временного интервала первой фазы интегрирования t0-t1.

В соответствии с этим способом преобразования вторая фаза интегрирования (малый наклон 103) начинается в конце первой фазы интегрирования. Иначе говоря, нижняя граница t1 второго временного интервала t1-t2 по существу сливается с верхней границей t1 первого временного интервала t0-t1. Затем эта вторая фаза интегрирования прерывается, когда сумма напряжений, проинтегрированных в течение двух фаз интегрирования, превысит значение входного напряжения VE.

Как указано выше, время измеряется числом импульсов, подаваемых опорным тактовым генератором (не показан). Поскольку кривые 102 и 103 представляют собой участки прямых линий, импульсы тактового генератора поэтому отображают то, насколько много имеется шагов дискретизации проинтегрированного напряжения и поэтому самого этого интегрирования напряжения. Поэтому этот способ аналого-цифрового преобразования называется "напряжение-время".

В соответствии с этим способом каждый из наклонов, большой 102 или малый 103, служит для кодирования числа, соответственно отображающего старшие биты (MSB) и младшие биты (LSB). Эти числа служат тем самым для воссоздания изображения, отображающего наблюдаемую картину в виде двоичной цифровой величины. Таким образом, аналоговая величина может быть преобразована в цифровой сигнал с разрешением, по меньшей мере, 12 битов и временем преобразования 60 мкс.

Фактически это время преобразования совместимо с просмотром 60 изображений/с для детектора, обычно составленного из 320x240 строк. С другой стороны, способ преобразования "напряжение-время" с единственным угловым коэффициентом дает время преобразования, слишком большое для такого разрешения. В настоящем контексте разрешение преобразователя означает способность преобразователя различать два соседних проинтегрированных напряжения. Это разрешение выбирается, в частности, в соответствии с желаемым применением детектора. Очевидно, что чем выше выбирается это разрешение, тем больше время аналого-цифрового преобразования.

Фактически разрешение не зависит от дискретизации интегрируемой величины. Известно, что этот шаг дискретизации имеет значение динамического диапазона детектора, разделенного на 2N (число 2, возведенное в степень числа N битов, кодирующих максимальное значение этого динамического диапазона).

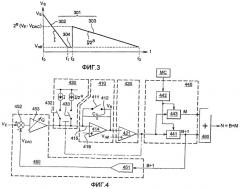

Практически, чтобы осуществить этот способ преобразования, каждый столбец матрицы детектора снабжен устройством преобразования или аналого-цифровым преобразователем. На Фиг.2 показан такой преобразователь предшествующего уровня техники. Он содержит последовательно включенные каскад 210 интегратора, дифференциальный или компараторный каскад 220, каскад 230 управления и считающий каскад 240.

Каскад 210 интегратора предназначен для интегрирования входного напряжения VE, произведенного столбцом элементарных датчиков. Дифференциальный каскад 220 служит для сравнения проинтегрированного напряжения VE с опорным значением Vref для определения первой фазы интегрирования от t0 до t1, обозначенной как t0-t1, и второй фазы интегрирования от t1 до t2, обозначенной как t1-t2. Управляющий каскад 230 служит для управления каскадом 210 интегратора, чтобы выполнить две фазы интегрирования последовательно с большим наклоном 102 и малым наклоном 103. Наконец, считающий каскад 240 служит для счета числа импульсов, подаваемых тактовым генератором 250 в течение каждой из этих фаз интегрирования t0-t1 и t1-t2, и, следовательно, для дискретизации проинтегрированного напряжения VE.

Каскад 210 интегратора может содержать входное сопротивление 211, соединенное с реверсивным входом 215 операционного усилителя 214 и конденсатором 212, установленным параллельно между реверсивным входом 215 и выходом 216 операционного усилителя 214. Конденсатор 212 служит для выполнения интегрирования входной аналоговой величины VE.

Каскад 220 сравнения по существу содержит два компаратора 221, 223, нереверсивные входы 222, 224 которых связаны соответственно с опорными напряжениями Vref1 и Vref2. Напряжение VE, проинтегрированное каскадом 210 интегратора, прикладывается к реверсивным входам изменения компараторов 221, 223 и может, таким образом, сравниваться с этими двумя опорными напряжениями. Как указано выше, это "сравнение", или измерение их разности, служит для определения верхних границ t1 и t2 большого наклона 102 и малого наклона 103 фаз интегрирования.

Кроме того, параллельно управляющему каскаду установлены два переключателя 232 и 233 для выбора одного или другого источника питания, I и I/2B - для разряда интегрирующего конденсатора 212. Переключатель означает любое устройство, подходящее для переключения схемы из разомкнутого состояния в замкнутое состояние и наоборот. Практически переключатели могут быть образованы транзисторами. При этом управляющий каскад 230 определяет коэффициент усиления каждой из двух фаз 102 и 103 интегрирования, который в данном случае обратно пропорционален емкости интегрирующего конденсатора 212.

Кроме того, когда он принимает сигналы "отмена", переданные каскадом компаратора, логическая схема управления 231, передавая соответствующий сигнал на его выходы 234, 235, останавливает счетчики 241, 242 импульсов, подаваемых опорным тактовым генератором.

При работе, когда разность между проинтегрированным напряжением VE и опорным напряжением Vref исчезает и затем изменяет знак, компаратор 221 передает сигнал "отмена" на логическую управляющую схему 231 управляющего каскада 230. Эта логическая схема 231, в свою очередь, управляется, синхронно с частотой fh тактового генератора 250, двумя счетчиками 241 и 242.

В течение временного интервала t0-t1 счетчик 241 определяет количество старших битов, составляющих проинтегрированную аналоговую величину. Затем, в течение временного интервала t1-t2, счетчик 242 определяет младшие биты, составляющие проинтегрированную аналоговую величину. Старшие и младшие биты могут быть затем добавлены в двоичном виде с использованием элемента 260 для формирования двоичного числа, отображающего значение проинтегрированной аналоговой величины.

Электрическая архитектура, описанная выше в связи с преобразователем на Фиг.1, имеет, таким образом, электронные компоненты, необходимые для осуществления этого способа преобразования предшествующего уровня техники. При этом, когда этот тип преобразователя используется в матричном детекторе, имеющем число С столбцов, для выполнения преобразования необходимо следующее:

С схем интегратора,

2·C схем компаратора,

и 2·С счетчиков.

Фактически, чем больше число электронных компонентов, тем выше их общее потребление мощности и тем более нагреваются схемы. Кроме того, занимаемое этими электронными компонентами пространство ограничивает малость шага повторения между двумя смежными столбцами датчиков. Кроме того, производственные возможности соразмерно ниже, и, следовательно, производственные затраты очевидно выше при большем числе электронных компонентов в преобразователе.

Этот способ преобразования с двумя наклонами поэтому призван снизить время преобразования аналоговой величины, поскольку время преобразования составляет: tconv1=(2В+2М)/fh, где В и М соответственно отображают числа старших и младших битов и 1/fh - период осуществления выборки или период импульсов тактового генератора Th.

Для его части система преобразования с единственным угловым коэффициентом требует времени преобразования: tconv2=2N/fh, где N - число В+М общих битов.

Легко убедиться, что tconv1<tconv2.

Однако способы и устройства преобразования, работающие с двумя угловыми коэффициентами интегрирования, в настоящее время сталкиваются с несколькими трудностями, которые ограничивают их характеристику оцифровки.

Во-первых, поскольку каждый столбец матричного детектора имеет свое собственное устройство преобразования, его размер ограничивает снижение шага повторения, а следовательно, и миниатюризацию детектора. Фактически устройство преобразования предшествующего уровня техники, подобное показанному на Фиг.2, требует установки двух компараторов и двух счетчиков для кодирования проинтегрированной аналоговой величины. Установка этих двойных компонентов поэтому увеличивает размер устройства преобразования, например, по сравнению с размером устройства преобразования с единственным линейно изменяющимся сигналом.

Кроме того, каждый компаратор 221 и 223 имеет свой собственный порог переключения. Фактически смещение напряжения между порогами этих двух компараторов очень низко, и оказывается затруднительным создать опорные напряжения Vref1 и Vref2 с достаточной точностью для оцифровки младших битов.

Таким образом, например, когда первая фаза t0-t1 интегрирования дискретизирует интегрируемую аналоговую величину, используя множество в восемь битов, называемых старшими битами, смещение напряжения между порогами этих двух компараторов имеет значение полного динамического диапазона детектора, разделенного на 28. Малость этого смещения поэтому требует высокой точности при образовании опорных напряжений Vref1 и Vref2, при условии Vref2>Vref1.

Кроме того, если учесть смещение напряжения двух компараторов, то для случая противоположных знаков можно найти, что условие:

Vref2+Voff2>Vref1+Voff1

не удовлетворяется.

Другая трудность является результатом того, что компаратор 223, установленный для оцифровки младших битов, работает в ограниченном диапазоне напряжения, что делает его очень чувствительным к шуму и к электрическим возмущениям, случающимся в схеме, особенно в момент переключения переключателей 232 и 233. Точность дискретизации, требуемая для операционного усилителя 223, должна быть ниже, чем младшие биты преобразователя. Максимальная допустимая ошибка должна быть ниже полного динамического диапазона детектора, разделенного на 2N, где N - разрешение устройства преобразования. Найдено, что для высокого N эта ошибка очень мала.

Кроме того, использование двух различных операционных усилителей-компараторов 221 и 223 для двух линейно изменяющихся сигналов 102 и 103 с различными угловыми коэффициентами, то есть с малым наклоном и большим наклоном, приводит к различному гистерезису для каждого компаратора. Это различие в гистерезисе вызывает нерегулярность или нелинейность в смене наклона, происходящей в момент времени t1.

Кроме того, отношение двух токов разряда I и I/2B должно также быть определено достаточно точно, без шума, чтобы избежать нелинейности. В частности, в случае преобразования в конце каждого столбца, сталкиваются с проблемой спаривания источников питания транзистора, когда число столбцов велико.

В технике предшествующего уровня возможны решения, обеспечивающие компенсацию смещения напряжения усилителя, установленного как компаратор, и корректирующие разности в коэффициенте усиления при большом и малом угловых коэффициентах. Это возможно, например, при использовании системы самокалибровки, объединенной с устройством преобразования и содержащей дополнительные электронные компоненты, например потенциометр.

Однако эти дополнительные электронные компоненты усложняют сборку и, главным образом, увеличивают область, занятую устройством преобразования. Фактически такой преобразователь должен быть пригоден для размещения в конце каждого столбца, на маленькой площади, на которой одно измерение определяется шагом повторения пикселя, что обычно составляет значение между 15 мкм и 45 мкм, которое, очевидно, должно быть минимизировано.

Можно также отметить, что два принципа коррекции, обычно используемые при инфракрасном отображении, призваны скорректировать коэффициент усиления и скомпенсировать смещение напряжения каждого пикселя. Однако эта коррекция никак не действует на смещение, случающееся на разрыве углового коэффициента преобразователя с двойным линейным изменением сигнала, как показано для момента времени t1 на Фиг.1, то есть эта коррекция не действует на ошибки линейности.

Задача настоящего изобретения заключается в преодолении трудностей, встречающихся в способах и устройствах преобразования предшествующего уровня техники, не увеличивая область, занятую таким преобразователем.

Сущность изобретения

Таким образом, настоящее изобретение относится к способу и устройству для преобразования аналоговых величин в цифровые сигналы, которые призваны по существу улучшить рабочие характеристики способов и устройств предшествующего уровня техники. Настоящее изобретение призвано, в частности, увеличить точность преобразования при снижении числа электронных компонентов, их потребления энергии, их размера и стоимости производства аналого-цифрового преобразователя, по сравнению с преобразователями предшествующего уровня техники.

Первой задачей изобретения является способ для аналого-цифрового преобразования, позволяющий точное и воспроизводимое преобразование интегрируемой аналоговой величины. Такой способ пригоден для оцифровки аналоговой величины, произведенной детектором электромагнитного излучения, в частности инфракрасного излучения. Упомянутый детектор содержит матрицу смежно расположенных элементарных датчиков, взаимодействия которых с излучением производят интегрируемую аналоговую величину. В соответствии с изобретением упомянутый способ содержит этапы, состоящие, для каждой строки или для каждого столбца матрицы:

в выполнении первой фазы интегрирования упомянутой аналоговой величины по первому временному интервалу с использованием каскада интегратора;

в задании прерывания упомянутой первой фазы интегрирования посредством каскада компаратора, у которого один вход связан с выходом упомянутого каскада интегратора, и другой вход - с опорной схемой, подающей опорное значение;

в преобразовании аналоговой величины, тем самым проинтегрированной до первого числового значения посредством двоичного счетчика, соединенного с выходом упомянутого каскада компаратора;

в сохранении упомянутого первого числового значения в форме первого двоичного числа, отображающего старшие биты;

в преобразовании упомянутого первого числового значения, полученного таким образом, в аналоговый сигнал, подобный оцифровываемой аналоговой величине, посредством аналого-цифрового преобразователя;

в вычитании упомянутого аналогового сигнала из упомянутой оцифровываемой аналоговой величины;

в усилении сигнала, получающегося из упомянутого вычитания с коэффициентом усиления, отображающим упомянутое первое числовое значение;

в выполнении второй фазы интегрирования с использованием упомянутого каскада интегратора для производства второго числового значения, пропорционального аналоговому сигналу, тем самым усиленного, и формировании второго двоичного числа, отображающего младшие биты;

в добавлении упомянутого первого и второго числовых значений для формирования числа, отображающего упомянутую интегрируемую аналоговую величину.

Таким образом, оцифровка интегрируемой аналоговой величины разбивается на две фазы интегрирования (два угловых коэффициента) для старших битов и младших битов соответственно, тем самым способствуя быстрой оцифровке аналоговой величины при использовании единственного компаратора. В течение второй фазы интегрирования интегрируемый остаток оценивается исключением значения старших битов, преобразованных в аналог, из интегрируемой аналоговой величины. Кроме того, аналоговый сигнал, отображающий младшие биты, усиливается с коэффициентом, призванным увеличить точность, то есть уменьшить максимальную ошибку второй фазы интегрирования.

Практически коэффициент усиления может иметь значение два, возведенное в степень, равную числу битов первого числового значения.

Таким образом, усиление остатка интегрируемой аналоговой величины призвано уменьшить максимальную ошибку второй фазы интегрирования, следовательно, снизить ограничение на точность этого аналого-цифрового преобразователя.

Практически первое числовое значение может быть увеличено на один младший бит перед упомянутым этапом преобразования, чтобы скорректировать смещение напряжения, представленное каскадом компаратора.

Этот признак способа в соответствии с изобретением служит поэтому для компенсации смещения напряжения, предоставленного операционным усилителем каскада компаратора.

В соответствии с конкретным вариантом реализации изобретения каскад интегратора может содержать конденсатор, и способ может содержать этапы, состоящие:

в зарядке упомянутого конденсатора преобразуемой аналоговой величиной;

в разряде упомянутого конденсатора при большом постоянном токе в течение первой фазы интегрирования;

в перезарядке упомянутого конденсатора напряжением, зависящим от разности между интегрируемой аналоговой величиной и результатом первой фазы преобразования;

в разряде упомянутого конденсатора при малом постоянном токе в течение второй фазы интегрирования.

Прилагательные "большой" и "малый" имеют относительный смысл. Фактически на практике величина малого тока может быть выбрана как равная отношению величины большого тока к числу 2, возведенному в степень, равную числу битов первого числового значения. Например, если это первое числовое значение составляет 8 битов, малое значение составляет 1/256 от большого значения. Такие токи разряда служат для достаточного определения угловых коэффициентов, для получения хорошей точности в течение каждой из фаз интегрирования. Кроме того, поскольку разряды выполняются при постоянном токе, между напряжением и временем устанавливается непосредственное соотношение.

Практически опорное значение может быть определено как функция диапазона чувствительности детектора.

Этот признак служит для оптимизации средних времен преобразования всех аналоговых величин для динамического диапазона выбранных детекторов.

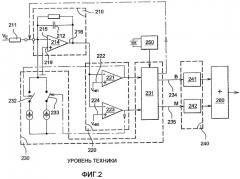

Кроме того, изобретение относится к устройству для оцифровки аналоговой величины, выходящей из детектора электромагнитного излучения. В соответствии с изобретением упомянутое устройство содержит для каждого столбца матрицы:

каскад интегратора, содержащий операционный усилитель, по меньшей мере, один конденсатор и электрически управляемое устройство переключения, служащее для инициализации упомянутого конденсатора, включенного параллельно между выходом и реверсивным входом упомянутого операционного усилителя, причем упомянутый каскад интегратора готов к интегрированию упомянутой аналоговой величины, когда упомянутое устройство переключения разомкнуто;

каскад компаратора, содержащий единственный операционный усилитель, один вход которого соединен с выходом упомянутого каскада интегратора и другой вход соединен с опорной схемой, подающей опорное значение;

двоичный счетчик, соединенный с выходом упомянутого каскада компаратора и пригодный для определения первого числового значения, пропорционального упомянутой проинтегрированной аналоговой величине; однако упомянутый двоичный счетчик может быть смещенным и обычно для всех столбцов, позволяя выиграть в площади и потребляемой мощности;

цифроаналоговую схему обратной связи упомянутого счетчика, последовательно содержащую:

преобразователь, пригодный для преобразования упомянутого первого числового значения в аналоговый сигнал, подобный упомянутой оцифровываемой аналоговой величине,

средство для вычитания упомянутого аналогового сигнала из упомянутой оцифровываемой аналоговой величины,

и средство для усиления сигнала, образованного упомянутым вычитанием, с коэффициентом усиления, зависящим от числа битов упомянутого первого числового значения;

выход упомянутой реверсивной схемы обратной связи, соединенный со входом упомянутого каскада интегратора так, что последний производит второе числовое значение, пропорциональное, таким образом, усиленному аналоговому сигналу;

средство для сохранения первого и второго числовых значений, образованных двумя фазами преобразования;

средство для добавления упомянутого первого и второго числовых значений для формирования числа, отображающего упомянутую интегрируемую аналоговую величину.

Иначе говоря, аналого-цифровой преобразователь настоящего изобретения содержит единственный операционный усилитель-интегратор и единственный операционный усилитель-компаратор. Кроме того, он содержит аналого-цифровую схему с отрицательной обратной связью, служащую для изоляции в проинтегрированной аналоговой величине остаточных старших битов, для преобразования упомянутого значения в аналоговую величину, для вычитания ее из начального аналогового сигнала и затем для усиления упомянутого слабого сигнала, чтобы увеличить точность и воспроизводимость оцифровки.

На практике электронный компонент каскада интегратора представляет собой конденсатор. Такой компонент действительно подходит для успешного выполнения интегрирования аналоговой величины.

В соответствии с практической реализацией изобретения средство памяти может содержать блокирующуюся схему памяти, лучше известную в технике как "защелку", соединенную с выходом двоичного счетчика. Такая память имеет преимущество благодаря тому, что занимает небольшую область.

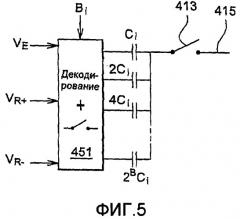

Обычно аналого-цифровая схема с отрицательной обратной связью содержит декодирующую систему и множество конденсаторов, установленных параллельно и индивидуально переключаемых с использованием переключателей, управляемых упомянутой декодирующей системой.

Такая схема с отрицательной обратной связью служит для выполнения этапов, приводящих ко второй фазе интегрирования, занимая при этом ограниченное пространство.

Кроме того, изобретение также относится к детектору электромагнитного излучения, в частности инфракрасного, содержащему матрицу смежно расположенных элементарных датчиков и устройство, как описано выше.

Предметом изобретения, таким образом, является укомплектованный детектор, пригодный для приема электромагнитного излучения и затем для его преобразования в цифровые сигналы.

Фактически матрица этого детектора может иметь единственную строку или единственный столбец.

Кроме того, элементарные датчики могут быть болометрами. Они предназначены для получения тепловых изображений объектов с использованием аппаратуры, работающей при комнатной температуре.

Краткое описание чертежей

Изобретение и его достоинства видны также из описания конкретных вариантов реализации, предоставляющих неограничивающие примеры, показанные на чертежах, из которых:

Фиг.1 схематически изображает график напряжение/время, показывающий способ преобразования предшествующего уровня техники. Этот чертеж уже рассматривался в связи с предшествующим уровнем техники;

Фиг.2 - схематическое представление аналого-цифрового устройства преобразования в соответствии с вариантом реализации предшествующего уровня техники. Этот чертеж уже рассматривался в связи с предшествующим уровнем техники;

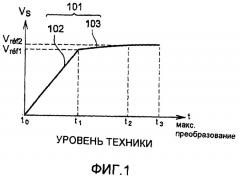

Фиг.3 - схематическое представление графика, иллюстрирующего вариант реализации способа, охватываемого настоящим изобретением;

Фиг.4 - схематическое представление устройства оцифровки в соответствии с вариантом реализации изобретения;

Фиг.5 - схематическое представление, показывающее особенности схемы с отрицательной обратной связью устройства оцифровки, показанного на Фиг.4.

Варианты реализации изобретения

На Фиг.3 показана временная диаграмма, иллюстрирующая интегрирование напряжения по времени. Ос