Дифференциальный операционный усилитель с малым напряжением питания

Иллюстрации

Показать всеИзобретение относится к области радиотехники и связи и может быть использовано в качестве устройства усиления аналоговых сигналов, в структуре аналоговых микросхем различного функционального назначения (например, ВЧ и СВЧ-усилителях и т.п.). Технический результат: повышение предельных значений коэффициента усиления по напряжению дифференциального усилителя (ДУ) при низковольтном питании. ДУ содержит входной дифференциальный каскад (ДК) (1) с первым (2) и вторым (3) токовыми выходами, буферный эмиттерный повторитель (ЭП) (4), вход которого соединен со вторым (3) токовым выходом входного ДК (1) и через первый (5) двухполюсник коллекторной нагрузки (ДКН) связан с шиной первого (6) источника питания (ИП), второй (7) ДКН, включенный между первым (2) токовым выходом входного ДК (1) и шиной первого (6) ИП, вторую (8) шину ИП, связанную с эмиттерными цепями входного ДК (1) и ЭП (4). В схему введен дополнительный согласующий транзистор (9), эмиттер которого соединен с первым (2) токовым выходом входного ДК (1), база соединена с выходом ЭП (4), а коллектор подключен ко входу дополнительного токового зеркала (ТЗ) (10), причем выход ТЗ (10) соединен со входом ЭП (4), а общий эмиттерный выход (11) ТЗ (10) связан с источником напряжения смещения потенциалов (11). 1 з.п. ф-лы, 9 ил.

Реферат

Изобретение относится к области радиотехники и связи и может быть использовано в качестве устройства усиления аналоговых сигналов, в структуре аналоговых микросхем различного функционального назначения (например, ВЧ и СВЧ-усилителях, фильтрах и т.п.).

В современной микроэлектронике находят применение классические дифференциальные операционные усилители (ДУ) с двумя резисторами в коллекторной цепи выходных транзисторов [1-17]. Данная архитектура является основой широкого класса IP-модулей систем связи и является базовой как для существующих, так и для принципиально новых технологий [10].

Наиболее близким по технической сущности к заявляемому устройству является входной дифференциальный ОУ в устройстве по патенту US 6285245, фиг.1.

Существенный недостаток известного ДУ, архитектура которого присутствует также во многих других усилительных каскадах [1-17], состоит в том, что при ограничениях на напряжение питания (Еп), характерных для SiGe технологических процессов (Еп≤2,0÷2,5 В), его коэффициент усиления по напряжению (Ку) получается небольшим (Кymax=10-20). В первую очередь это обусловлено ограничениями на сопротивления резисторов коллекторной нагрузки, которые из-за малых Еп не могут выбираться высокоомными.

Основная задача предлагаемого изобретения состоит в повышении предельных значений коэффициента усиления по напряжению ДУ при низковольтном питании.

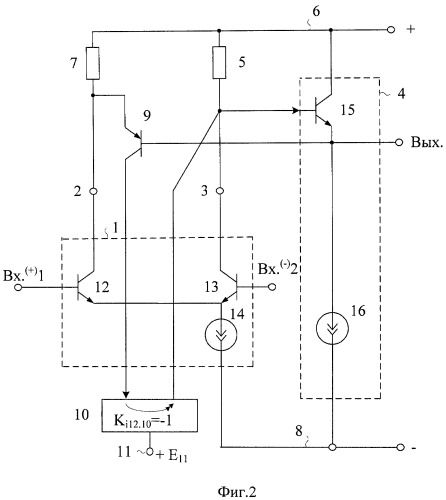

Поставленная задача решается тем, что в дифференциальном усилителе фиг.1, содержащем входной дифференциальный каскад 1 с первым 2 и вторым 3 токовыми выходами, буферный эмиттерный повторитель 4, вход которого соединен со вторым 3 токовым выходом входного дифференциального каскада 1 и через первый 5 двухполюсник коллекторной нагрузки связан с шиной первого 6 источника питания, второй 7 двухполюсник коллекторной нагрузки, включенный между первым 2 токовым выходом входного дифференциального каскада 1 и шиной первого 6 источника питания, вторую 8 шину источника питания, связанную с эмиттерными цепями входного дифференциального каскада 1 и буферного эмиттерного повторителя 4, предусмотрены новые элементы и связи - в схему введен дополнительный согласующий транзистор 9, эмиттер которого соединен с первым 2 токовым выходом входного дифференциального каскада 1, база соединена с выходом буферного эмиттерного повторителя 4, а коллектор подключен ко входу дополнительного токового зеркала 10, причем выход дополнительного токового зеркала 10 соединен со входом буферного эмиттерного повторителя 4, а общий эмиттерный выход 11 дополнительного токового зеркала 10 связан с источником напряжения смещения потенциалов 11.

На чертеже фиг.1 показана схема ДУ-прототипа.

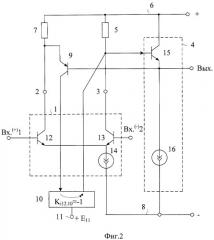

Схема заявляемого устройства, соответствующего п.1 формулы изобретения, показана на чертеже фиг.2.

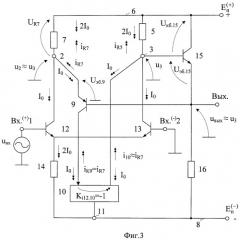

На чертеже фиг.3 показана схема заявляемого ДУ в соответствии с п.2 формулы изобретения.

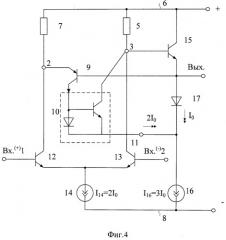

На чертеже фиг.4 приведен частный пример схемы ДУ фиг.2, в котором узел 11 связан с выходами ДУ.

На чертеже фиг.5 представлена схема ДУ-прототипа фиг.1 в среде компьютерного моделирования Cadence на моделях интегральных SiGe транзисторов, а на чертеже фиг.6 - заявляемого ДУ фиг.2 со 100% отрицательной обратной связью.

Графики фиг.7 характеризуют частотную зависимость коэффициента усиления по напряжению (Ку) сравниваемых ДУ фиг.5 и 6.

На чертеже фиг.8 приведен график зависимости коэффициента усиления по напряжению ДУ фиг.6 от неидентичности (абсолютной разности) сопротивлений резисторов 7 и 5 (двухполюсников коллекторной нагрузки 7 и 5).

График фиг.9 характеризует частотную зависимость максимально возможного Ку, который реализуется при разности сопротивлений двухполюсников коллекторной нагрузки 7 и 5 Rdiff=40 Ом.

Дифференциальный усилитель фиг.2 содержит входной дифференциальный каскад 1 с первым 2 и вторым 3 токовыми выходами, буферный эмиттерный повторитель 4, вход которого соединен со вторым 3 токовым выходом входного дифференциального каскада 1 и через первый 5 двухполюсник коллекторной нагрузки связан с шиной первого 6 источника питания, второй 7 двухполюсник коллекторной нагрузки, включенный между первым 2 токовым выходом входного дифференциального каскада 1 и шиной первого 6 источника питания, вторую 8 шину источника питания, связанную с эмиттерными цепями входного дифференциального каскада 1 и буферного эмиттерного повторителя 4. В схему введен дополнительный согласующий транзистор 9, эмиттер которого соединен с первым 2 токовым выходом входного дифференциального каскада 1, база соединена с выходом буферного эмиттерного повторителя 4, а коллектор подключен ко входу дополнительного токового зеркала 10, причем выход дополнительного токового зеркала 10 соединен со входом буферного эмиттерного повторителя 4, а общий эмиттерный выход 11 дополнительного токового зеркала 10 связан с источником напряжения смещения потенциалов 11. В частном случае (фиг.2), входной дифференциальный каскад 1 реализован на транзисторах 12, 13 и источнике тока 14, а буферный эмиттерный повторитель 4 содержит транзистор 15 и двухполюсник 16.

На чертеже фиг.3, в соответствии с п.2 формулы изобретения, в качестве источника напряжения смещения потенциалов 11 используется вторая 8 шина источника питания.

На чертеже фиг.4 в качестве цепи смещения потенциалов 11 используется выход буферного эмиттерного повторителя 4.

Рассмотрим работу ДУ фиг.1 и 3 на переменном токе.

Коэффициент усиления по напряжению ДУ фиг.1 без обратной связи определяется сопротивлением первого 5 двухполюсника коллекторной нагрузки:

где S1-2=(rэ12+rэ13)-1 - крутизна усиления входного дифференциального каскада 1, зависящая от сопротивлений эмиттерных переходов (rэ12, rэ13) входных транзисторов 12 и 13 входного дифференциального каскада 1.

Покажем аналитически, что более высокие значения Ку реализуются в схеме фиг.3.

Коэффициент усиления по напряжению ДУ фиг.3 можно найти по формуле

где Rэкв.3 - эквивалентное сопротивление в узле 3;

u3 - напряжение в узле 3;

- сопротивление эмиттерных переходов входных транзисторов 12, 13 входного дифференциального каскада 1 при эмиттерном токе Iэi=I0;

φT≈25 мВ - температурный потенциал.

Изменение u3 в узле 3 приводит к появлению токов iR5 через двухполюсник коллекторной нагрузки 5 и iR7 через двухполюсник 7:

,

где u2≈uвых≈u3 - напряжения в узле 2, на выходе ДУ и в узле 3. Последнее равенство объясняется единичной передачей по напряжению эмиттерных повторителей на транзисторах 15 и 9.

Приращение iR7 поступает через транзистор 9 на вход дополнительного токового зеркала 10, что создает ток i10 на его выходе:

где Ki12.10≈1, α9≈1 - коэффициенты передачи по току дополнительного токового зеркала 10 и тока эмиттера дополнительного согласующего транзистора 9.

Следовательно, эквивалентное приращение тока в узле 3 (iэкв.3) и эквивалентное сопротивление в узле 3:

Таким образом, коэффициент усиления по напряжению разомкнутого ДУ фиг.3:

Если выбрать R5=R7 и K i12.10 ≈0,99, то из (1) и (7) следует, что в предлагаемом ДУ коэффициент усиления Ку повышается в Nу-раз, где

Предельные значения Kymax в схеме фиг.3 определяются выходным сопротивлением дополнительного токового зеркала 10 и входным сопротивлением эмиттерного повторителя на транзисторе 15.

Графики фиг.7 получены в результате моделирования сравниваемых схем фиг.5, 6. Они показывают, что в заявляемом ДУ выигрыш по Ку (без обратной связи) достигает 36 дБ (т.е. почти два порядка).

Еще больший выигрыш по Ку реализуется при введении небольшой асимметрии сопротивлений резисторов R5 и R7 (фиг.8, 9).

Заявляемая схема особенно перспективна для использования в микроэлектронных СВЧ устройствах, реализуемых по техпроцессу SG25H2 и т.п.

БИБЛИОГРАФИЧЕСКИЙ СПИСОК

1. Патент США №3541464.

2. Патентная заявка WO 2004/102789.

3. Патент США №5389893.

4. Патент JP 53-142849.

5. A.с. CCCP 1102019.

6. Патентная заявка WO 2005/077525.

7. Патентная заявка США №2006/0181348.

8. Патентная заявка WO 2006/077525.

9. Патент GB 2419052.

10. Патентная заявка США №2008/0290941.

11. Патент WO 96/21271.

12. Патентная заявка США 2009/0108882, fig.3.

13. Патент JP 55030218.

14. Патент GB 1350352.

15. Патент JP 54-47467.

16. Патент JP 55099810.

11. Патент DE 2821942.

1. Дифференциальный операционный усилитель с малым напряжением питания, содержащий входной дифференциальный каскад (1) с первым (2) и вторым (3) токовыми выходами, буферный эмиттерный повторитель (4), вход которого соединен со вторым (3) токовым выходом входного дифференциального каскада (1) и через первый (5) двухполюсник коллекторной нагрузки связан с шиной первого (6) источника питания, второй (7) двухполюсник коллекторной нагрузки, включенный между первым (2) токовым выходом входного дифференциального каскада (1) и шиной первого (6) источника питания, вторую (8) шину источника питания, связанную с эмиттерными цепями входного дифференциального каскада (1) и буферного эмиттерного повторителя (4), отличающийся тем, что в схему введен дополнительный согласующий транзистор (9), эмиттер которого соединен с первым (2) токовым выходом входного дифференциального каскада (1), база соединена с выходом буферного эмиттерного повторителя (4), а коллектор подключен ко входу дополнительного токового зеркала (10), причем выход дополнительного токового зеркала (10) соединен со входом буферного эмиттерного повторителя (4), а общий эмиттерный выход (11) дополнительного токового зеркала (10) связан с источником напряжения смещения потенциалов (11).

2. Дифференциальный операционный усилитель с малым напряжением питания по п.1, отличающийся тем, что в качестве источника напряжения смещения потенциалов (11) используется вторая (8) шина источника питания.