Двоичный счетчик

Иллюстрации

Показать всеРеферат

243287

O ll H C A H H E

ИЗОБРЕТЕНИЯ боюв Советских

Социалистических

Республик

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

Зависимое от авт. свидетельства №

Заявлено 25.XII.1967 (№ 1205643/18-24) с присоединением заявки №

Приоритет

Опубликовано 05Х.1969. Бюллетень ¹ 16

Дата опубликования описания 23.IX.1969

Кл. 42m7, 1!10

21а>, 36/22

МПК G 06m

Н 03k

УДК 681.325(088.8) Комитет по .делай изобретений и открытий пои Совете Министров

СССР

Авторы изобретения

С. С. Клейменов, Г, Н. Кулаков и Н. 3. Семенюк

Заявитель

ДВОИЧНblЙ СЧЕТЧИК

Данное предложение относится к устройст вам счета импульсов,,применяемьгм в автоматике, телемеханике и вычислительной технике.

Известны двоичные счетчики, содержащие по два несимметричных триггера, один из которых выполняет функцию запоминания, а другой — счета. Недостатком известных схем является их недостаточное быстродействие.

Предложенный двоичный счетчик отличается тем, что он содержит дополнительный симметричный триггер, левое и правое плечи которого состоят каждое из последовательно соединенных усилителя и инвертора, причем выходы усилителей соединены с нулевыми входами, а выходы инверторов — с единичными входами соответственно счетных и запоминающих триггеров, входы правого и левого плеч дополнительного симметричного триггера соединены со входами положительных и отрицательных счетных импульсов. Это позволяет повысить быстродействие прибора.

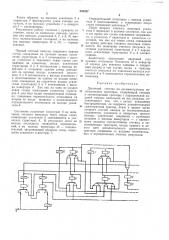

На чертеже приведена схема счетчика. Левое и правое плечи дополнительного симметричного триггера, предназначенного для формирования счетных импульсов, состоят каждое из последовательно соединенных усилителей 1 и 2 и инверторов 8 и 4. Левое плечо запускается непосредственно, правое — через инвертор б.

Выходы усилителей 1 и 2 соединейы с нулевыми входами, а выходы инверторов 8 и

4 — с единичными входами соответственно счетных триггеров б и 7 и запоминающих

5 триггеров 8 и 9.

Выходы триггеров 8 и 9 через инверторы 10 и 11 связаны со входами триггеров б и 7 и со схемой переноса, выполненной на последовательно соединенных усилителе 12 и инверто10 ре 18.

Последовательность счетных импульсов формируется следующим образом. Отрицательный импульс поступает на вход левой схемы совпадения усилителя 1 и на вход инвер15 тора б. Положительный импульс с выхода инвертора б поступает на правую схему совпадения усилителя 2, а отрицательный через усилитель 1 и инвертор 8 — на левую. В результате этого левая схема совпадения за20 крывается, и на выходе усилителя 2 появляется положительный, а на выходе инвертора

4 — отрицательный импульс.

По окончании счетного импульса левая схе25 ма совпадения усилителя 1 закрывается, но положительный и отрицательный потенциалы соответственно появляются на выходах усилителя 1 и инвертора 8 после возникновения на выходе инвертора 4 положительного потенЗ0 циала.

243287

Таким образом, на выходах усилителя 2 и инвертора 4 формируются узкие счетные импульсы, а на выходах усилителя l и инвертора 3 — расширенные.

Рассмотрим работу счетчика с нулевого состояния, когда на единичных выходах триггеров (на выходах усилителей б, 7, и 8, 9) имеется положительный потенциал, а на нулевых (на выходах инверторов 10 и 11) — отрицательный.

Первый счетный импульс закрывает правые схемы совпадения на нулевых входах усилителей (триггеров) б и 7 потенциалом с выхода усилителя 2, закрывает левые схемы совпадения на единичных входах усилителей (триггеров) 8 и 9 потенциалом с выхода инвертора 8, открывает правые схемы совпадения на нулевых входах усилителей (триггеров) 8 и 9 потенциалом с выхода усилителя 1 и подготавливает по одному из входов левых схем совпадения на единичных входах усилителей (триггеров) б и 7 потенциалом с выхода инвертора 4. Так как на один из входов левой схемы совпадения усилителя (триггера) б уже был подан отрицательный потенциал, появление отрицательного потенциала на втором ее входе приводит к возникновению отрицательного потенциала на выходе усилителя б.

Состояние усилителя (триггера) б по окончании счетного импульса через левую схему совпадения усилителя 8 запоминается в усилителе (триггере) 8. В результате этого на выходе последнего появляется отрицательный, а на выходе инвертора 10 — положительный, закрывающий среднюю схему совпадения усилителя (триггера) 7.

Отрицательный потенциал с выхода усилителя 8 подготавливает к открыванию левую схему совпадения усилителя 7.

После второго счетного импульса усилитель б переходит в нулевое состояние, так как в это время его схемы совпадения закрываются, а усилитель 7 переходит ia единичное состояние, так как его левая схема совпадения на время действия счетного импульса QTKpbI10 вается. По окончании счетного импульса состояния усилителей (триггеров) б и 7 передаются усилителям (триггерам) 8 и 9 соответственно.

Аналогично происходит двоичный счет

15 входных импульсов. Усилитель 12 и инвертор

18 служат для переноса единицы в следующий разряд в том случае, когда к приходу счетного импульса на единичных выходах усилителейй 8 и 9 оказываются отрицательные по20 тенциалы.

Предмет изобретения

Двоичный счетчик на несимметричных по25 тенциальных триггерах, содержащий счетные и запоминающие триггеры с параллельной подачей счетных импульсов на все разряды, отличпющийся тем, что, с целью повышения быстродействия, он содержит дополнительный

30 симметричный триггер, левое и правое плечи которого состоят каждое из последовательно соединенных усилителя и инвертора, причем выходы усилителей соединены с нулевыми входами, а выходы инверторов — с единич35 ными входами соответственно счетных и запоминающих триггеров, входы правого и левого плеч дополнительного симметричного триггера соединены со входами положительных и отрицательных счетных импульсов.