Прецизионный дифференциальный операционный усилитель

Иллюстрации

Показать всеИзобретение относится к области радиотехники и связи и может быть использовано в качестве устройства усиления аналоговых сигналов в структуре аналоговых микросхем различного функционального назначения (например, прецизионных операционных усилителях, стабилизаторах напряжения, компараторах). Технический результат: уменьшение Uсм и повышение Кос.п и Кос.сф. Прецизионный дифференциальный операционный усилитель содержит первый (1) и второй (2) входные транзисторы, эмиттеры которых соединены с выходом источника опорного тока (3), связанного также с первой (4) шиной источника питания, первый (5) вспомогательный транзистор, эмиттер которого через первый (6) вспомогательный резистор связан со второй (7) шиной источника питания, база - подключена к источнику напряжения смещения (8), а коллектор соединен с коллектором второго (2) входного транзистора, выходной (9) транзистор, база которого соединена с коллектором второго (2) входного транзистора, коллектор связан со второй (7) шиной источника питания, а эмиттер соединен с выходом устройства и через токостабилизирующий двухполюсник (10) связан с первой (4) шиной источника питания. Источник опорного тока (3) содержит первое (11) и второе (12) токовые зеркала, выходы которых объединены и являются выходом источника опорного тока (3), вход первого (11) токового зеркала соединен с коллектором первого (13) дополнительного транзистора, вход второго (12) токового зеркала соединен с коллектором второго (14) дополнительного транзистора, базы первого(13) и второго (14) дополнительных транзисторов соединены с базой первого (5) вспомогательного транзистора, а их эмиттеры через соответствующие первый (15) и второй (16) дополнительные резисторы подключены ко второй (7) шине источника питания. 2 з.п. ф-лы, 8 ил.

Реферат

Изобретение относится к области радиотехники и связи и может быть использовано в качестве устройства усиления аналоговых сигналов, в структуре аналоговых микросхем различного функционального назначения (например, прецизионных операционных усилителях, стабилизаторах напряжения, компараторах).

В современной микроэлектронике широко применяются двухкаскадные дифференциальные операционные усилители (ДУ) с несимметричным включением активной нагрузки во входном каскаде, при котором нагрузкой одного из входных транзисторов является транзисторный источник опорного тока, а нагрузка второго входного транзистора - отсутствует [1-8]. Такая архитектура имеет ряд преимуществ по динамическим параметрам в сравнении с ДУ на основе классических управляемых токовых зеркал. Однако существенный недостаток таких ДУ - повышенный уровень систематической составляющей напряжения смещения нуля (Ucм) из-за несимметрии архитектуры, а также невысокий коэффициент ослабления помехи по питанию (Кос.п) и коэффициент ослабления входных синфазных напряжений (Коc.сф).

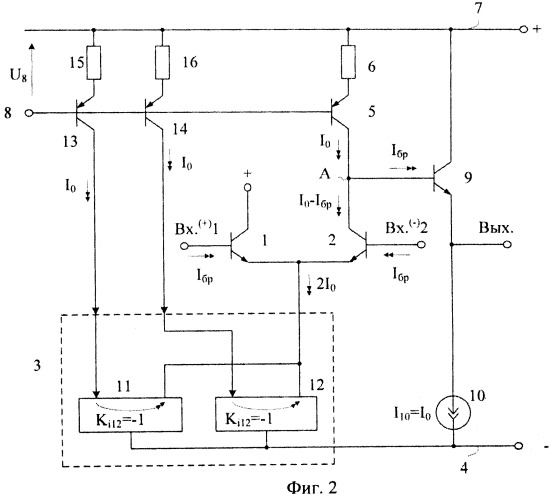

Ближайшим прототипом заявляемого устройства является ДУ по патенту США №6531920, fig.5. Он содержит первый 1 и второй 2 входные транзисторы, эмиттеры которых соединены с выходом источника опорного тока 3, связанного также с первой 4 шиной источника питания, первый 5 вспомогательный транзистор, эмиттер которого через первый 6 вспомогательный резистор связан со второй 7 шиной источника питания, база подключена к источнику напряжения смещения 8, а коллектор соединен с коллектором второго 2 входного транзистора, выходной 9 транзистор, база которого соединена с коллектором второго 2 входного транзистора, коллектор связан со второй 7 шиной источника питания, а эмиттер соединен с выходом устройства и через токостабилизирующий двухполюсник 10 связан с первой 4 шиной источника питания.

Существенный недостаток известного ДУ состоит в том, что он имеет повышенное значение систематической составляющей напряжения смещения нуля (Ucм), т.е. составляющей, зависящей от схемотехники ДУ, а также невысокие значения Кос.п и Кос.сф.

Основная задача предполагаемого изобретения состоит в уменьшении Ucм и повышении Кос.п и Кос.сф.

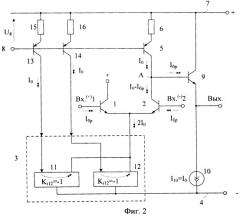

Поставленная задача решается тем, что в дифференциальном усилителе фиг.1, содержащем первый 1 и второй 2 входные транзисторы, эмиттеры которых соединены с выходом источника опорного тока 3, связанного также с первой 4 шиной источника питания, первый 5 вспомогательный транзистор, эмиттер которого через первый 6 вспомогательный резистор связан со второй 7 шиной источника питания, база подключена к источнику напряжения смещения 8, а коллектор соединен с коллектором второго 2 входного транзистора, выходной 9 транзистор, база которого соединена с коллектором второго 2 входного транзистора, коллектор связан со второй 7 шиной источника питания, а эмиттер соединен с выходом устройства и через токостабилизирующий двухполюсник 10 связан с первой 4 шиной источника питания, предусмотрены новые элементы и связи - источник опорного тока 3 содержит первое 11 и второе 12 токовые зеркала, выходы которых объединены и являются выходом источника опорного тока 3, вход первого 11 токового зеркала соединен с коллектором первого 13 дополнительного транзистора, вход второго 12 токового зеркала соединен с коллектором второго 14 дополнительного транзистора, базы первого 13 и второго 14 дополнительных транзисторов соединены с базой первого 5 вспомогательного транзистора, а их эмиттеры через соответствующие первый 15 и второй 16 дополнительные резисторы подключены ко второй 7 шине источника питания.

Схема усилителя-прототипа показана на чертеже фиг.1. На чертеже фиг.2 представлена схема заявляемого устройства в соответствии с п.1 формулы изобретения.

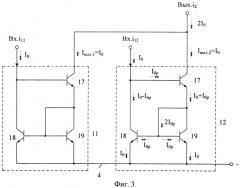

На чертеже фиг.3 приведена схема источника опорного тока 3 в заявляемом ДУ в соответствии с п.2 формулы изобретения.

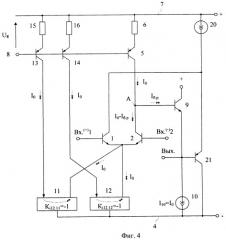

На чертеже фиг.4 приведена схема заявляемого ДУ в соответствии с п.2 формулы изобретения, а также специальном (по п.3 формулы изобретения) подключении коллектора первого 1 входного транзистора к эмиттеру согласующего транзистора 21.

На чертеже фиг.5 показана обобщенная схема ДУ-прототипа (прототип №1) в среде компьютерного моделирования PSpice на моделях интегральных транзисторов ФГУП НПП «Пульсар», а на чертеже фиг.6 - модифицированного ДУ-прототипа по патенту США №6531920, fig.5.

На чертеже фиг.7 показана схема заявляемого устройства фиг.2 в среде компьютерного моделирования PSpice на моделях интегральных транзисторов ФГУП НПП «Пульсар».

На чертеже фиг.8 приведены температурные зависимости напряжения смещения нуля Ucм трех сравниваемых схем ДУ фиг.7, фиг.6 и фиг.5.

Прецизионный дифференциальный операционный усилитель фиг.2 содержит первый 1 и второй 2 входные транзисторы, эмиттеры которых соединены с выходом источника опорного тока 3, связанного также с первой 4 шиной источника питания, первый 5 вспомогательный транзистор, эмиттер которого через первый 6 вспомогательный резистор связан со второй 7 шиной источника питания, база подключена к источнику напряжения смещения 8, а коллектор соединен с коллектором второго 2 входного транзистора, выходной 9 транзистор, база которого соединена с коллектором второго 2 входного транзистора, коллектор связан со второй 7 шиной источника питания, а эмиттер соединен с выходом устройства и через токостабилизирующий двухполюсник 10 связан с первой 4 шиной источника питания. Источник опорного тока 3 содержит первое 11 и второе 12 токовые зеркала, выходы которых объединены и являются выходом источника опорного тока 3, вход первого 11 токового зеркала соединен с коллектором первого 13 дополнительного транзистора, вход второго 12 токового зеркала соединен с коллектором второго 14 дополнительного транзистора, базы первого 13 и второго 14 дополнительных транзисторов соединены с базой первого 5 вспомогательного транзистора, а их эмиттеры через соответствующие первый 15 и второй 16 дополнительные резисторы подключены ко второй 7 шине источника питания.

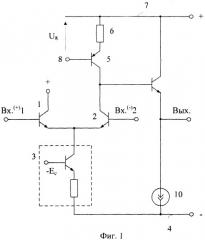

На чертеже фиг.3, в соответствии с п.2 формулы изобретения, каждое первое 11 и второе 12 токовые зеркала идентичны и содержат выходной транзистор 17, коллектор которого является выходом токового зеркала, а база - его входом, входной транзистор 18, коллектор которого соединен с базой выходного транзистора 17, эмиттер связан с первой 4 шиной источника питания, а база подключена к эмиттеру выходного транзистора 17 и через дополнительный p-n переход 19 соединена с первой 4 шиной источника питания.

Кроме этого на чертеже фиг.4 в соответствии с п.3 формулы изобретения, коллектор первого 1 входного транзистора связан со второй 7 шиной источника питания через источник опорного тока 20 и соединен с эмиттером согласующего транзистора 21, база которого подключена к эмиттеру выходного транзистора 9, а коллектор соединен с первой 4 шиной источника питания.

Рассмотрим работу ДУ фиг.2.

Статический режим прецизионного ОУ фиг.2 устанавливается напряжением источника смещения U8 и резисторами 15, 16, 6, которые должны быть идентичны. Поэтому коллекторные токи транзисторов 13, 14, 5 одинаковы и равны величине I0 (например, 0,5 мА или 1 мА).

В качестве идентичных токовых зеркал 11 и 12 рекомендуется использовать хорошо известные схемы Вильсона (фиг.3), которые обладают высокой точностью передачи входного тока на выход (Ki12=-1), а также предельными значениями выходного сопротивления (Rвых), близкого к сопротивлению закрытого коллекторного перехода применяемых транзисторов.

Авторам пока не известны другие варианты построения токовых зеркал 11 и 12, обладающих данной совокупностью параметров. Простейшие токовые зеркала имеют либо низкое выходное сопротивление Rвых=20·30 кОм, либо большую погрешность передачи входного тока на его выход, либо первый и второй недостаток одновременно. Однако дальнейшее развитие микросхемотехники позволит, в принципе, применять и другие новые токовые зеркала в качестве функциональных узлов 11 и 12.

При рассматриваемых допущениях коллекторные и базовые токи транзисторов схемы фиг.2 принимают следующие значения:

где Iбi - ток базы i-ro транзистора;

β - коэффициент усиления по току базы n-p-n транзисторов схемы при Iэ=I0.

Как следствие, в узле «А» происходит полная взаимная компенсация всех токов, сходящихся в этом узле при uвх=0

Как следствие, систематическая составляющая напряжения смещения нуля Ucм ДУ фиг.2 близка к нулю.

Данные выводы подтверждаются результатами компьютерного моделирования фиг.8 ДУ фиг.5, фиг.6 и фиг.7 - предлагаемая схема фиг.7 имеет систематическую составляющую Uсм≈0,8 мкВ и малый температурный дрейф Uсм в то время как известные устройства фиг.5 и фиг.6 характеризуются повышенными уровнями Uсм=3,8÷4,8 мВ.

При изменении напряжения питания токи коллекторов транзисторов 5, 14, 13, 2 изменяются одинаково на величину iп и, следовательно, в узле «А» происходит взаимная компенсация равных приращений iк5=iп и iк2=iп.Это является необходимым условием повышения коэффициента ослабления помехи по питанию ДУ фиг.2.

Увеличение коэффициента ослабления входных синфазных напряжений ДУ фиг.2 обеспечивается применением токовых зеркал фиг.3, которые имеют повышенное сопротивление.

В схеме ДУ фиг.4 по п.3 формулы изобретения реализуются предельные значения коэффициента усиления по напряжению в режиме повторителя сигналов.

Таким образом, заявляемое устройство имеет существенные преимущества по сравнению с прототипом.

БИБЛИОГРАФИЧЕСКИЙ СПИСОК

1. Патент США №6531920.

2. Патентная заявка SU №2007/0152753, fig.5c.

3. Патент США №6396346.

4. Патентная заявка SU №2008/0129384, fig.5.

5. Патент Японии JP 51-112253.

6. Патент США №5075636, fig.1.

7. Патент СА 02072436, fig.2.

8. Патент США №5262688, fig.3.

1. Прецизионный дифференциальный операционный усилитель, содержащий первый (1) и второй (2) входные транзисторы, эмиттеры которых соединены с выходом источника опорного тока (3), связанного также с первой (4) шиной источника питания, первый (5) вспомогательный транзистор, эмиттер которого через первый (6) вспомогательный резистор связан со второй (7) шиной источника питания, база подключена к источнику напряжения смещения (8), а коллектор соединен с коллектором второго (2) входного транзистора, выходной (9) транзистор, база которого соединена с коллектором второго (2) входного транзистора, коллектор связан со второй (7) шиной источника питания, а эмиттер соединен с выходом устройства и через токостабилизирующий двухполюсник (10) связан с первой (4) шиной источника питания, отличающийся тем, что источник опорного тока (3) содержит первое (11) и второе (12) токовые зеркала, выходы которых объединены и являются выходом источника опорного тока (3), вход первого (11) токового зеркала соединен с коллектором первого (13) дополнительного транзистора, вход второго (12) токового зеркала соединен с коллектором второго (14) дополнительного транзистора, базы первого (13) и второго (14) дополнительных транзисторов соединены с базой первого (5) вспомогательного транзистора, а их эмиттеры через соответствующие первый (15) и второй (16) дополнительные резисторы подключены ко второй (7) шине источника питания.

2. Прецизионный дифференциальный операционный усилитель по п.1, отличающийся тем, что каждое первое (11) и второе (12) токовые зеркала идентичны и содержат выходной транзистор (17), коллектор которого является выходом токового зеркала, а база - его входом, входной транзистор (18), коллектор которого соединен с базой выходного транзистора (17), эмиттер связан с первой (4) шиной источника питания, а база подключена к эмиттеру выходного транзистора (17) и через дополнительный р-n переход (19) соединена с первой (4) шиной источника питания.

3. Прецизионный дифференциальный операционный усилитель по п.1, отличающийся тем, что коллектор первого (1) входного транзистора связан со второй (7) шиной источника питания через источник опорного тока (20) и соединен с эмиттером согласующего транзистора (21), база которого подключена к эмиттеру выходного транзистора (9), а коллектор соединен с первой (4) шиной источника питания.