Дифференциальный операционный усилитель с парафазным выходом

Иллюстрации

Показать всеИзобретение относится к области радиотехники и связи и может быть использовано в качестве устройства усиления аналоговых сигналов в структуре аналоговых микросхем различного функционального назначения (например, решающих усилителях (ОУ), компараторах и т.п.). Технический результат - создание условий, при которых выходное статическое синфазное напряжение дифференциального усилителя (ДУ) будет иметь высокую стабильность и нулевое значение. ДУ содержит первый (1) и второй (2) входные транзисторы (Т), базы которых соединены со входами (3) и (4) устройства, первый (5) токостабилизирующий двухполюсник, включенный между объединенным эмиттером первого (1) и второго (2) входных Т и шиной первого (6) источника питания (ИП), первый (7) и второй (8) выходные Т, коллекторы которых соединены с шиной второго (9) ИП, эмиттеры связаны с соответствующими парафазными выходами (10), (11) устройства и связаны друг с другом через два последовательно соединенных первого (12) и второго (13) резисторов цепи обратной связи, первый (14) двухполюсник коллекторной нагрузки, включенный между базой первого (7) выходного Т и шиной второго (9) ИП, второй (15) двухполюсник коллекторной нагрузки, включенный между базой второго (8) выходного Т и шиной второго (9) ИП. В схему введены первый (16), второй (17) и третий (18) дополнительные Т, объединенные эмиттеры которых через первый (19) вспомогательный двухполюсник соединены с шиной первого (6) ИП, база первого (16) дополнительного Т связана с источником напряжения смещения потенциалов (20), объединенные базы второго (17) и третьего (18) дополнительных Т соединены с общим узлом последовательно соединенных первого (12) и второго (13) резисторов обратной связи, коллектор второго (17) дополнительного Т соединен с базой первого (7) выходного Т, коллектор третьего (18) дополнительного Т соединен с базой второго (8) выходного Т, причем эмиттеры первого (7) и второго (8) выходных Т связаны с шиной первого (6) ИП через соответствующие первый (21) и второй (22) вспомогательные двухполюсники. 2 з.п. ф-лы, 6 ил.

Реферат

Изобретение относится к области радиотехники и связи и может быть использовано в качестве устройства усиления аналоговых сигналов в структуре аналоговых микросхем различного функционального назначения (например, решающих усилителях (ОУ), компараторах и т.п.).

Известны схемы классических дифференциальных усилителей (ДУ) [1-14] с отрицательной обратной связью по синфазному сигналу, которые стали основой многих серийных аналоговых микросхем первого и второго поколения.

В последние годы ДУ данного класса стали снова активно применяться в структуре СВЧ-устройств [1, 2, 3], реализованных на базе новейших SiGe-технологий. Это связано с возможностью построения на их основе активных RC-фильтров гигагерцового диапазона для современных и перспективных систем связи. В значительной степени этому способствует простота установления статического режима ДУ при низковольтном питании (1,2÷2,1)В, которое характерно для SiGe транзисторов с предельными частотами 20÷60 ГГц.

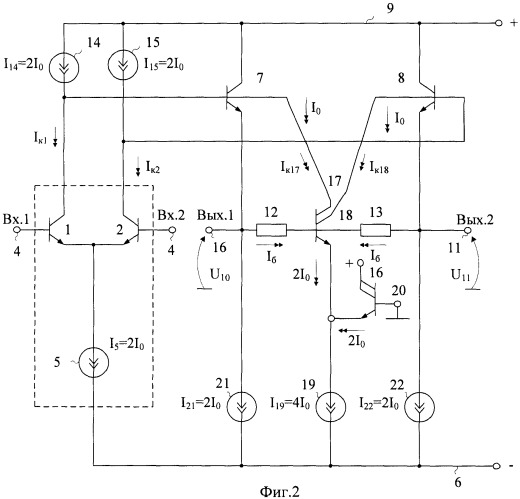

Ближайшим прототипом (фиг.1) заявляемого устройства является дифференциальный усилитель, описанный в патенте RU 2346382, содержащий первый 1 и второй 2 входные транзисторы, базы которых соединены со входами 3 и 4 устройства, первый 5 токостабилизирующий двухполюсник, включенный между объединенным эмиттером первого 1 и второго 2 входных транзисторов и шиной первого 6 источника питания, первый 7 и второй 8 выходные транзисторы, коллекторы которых соединены с шиной второго 9 источника питания, эмиттеры связаны с соответствующими парафазными выходами (10), (11) устройства и связаны друг с другом через два последовательно соединенных первый 12 и второй 13 резисторы цепи обратной связи, первый 14 двухполюсник коллекторной нагрузки, включенный между базой первого 7 выходного транзистора и шиной второго 9 источника питания, второй 15 двухполюсник коллекторной нагрузки, включенный между базой второго 8 выходного транзистора и шиной второго 9 источника питания.

Основная цель предлагаемого изобретения состоит в создании условий, при которых выходное статическое синфазное напряжение ДУ будет иметь высокую стабильность и нулевое значение.

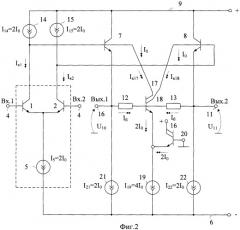

Поставленная задача решается тем, что в дифференциальном операционном усилителе с парафазным выходом, фиг.1, содержащем первый 1 и второй 2 входные транзисторы, базы которых соединены со входами 3 и 4 устройства, первый 5 токостабилизирующий двухполюсник, включенный между объединенным эмиттером первого 1 и второго 2 входных транзисторов и шиной первого 6 источника питания, первый 7 и второй 8 выходные транзисторы, коллекторы которых соединены с шиной второго 9 источника питания, эмиттеры связаны с соответствующими парафазными выходами (10), (11) устройства и связаны друг с другом через два последовательно соединенных первый 12 и второй 13 резисторы цепи обратной связи, первый 14 двухполюсник коллекторной нагрузки, включенный между базой первого 7 выходного транзистора и шиной второго 9 источника питания, второй 15 двухполюсник коллекторной нагрузки, включенный между базой второго 8 выходного транзистора и шиной второго 9 источника питания, предусмотрены новые элементы и связи - в схему введены первый 16, второй 17 и третий 18 дополнительные транзисторы, объединенные эмиттеры которых через первый 19 вспомогательный двухполюсник соединены с шиной первого 6 источника питания, база первого 16 дополнительного транзистора связана с источником напряжения смещения потенциалов 20, объединенные базы второго 17 и третьего 18 дополнительных транзисторов соединены с общим узлом последовательно соединенных первого 12 и второго 13 резисторов обратной связи, коллектор второго 17 дополнительного транзистора соединен с базой первого 7 выходного транзистора, коллектор третьего 18 дополнительного транзистора соединен с базой второго 8 выходного транзистора, причем эмиттеры первого 7 и второго 8 выходных транзисторов связаны с шиной первого 6 источника питания через соответствующие первый 21 и второй 22 вспомогательные двухполюсники.

На фиг.1 показана схема ДУ-прототипа.

На фиг.2 показана схема заявляемого устройства в соответствии с п.1, п.2 и п.3 формулы изобретения.

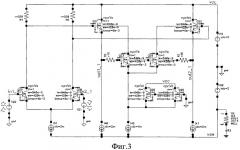

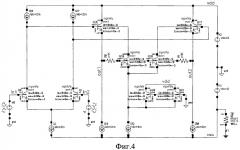

На фиг.3 и фиг.4 - показаны схемы заявляемого ДУ (фиг.2) в среде компьютерного моделирования Cadance на моделях SiGe интегральных транзисторов при резистивных (фиг.3) двухполюсниках коллекторной нагрузки (14, 15), а также при их выполнении в виде источников опорного тока (фиг.4).

На фиг.5 приведены частотные зависимости коэффициента усиления по напряжению схем фиг.3 и фиг.4.

Фиг.6 характеризует уровень максимального неискаженного выходного сигнала с выходов out1 и out2 при R12=R13=R=1 кОм при резистивной коллекторной нагрузке.

Дифференциальный операционный усилитель с парафазным выходом, фиг.2, содержит первый 1 и второй 2 входные транзисторы, базы которых соединены со входами 3 и 4 устройства, первый 5 токостабилизирующий двухполюсник, включенный между объединенным эмиттером первого 1 и второго 2 входных транзисторов и шиной первого 6 источника питания, первый 7 и второй 8 выходные транзисторы, коллекторы которых соединены с шиной второго 9 источника питания, эмиттеры связаны с соответствующими парафазными выходами (10), (11) устройства и связаны друг с другом через два последовательно соединенных первый 12 и второй 13 резистора цепи обратной связи, первый 14 двухполюсник коллекторной нагрузки, включенный между базой первого 7 выходного транзистора и шиной второго 9 источника питания, второй 15 двухполюсник коллекторной нагрузки, включенный между базой второго 8 выходного транзистора и шиной второго 9 источника питания. В схему введены первый 16, второй 17 и третий 18 дополнительные транзисторы, объединенные эмиттеры которых через первый 19 вспомогательный двухполюсник соединены с шиной первого 6 источника питания, база первого 16 дополнительного транзистора связана с источником напряжения смещения потенциалов 20, объединенные базы второго 17 и третьего 18 дополнительных транзисторов соединены с общим узлом последовательно соединенных первого 12 и второго 13 резисторов обратной связи, коллектор второго 17 дополнительного транзистора соединен с базой первого 7 выходного транзистора, коллектор третьего 18 дополнительного транзистора соединен с базой второю 8 выходного транзистора, причем эмиттеры первого 7 и второго 8 выходных транзисторов связаны с шиной первого 6 источника питания через соответствующие первый 21 и второй 22 вспомогательные двухполюсники.

На фиг.2 в соответствии с п.2 формулы изобретения в качестве источника напряжения смещения потенциала 20 используется общая шина первого 6 и второго 9 источников питания.

Кроме того, на фиг.3 в соответствии с п.3 формулы изобретения первый 16 дополнительный транзистор имеет площадь эмиттерного p-n перехода, приблизительно, в два раза больше, чем у второго 17 и третьего 18 дополнительных транзисторов.

Рассмотрим работу ДУ фиг.2.

Статический режим по току транзисторов предлагаемого ДУ устанавливается двухполюсниками 5, 14, 15, 19, 21 и 22:

I14=Iк1+Iк17, I15=Iк2+Iк18

Iк17=Iк18+Iк16=I19

В соответствии со вторым законом Киргофа статические напряжения на выходах 10 и 11 ДУ:

где Uэб.17=Uэб.16 - напряжения «эмиттер-база» транзисторов 17 и 16;

E20 - напряжение источника смещения потенциалов 20;

Iб=0,5Iб17-18 - половина суммарного тока базы транзисторов 17 и 18. Если выбрать Е20=0, R12=R13, тo:

С учетом типовых численных значений Iб и R12 практических схем ДУ из уравнения (3) можно сделать вывод о том, что в заявляемом ДУ статические выходные напряжения U10=U11 близки к единицам милливольт.

Дальнейшее уменьшение U10=U11 возможно за счет рационального выбора внутреннего сопротивления (R20) источника напряжения смещения потенциалов 20. Если в схеме фиг.2 обеспечить R20=R12=R13 за счет включения в базовую цепь транзистора 16 резистора R20=R12=R13, то теоретическое значение U10=U11 с высокой точностью будет соответствовать нулевому уровню.

В зависимости от величины напряжения смещения потенциалов (20) в ДУ фиг.2 можно установить и другие заданные величины статического выходного синфазного напряжения.

Графики фиг.6 показывают, что в схемах ДУ фиг.2 с резистивной (фиг.3) и активной (фиг.4) коллекторной нагрузкой диапазон изменения uвых при низковольтном питании (±2В) лежит в пределах ±1В. При этом коэффициент усиления по напряжению ДУ с резистивной нагрузкой более 20 дБ (фиг.5), а при активной нагрузки более 60 дБ (фиг.5).

При реализации ДУ фиг.2 в соответствии с п.3 формулы изобретения создаются дополнительные условия, способствующие уменьшению U10=U11≈0.

Таким образом, заявляемый дифференциальный операционный усилитель имеет малый нулевой уровень выходного синфазного напряжения. Это весьма существенно для его согласования с последующими функциональными узлами системы на кристалле, а также для получения боле широкого диапазона изменения выходных противофазных напряжений.

БИБЛИОГРАФИЧЕСКИЙ СПИСОК

1. Budyakov, A. Design of Fully Differential OpAmps for GHz Range Applications [Текст] / Budyakov A., Schmaiz K., Prokopenko N., Scheytt C., Ostrovskyy P. // Проблемы современной аналоговой микросхемотехники: Сб. материалов VI Международного научно-практического семинара. В 3-х ч. Ч.1. Функциональные узлы аналоговых интегральных схем и сложных функциональных блоков / Под ред. Н.Н.Прокопенко. - Шахты: Изд-во ЮРГУЭС, 2007 - С.106-110.

2. S.P.Voinigescu, et al., "Design Methodology and Applications of SiGe BiCMOS Cascode Opamps with up to 37-GHz Unity Gain Bandwidth," IEEE CS1CS, Techn. Digest, pp.283-286, Nov.2005, фиг.2.

3. S.P.Voinigescu, et al., "SiGe BiCMOS for Analog, High-Speed Digital and Millimetre-Wave Applications Beyond 50 GHz," IEEE BCTM, pp.1-8, Oct. 2006.

4. Патент США №4274394, фиг.2.

5. Патент США №3619797.

6. Патент США №3622902.

7. Патент США №3440554.

8. Авт.св. СССР №299013.

9. Патент Англии №1175329, Н3Т.

10. Патент США №3304512.

11. Патент США №437193.

12. Авт.св. СССР №421105.

13. Авт.св. СССР №764100.

14. Авт.св. СССР №669471.

1. Дифференциальный операционный усилитель с парафазным выходом, содержащий первый (1) и второй (2) входные транзисторы, базы которых соединены со входами (3) и (4) устройства, первый (5) токостабилизирующий двухполюсник, включенный между объединенным эмиттером первого (1) и второго (2) входных транзисторов и шиной первого (6) источника питания, первый (7) и второй (8) выходные транзисторы, коллекторы которых соединены с шиной второго (9) источника питания, эмиттеры связаны с соответствующими парафазными выходами (10), (11) устройства и связаны друг с другом через два последовательно соединенных первого (12) и второго (13) резистора цепи обратной связи, первый (14) двухполюсник коллекторной нагрузки, включенный между базой первого (7) выходного транзистора и шиной второго (9) источника питания, второй (15) двухполюсник коллекторной нагрузки, включенный между базой второго (8) выходного транзистора и шиной второго (9) источника питания, отличающийся тем, что в схему введены первый (16), второй (17) и третий (18) дополнительные транзисторы, объединенные эмиттеры которых через первый (19) вспомогательный двухполюсник соединены с шиной первого (6) источника питания, база первого (16) дополнительного транзистора связана с источником напряжения смещения потенциалов (20), объединенные базы второго (17) и третьего (18) дополнительных транзисторов соединены с общим узлом последовательно соединенных первого (12) и второго (13) резисторов обратной связи, коллектор второго (17) дополнительного транзистора соединен с базой первого (7) выходного транзистора, коллектор третьего (18) дополнительного транзистора соединен с базой второго (8) выходного транзистора, причем эмиттеры первого (7) и второго (8) выходных транзисторов связаны с шиной первого (6) источника питания через соответствующие первый (21) и второй (22) вспомогательные двухполюсники.

2. Дифференциальный операционный усилитель по п.1, отличающийся тем, что в качестве источника напряжения смещения потенциала (20) используется общая шина первого (6) и второго (9) источников питания.

3. Дифференциальный операционный усилитель по п.1, отличающийся тем, что первый (16) дополнительный транзистор имеет площадь эмиттерного p-n перехода, приблизительно, в два раза больше, чем у второго (17) и третьего (18) дополнительных транзисторов.