Дифференциальный операционный усилитель с парафазным выходом

Иллюстрации

Показать всеИзобретение относится к области радиотехники и связи и может быть использовано в качестве устройства усиления аналоговых сигналов, в структуре аналоговых микросхем различного функционального назначения (например, решающих усилителях (ОУ), компараторах, мостовых усилителях мощности и т.п.). Технический результат - создание условий, при которых выходное статическое синфазное напряжение ДУ будет иметь высокую стабильность и нулевое значение. Дифференциальный операционный усилитель с парафазным выходом содержит входной дифференциальный каскад (1) с первым (2) и вторым (3) токовыми выходами, первым (4) и вторым (5) входами, первой (6) шиной источника питания, связанной с общей эмиттерной цепью входного дифференциального каскада (1), первый (7) выходной транзистор, база которого соединена со вторым (3) токовым выходом входного дифференциального каскада (1), коллектор подключен к шине второго (8) источника питания, а эмиттер связан с первым (9) вспомогательным выходом устройства и через первый (10) токостабилизирующий двухполюсник соединен с первой (6) шиной источника питания, второй (11) выходной транзистор, база которого соединена с первым (2) токовым выходом входного дифференциального каскада (1), коллектор подключен к шине второго (8) источника питания, а эмиттер связан со вторым (12) вспомогательным выходом устройства и через второй (13) токостабилизирующий двухполюсник соединен с первой (6) шиной источника питания, третий (14) и четвертый (15) выходные транзисторы, эмиттеры которых соединены со второй (8) шиной источника питания, базы связаны друг с другом, коллектор третьего (14) выходного транзистора подключен к базе второго (11) выходного транзистора, коллектор четвертого (15) выходного транзистора подключен к базе первого (7) выходного транзистора. В схему введены первый (16), второй (17) и третий (18) дополнительные транзисторы, эмиттеры которых соединены друг с другом и через третий (19) токостабилизирующий двухполюсник связаны с первой (6) шиной источника питания, коллекторы первого (16) и второго (17) дополнительных транзисторов объединены и связаны с базами третьего (14) и четвертого (15) выходных транзисторов, база первого (16) дополнительного транзистора соединена с первым (4) входом устройства, база второго (17) дополнительного транзистора соединена со вторым (5) входом устройства, коллектор третьего (18) дополнительного транзистора связан со второй (8) шиной источника питания, причем первый (9) вспомогательный выход устройства соединен с базой третьего (18) дополнительного транзистора через первый (20) резистор обратной связи, а второй (12) вспомогательный выход устройства соединен с базой третьего (18) дополнительного транзистора через второй (21) резистор обратной связи. 2 з.п. ф-лы, 12 ил.

Реферат

Изобретение относится к области радиотехники и связи и может быть использовано в качестве устройства усиления аналоговых сигналов, в структуре аналоговых микросхем различного функционального назначения (например, решающих усилителях (ОУ), компараторах, мостовых усилителях мощности и т.п.).

Известны схемы классических двухкаскадных дифференциальных усилителей (ДУ) с парафазным выходом, которые стали основой многих серийных аналоговых микросхем [1-8].

Кроме того, ДУ данного класса активно применяются в структуре СВЧ-устройств, реализованных на базе новейших SiGe-технологий. Это связано с возможностью построения на их основе активных RC-фильтров гигагерцового диапазона для современных и перспективных систем связи, мостовых усилителей мощности и т.п.

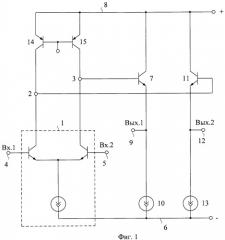

Ближайшим прототипом (фиг.1) заявляемого устройства является дифференциальный усилитель, представленный в статье Будякова А.С., Прокопенко Н.Н., Манжулы В.Г. Анализ частотных характеристик подсхем входных каскадов СВЧ операционных усилителей для сложных функциональных блоков радиационностойкой аппаратуры нового поколения// в журнале «Научно-технические ведомости СПбГПУ. Информатика, Телекоммуникации. Управление». - №3 (101)/2010. - с.210, рис.4 и содержащий входной дифференциальный каскад 1 с первым 2 и вторым 3 токовыми выходами, первым 4 и вторым 5 входами, первой 6 шиной источника питания, связанной с общей эмиттерной цепью входного дифференциального каскада 1, первый 7 выходной транзистор, база которого соединена со вторым 3 токовым выходом входного дифференциального каскада 1, коллектор подключен к шине второго 8 источника питания, а эмиттер связан с первым 9 вспомогательным выходом устройства и через первый 10 токостабилизирующий двухполюсник соединен с первой 6 шиной источника питания, второй 11 выходной транзистор, база которого соединена с первым 2 токовым выходом входного дифференциального каскада 1, коллектор подключен к шине второго 8 источника питания, а эмиттер связан со вторым 12 вспомогательным выходом устройства и через второй 13 токостабилизирующий двухполюсник соединен с первой 6 шиной источника питания, третий 14 и четвертый 15 выходные транзисторы, эмиттеры которых соединены со второй 8 шиной источника питания, базы связаны друг с другом, коллектор третьего 14 выходного транзистора подключен к базе второго 11 выходного транзистора, коллектор четвертого 15 выходного транзистора подключен к базе первого 7 выходного транзистора.

Существенный недостаток известного ДУ состоит в том, что он имеет нестабильный уровень выходного синфазного напряжения, зависящий от параметров входного дифференциального каскада 1 и напряжений источников питания. Это значительно затрудняет его согласование с последующими функциональными узлами СФ-блоков систем на кристалле A/d и D/a классов.

Основная задача предлагаемого изобретения состоит в создании условий, при которых выходное статическое синфазное напряжение ДУ будет иметь высокую стабильность и нулевое значение.

Поставленная задача решается тем, что в дифференциальном операционном усилителе с парафазным выходом фиг.1, содержащем входной дифференциальный каскад 1 с первым 2 и вторым 3 токовыми выходами, первым 4 и вторым 5 входами, первой 6 шиной источника питания, связанной с общей эмиттерной цепью входного дифференциального каскада 1, первый 7 выходной транзистор, база которого соединена со вторым 3 токовым выходом входного дифференциального каскада 1, коллектор подключен к шине второго 8 источника питания, а эмиттер связан с первым 9 вспомогательным выходом устройства и через первый 10 токостабилизирующий двухполюсник соединен с первой 6 шиной источника питания, второй 11 выходной транзистор, база которого соединена с первым 2 токовым выходом входного дифференциального каскада 1, коллектор подключен к шине второго 8 источника питания, а эмиттер связан со вторым 12 вспомогательным выходом устройства и через второй 13 токостабилизирующий двухполюсник соединен с первой 6 шиной источника питания, третий 14 и четвертый 15 выходные транзисторы, эмиттеры которых соединены со второй 8 шиной источника питания, базы связаны друг с другом, коллектор третьего 14 выходного транзистора подключен к базе второго 11 выходного транзистора, коллектор четвертого 15 выходного транзистора подключен к базе первого 7 выходного транзистора, предусмотрены новые элементы и связи - в схему введены первый 16, второй 17 и третий 18 дополнительные транзисторы, эмиттеры которых соединены друг с другом и через третий 19 токостабилизирующий двухполюсник связаны с первой 6 шиной источника питания, коллекторы первого 16 и второго 17 дополнительных транзисторов объединены и связаны с базами третьего 14 и четвертого 15 выходных транзисторов, база первого 16 дополнительного транзистора соединена с первым 4 входом устройства, база второго 17 дополнительного транзистора соединена со вторым 5 входом устройства, коллектор третьего 18 дополнительного транзистора связан со второй 8 шиной источника питания, причем первый 9 вспомогательный выход устройства соединен с базой третьего 18 дополнительного транзистора через первый 20 резистор обратной связи, а второй 12 вспомогательный выход устройства соединен с базой третьего 18 дополнительного транзистора через второй 21 резистор обратной связи.

На фиг.1 показана схема ДУ-прототипа.

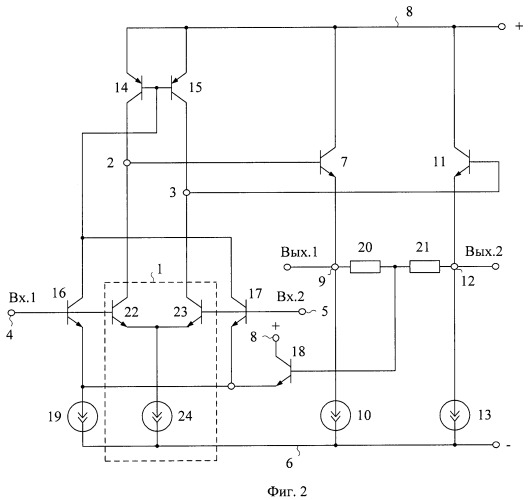

На фиг.2 показана схема заявляемого устройства в соответствии с п.1 формулы изобретения.

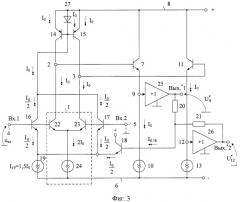

На фиг.3 показана схема ДУ по п.2 и п.3 формулы изобретения.

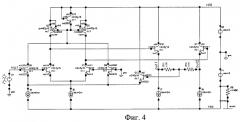

На фиг.4 приведена схема заявляемого ДУ фиг.3 в среде компьютерного моделирования Cadance на моделях SiGe интегральных транзисторов.

Графики фиг.5 показывают зависимость постоянной составляющей выходного синфазного статического напряжения ДУ фиг.4 от тока третьего 19 токостабилизирующего двухполюсника (I19=Ivar) при сопротивлениях резисторов обратной связи 20 и 21 R20=R21=1 кОм.

На фиг.6 представлена временная зависимость выходных синусоидальных напряжений ДУ фиг.4.

На фиг.7 приведена зависимость коэффициента усиления по напряжению ДУ фиг.4 от частоты.

Фиг.8 показывает зависимость постоянной составляющей выходного синфазного статического напряжения ДУ фиг.4 от тока третьего 19 токостабилизирующего двухполюсника (I19=Ivar) при сопротивлениях резисторов обратной связи 20 и 21 R20=R21=10 кОм.

На фиг.9 приведена схема драйвера дифференциальной линии связи на основе заявляемого ДУ фиг.4 в среде компьютерного моделирования Cadance на моделях SiGe интегральных транзисторов.

На фиг.10 представлена зависимость коэффициента усиления по напряжению драйвера фиг.9 от частоты без емкости коррекции.

На фиг.11 показана временная зависимость выходных синусоидальных напряжений драйвера фиг.9.

На фиг.12 представлена зависимость коэффициента усиления по напряжению драйвера фиг.9 от частоты с емкостью коррекции Ccorr=500 fF между базами транзисторов Q10 и Q11 при неравномерности амлитудно-частотной характеристики менее 1дБ.

Дифференциальный операционный усилитель с парафазным выходом фиг.2 содержит входной дифференциальный каскад 1 с первым 2 и вторым 3 токовыми выходами, первым 4 и вторым 5 входами, первой 6 шиной источника питания, связанной с общей эмиттерной цепью входного дифференциального каскада 1, первый 7 выходной транзистор, база которого соединена со вторым 3 токовым выходом входного дифференциального каскада 1, коллектор подключен к шине второго 8 источника питания, а эмиттер связан с первым 9 вспомогательным выходом устройства и через первый 10 токостабилизирующий двухполюсник соединен с первой 6 шиной источника питания, второй 11 выходной транзистор, база которого соединена с первым 2 токовым выходом входного дифференциального каскада 1, коллектор подключен к шине второго 8 источника питания, а эмиттер связан со вторым 12 вспомогательным выходом устройства и через второй 13 токостабилизирующий двухполюсник соединен с первой 6 шиной источника питания, третий 14 и четвертый 15 выходные транзисторы, эмиттеры которых соединены со второй 8 шиной источника питания, базы связаны друг с другом, коллектор третьего 14 выходного транзистора подключен к базе второго 11 выходного транзистора, коллектор четвертого 15 выходного транзистора подключен к базе первого 7 выходного транзистора. В схему введены первый 16, второй 17 и третий 18 дополнительные транзисторы, эмиттеры которых соединены друг с другом и через третий 19 токостабилизирующий двухполюсник связаны с первой 6 шиной источника питания, коллекторы первого 16 и второго 17 дополнительных транзисторов объединены и связаны с базами третьего 14 и четвертого 15 выходных транзисторов, база первого 16 дополнительного транзистора соединена с первым 4 входом устройства, база второго 17 дополнительного транзистора соединена со вторым 5 входом устройства, коллектор третьего 18 дополнительного транзистора связан со второй 8 шиной источника питания, причем первый 9 вспомогательный выход устройства соединен с базой третьего 18 дополнительного транзистора через первый 20 резистор обратной связи, а второй 12 вспомогательный выход устройства соединен с базой третьего 18 дополнительного транзистора через второй 21 резистор обратной связи. В частном случае входной дифференциальный каскад 1 реализован на транзисторах 22 и 23 и источнике тока 24.

В качестве первого 10, второго 13 и третьего 19 токостабилизирующих двухполюсников авторы рекомендуют использовать классические источники опорного тока на транзисторах или сравнительно высокоомные резисторы.

На фиг.3 в соответствии с п.2 формулы изобретения первый 9 вспомогательный выход устройства связан с базой третьего 18 дополнительного транзистора через последовательно соединенные первый 25 дополнительный буферный усилитель и первый 20 резистор обратной связи, а второй 12 вспомогательный выход устройства связан с базой третьего 18 дополнительного транзистора через последовательно соединенные второй 26 дополнительный буферный усилитель и второй 21 резистор обратной связи.

В качестве дополнительных буферных усилителей 25 и 26 авторы рекомендуют применение различных классических эмиттерных повторителей, в том числе на основе так называемых «бриллиантовых» транзисторов. Кроме этого на фиг.3 в соответствии с п.3 формулы изобретения между объединенными эмиттерами и объединенными базами третьего 14 и четвертого 15 выходных транзисторов включен дополнительный p-n переход 27.

Рассмотрим работу ДУ фиг.3.

Статический режим по току транзисторов предлагаемого ДУ устанавливается токостабилизирующими двухполюсниками 19, 24, 10, и 13. Причем коллекторные и эмиттерные токи транзисторов схемы:

где I0 - заданное значение опорного тока, например, 1 мА.

Статические напряжения U9 на выходе Вых.*1 и U на Вых.2 ДУ при нулевом входном сигнале (uвх=0) можно найти из уравнения:

где Uэб.18=Uэб.l6=Uэб.l7 - напряжение «эмиттер-база» транзисторов 18, 16 и 17 при одинаковых токах эмиттера Iэi=0.5I0;

Iб.18 - ток баз третьего дополнительного транзистора 18 в резисторе обратной связи 20 (21).

Таким образом, при типовых значениях токов базы транзистора 18, а также при R20=R21=500÷1000 Ом выходное синфазное напряжение ДУ фиг.3 практически равно нулю в широком диапазоне температурных и радиационных воздействий, а также изменений напряжений питания. Это весьма существенно для согласования заявляемого ДУ с последующими функциональными узлами радиоэлектронной аппаратуры.

Графики фиг.6 показывают, что в схемах ДУ фиг.4 диапазон изменения uвых при низковольтном питании (±2 В) лежит в пределах ±1 В. При этом коэффициент усиления по напряжению ДУ более 50 дБ (фиг.7).

В схеме фиг.3, которая отличается от схемы фиг.2 наличием дополнительных буферных усилителей 25 и 26, значительно снижаются требования к величине сопротивлений резисторов обратной связи 21 и 22, что позволяет получить на выходах Вых.* 1 и Вых.* 2 нулевые уровни статических напряжений U независимо от статических параметров дополнительных буферных усилителей 25 и 26. Однако в схеме фиг.3, соответствующей П.2 формулы изобретения, в низкоомной нагрузке, включенной между выходами Вых.* 1 и Вых.* 2, могут быть получены значительно большие мощности, которые определяются свойствами буферных усилителей 25 и 26. Кроме этого в архитектуре рис.3 при повышенных напряжениях питания максимальные амплитуды выходных напряжений положительной U и отрицательной U полярностей близки к сумме напряжений первого 6 Е и второго Е 8 источников питания:

Результаты компьютерного моделирования фиг.11, фиг.12 схемы фиг.9 показывают, что на основе предлагаемого ДУ реализуются широкополосные драйвера дифференциальных линий связи гигагерцевого диапазона.

Таким образом, заявляемый дифференциальный операционный усилитель имеет нулевой уровень выходного синфазного напряжения. Это весьма существенно для его согласования с последующими функциональными узлами различных систем на кристалле, а также для получения более широкого диапазона изменения выходных противофазных напряжений.

Источники информации

1. Будяков А.С., Прокопенко Н.Н., Манжула В.Г. Анализ частотных характеристик подсхем входных каскадов СВЧ операционных усилителей для сложных функциональных блоков радиационностойкой аппаратуры нового поколения [Текст] / А.С.Будяков, Н.Н.Прокопенко, В.Г.Манжула // Научно-технические ведомости СПбГПУ. Информатика, Телекоммуникации. Управление. - №3 (101) / 2010. - С.210, рис.4.

2. СВЧ операционные усилители ОА-1 - ОА-3 на основе техпроцесса SG25H2 и их практическое применение в системах связи и телекоммуникаций: учебно-методическое пособие / А.Будяков, K.Schmalz, Н.Прокопенко, C.Scheytt, Р.Островский. - Шахты: Изд-во ЮРГУЭС, 2010. - С.23, рис.2.11.

3. Будяков А.С. Микросхема низковольтного операционного усилителя ОА-3, 0_T214_bench_www с повышенным ослаблением синфазного сигнала в диапазоне высоких частот и ее практическое применение в устройствах автоматики и телекоммуникации [Текст] / А.С.Будяков, Н.Н.Прокопенко, С.В.Крюков // Проблемы современной аналоговой микросхемотехники: VII международный научно-практический семинар. В 2 ч., Ч.1 / гл. ред. Н.Н.Прокопенко; редкол.: В.Г.Немудров [и др.]. - Шахты: ГОУ ВПО «ЮРГУЭС», 2009. - С.17-22, рис.1.

4. Схемотехника СВЧ операционных усилителей для аналоговых интерфейсов с глубокой обратной связью [Текст] / А.С.Будяков, Н.Н.Прокопенко, К.Schmalz, С.Scheytt, P.Ostrovskyy // Проблемы разработки перспективных микро- и наноэлектронных систем - 2008. Сборник научных трудов III Всероссийской научно-технической конференции / под общ. ред. Академика РАН А.Л.Стемпковского. - М.: Институт проблем проектирования в микроэлектронике РАН, 2008. - С.301-306, рис.6, рис.7.

5. Патент США №4.007.427.

6. Патент США №4.101.842, fig.1.

7. Патент SU 414704.

8. Патент США 5.610.547, fig.33.

1. Дифференциальный операционный усилитель с парафазным выходом, содержащий входной дифференциальный каскад (1) с первым (2) и вторым (3) токовыми выходами, первым (4) и вторым (5) входами, первой (6) шиной источника питания, связанной с общей эмиттерной цепью входного дифференциального каскада (1), первый (7) выходной транзистор, база которого соединена со вторым (3) токовым выходом входного дифференциального каскада (1), коллектор подключен к шине второго (8) источника питания, а эмиттер связан с первым (9) вспомогательным выходом устройства и через первый (10) токостабилизирующий двухполюсник соединен с первой (6) шиной источника питания, второй (11) выходной транзистор, база которого соединена с первым (2) токовым выходом входного дифференциального каскада (1), коллектор подключен к шине второго (8) источника питания, а эмиттер связан со вторым (12) вспомогательным выходом устройства и через второй (13) токостабилизирующий двухполюсник соединен с первой (6) шиной источника питания, третий (14) и четвертый (15) выходные транзисторы, эмиттеры которых соединены со второй (8) шиной источника питания, базы связаны друг с другом, коллектор третьего (14) выходного транзистора подключен к базе второго (11) выходного транзистора, коллектор четвертого (15) выходного транзистора подключен к базе первого (7) выходного транзистора, отличающийся тем, что в схему введены первый (16), второй (17) и третий (18) дополнительные транзисторы, эмиттеры которых соединены друг с другом и через третий (19) токостабилизирующий двухполюсник связаны с первой (6) шиной источника питания, коллекторы первого (16) и второго (17) дополнительных транзисторов объединены и связаны с базами третьего (14) и четвертого (15) выходных транзисторов, база первого (16) дополнительного транзистора соединена с первым (4) входом устройства, база второго (17) дополнительного транзистора соединена со вторым (5) входом устройства, коллектор третьего (18) дополнительного транзистора связан со второй (8) шиной источника питания, причем первый (9) вспомогательный выход устройства соединен с базой третьего (18) дополнительного транзистора через первый (20) резистор обратной связи, а второй (12) вспомогательный выход устройства соединен с базой третьего (18) дополнительного транзистора через второй (21) резистор обратной связи.

2. Дифференциальный операционный усилитель с парафазным выходом по п.1, отличающийся тем, что первый (9) вспомогательный выход устройства связан с базой третьего (18) дополнительного транзистора через последовательно соединенные первый (25) дополнительный буферный усилитель и первый (20) резистор обратной связи, а второй (12) вспомогательный выход устройства связан с базой третьего (18) дополнительного транзистора через последовательно соединенные второй (26) дополнительный буферный усилитель и второй (21) резистор обратной связи.

3. Дифференциальный операционный усилитель с парафазным выходом по п.1, отличающийся тем, что между объединенными эмиттерами и объединенными базами третьего (14) и четвертого (15) выходных транзисторов включен дополнительный р-n переход (27).