Широкополосный усилитель

Иллюстрации

Показать всеИзобретение относится к области радиотехники и связи и может быть использовано в качестве устройства усиления аналоговых сигналов, в структуре аналоговых микросхем различного функционального назначения (например, СВЧ-усилителях, логарифмирующих каскадах, аналоговых перемножителях и смесителях сигналов и т.п.). Технический результат - расширение диапазона рабочих частот широкополосного усилителя. Широкополосный усилитель содержит первый (1) и второй (2) входные транзисторы (Т), эмиттеры которых связаны с первым (3) источником питания (ИП) через первый (4) и второй (5) токостабилизирующие двухполюсники (ТД) и через первый (6) и второй (7) паразитные конденсаторы соединены по переменному току с общей шиной (8) первого (3) и второго (9) ИП, источник входного сигнала (10), связанный с базой первого Т (1) и общей шиной (8), масштабирующий резистор (11), первый вывод которого подключен к эмиттеру Т (1), цепь согласования потенциалов (12), включенная между вторым (9) ИП и объединенными первыми выводами первого (13) и второго (14) логарифмирующих р-n переходов, первый (15) выходной Т, база которого соединена с коллектором Т (1) и вторым выводом первого (13) логарифмирующего р-n перехода, второй (16) выходной Т, база которого соединена с коллектором Т (2) и вторым выводом второго (14) логарифмирующего р-n перехода, причем эмиттеры Т (15) и Т (16) соединены с первым (17) источником опорного тока, а коллекторы связаны с выходной цепью нагрузки устройства (18). В схему введен третий (19) входной Т, база которого соединена с общей шиной (8), эмиттер связан с шиной первого (3) ИП через третий (20) ТД и соединен со вторым выводом масштабирующего резистора (11), а коллектор подключен к эмиттеру вспомогательного Т (21), база которого соединена с цепью согласования потенциалов (12), коллектор подключен ко второму (9) ИП, причем база Т (2) соединена с базой Т (1). 3 з.п. ф-лы, 15 ил.

Реферат

Изобретение относится к области радиотехники и связи и может быть использовано в качестве устройства усиления аналоговых сигналов, в структуре аналоговых микросхем различного функционального назначения (например, СВЧ-усилителях, логарифмирующих каскадах, аналоговых перемножителях и смесителях сигналов и т.п.).

В современной микроэлектронике при построении систем на кристалле возникает необходимость применения широкополосных усилителей с несимметричным входом, обеспечивающих логарифмирование входного напряжения (uвх) и его последующее антилогарифмирующее преобразование с помощью второго каскада на основе дифференциального усилителя [1-18]. Такие ШУ являются основой многих десятков модификаций аналоговых смесителей и перемножителей двух напряжений, ВЧ и СВЧ - управляемых усилителей и т.п. При использовании несимметричного входа, т.е. при наличии одного источника сигнала uвх, в отличие от симметричных архитектур данного класса существенно ухудшается частотный диапазон. Это обусловлено наличием паразитных емкостей на подложку у транзисторов, устанавливающих статический режим входного фазорасщепителя (преобразователя однофазного сигнала в два противофазных).

Известны схемы широкополосных двухкаскадных дифференциальных усилителей (ДУ) на основе логарифмирующих p-n переходов - так называемые ячейки Джильберта [1-18].

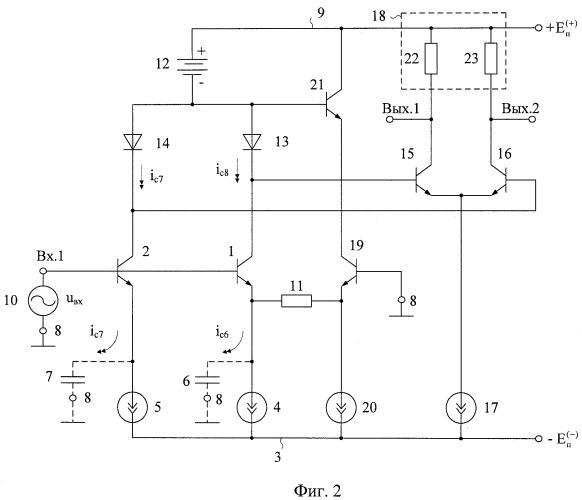

Наиболее близким по технической сущности к заявляемому устройству является широкополосный дифференциальный усилитель, фиг.1, рассмотренный в патенте США №5.521.544, fig.6. Эта же схема присутствует в патентах [2-18].

Существует недостаток известного ШУ, который состоит в значительной деградации верхней граничной частоты (fв) коэффициента усиления по напряжению (Ку) при несимметричном включении источника сигнала uвх. Следует заметить, что при более сложном симметричном управлении ШУ, например в структуре аналогового перемножителя напряжений, требуется применение входных фазорасщепителей, к которым предъявляются повышенные требования по фазовой идентичности каналов и частотному диапазону.

Основная задача предлагаемого изобретения состоит в расширении диапазона рабочих частот широкополосного усилителя.

Поставленная задача достигается тем, что в широкополосном усилителе, фиг.1, содержащем первый 1 и второй 2 входные транзисторы, эмиттеры которых связаны с первым 3 источником питания через первый 4 и второй 5 токостабилизирующие двухполюсники и через первый 6 и второй 7 паразитные конденсаторы соединены по переменному току с общей шиной 8 первого 3 и второго 9 источников, источник входного сигнала 10, связанный с базой первого 1 входного транзистора и общей шиной 8 первого 3 и второго 9 источников питания, масштабирующий резистор 11, первый вывод которого подключен к эмиттеру первого 1 входного транзистора, цепь согласования потенциалов 12, включенная между вторым 9 источником питания и объединенными первыми выводами первого 13 и второго 14 логарифмирующих p-n переходов, первый 15 выходной транзистор, база которого соединена с коллектором первого 1 входного транзистора и вторым выводом первого 13 логарифмирующего p-n перехода, второй 16 выходной транзистор, база которого соединена с коллектором второго 2 входного транзистора и вторым выводом второго 14 логарифмирующего p-n перехода, причем эмиттеры первого 15 и второго 16 выходных транзисторов соединены с первым 17 источником опорного тока, а коллекторы первого 15 и второго 16 выходных транзисторов связаны с выходной цепью нагрузки устройства 18, предусмотрены новые элементы и связи - в схему введен третий 19 входной транзистор, база которого соединена с общей шиной 8 первого 3 и второго 9 источников питания, эмиттер связан с шиной первого 3 источника питания через третий 20 токостабилизирующий двухполюсник и соединен со вторым выводом масштабирующего резистора 11, а коллектор подключен к эмиттеру вспомогательного транзистора 21, база которого соединена с цепью согласования потенциалов 12, коллектор подключен ко второму 9 источнику питания, причем база второго 2 входного транзистора соединена с базой первого 1 входного транзистора.

На фиг.1 представлена схема ШУ-прототипа.

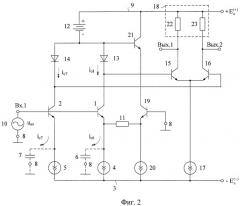

На фиг.2 представлена схема заявляемого ШУ в соответствии с п.1 формулы изобретения.

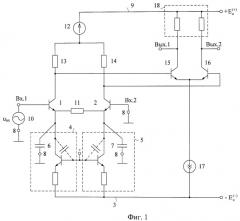

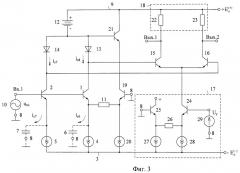

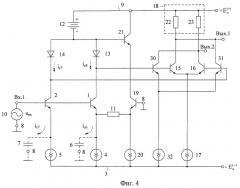

На фиг.3 приведена схема ШУ, соответствующая п.2, а на фиг.4 - п.3 формулы изобретения.

На фиг.5 приведена схема ШУ, соответствующая п.3 формулы изобретения с конкретным выполнением источников опорного тока 32 и 17.

На фиг.6 приведена схема ШУ-прототипа, а на фиг.7 - заявляемого ШУ в среде компьютерного моделирования Cadence на моделях интегральных SiGe транзисторов.

На фиг.8 показана частотная зависимость коэффициента усиления по напряжению сравниваемых схем фиг.6 и фиг.7 при емкости первого 6 паразитного конденсатора 60 фФ и различных емкостях второго 7 паразитного конденсатора (С7=С1) при одинаковых коэффициентах усиления (несимметричное управление дифференциальным каскадом).

На фиг.9 показана частотная зависимость коэффициента усиления по напряжению схем фиг.6 и фиг.7 при емкостях первого 6 паразитного конденсатора 60 фФ и емкости второго 7 паразитного конденсатора (С7=С1=230 фФ) при одинаковых коэффициентах усиления (несимметричное управление дифференциальным каскадом).

На фиг.10 показана частотная зависимость нормированного к Ку на постоянном токе коэффициента усиления Ку по напряжению схем фиг.6 и фиг.7 при емкости первого 6 паразитного конденсатора 60 фФ и емкости второго 7 паразитного конденсатора (С7=С1=230 фФ).

На фиг.11 приведена схема классического аналогового перемножителя сигналов Джильберта на базе известного ШУ, а на фиг.12 - схема аналогового перемножителя на базе заявляемого ШУ в соответствии с п.4 формулы изобретения.

На фиг.13 показана частотная зависимость коэффициентов передачи по напряжению сравниваемых схем фиг.11 и фиг.12 при одинаковых коэффициентах усиления.

На фиг.14 показана частотная зависимость нормированного коэффициента передачи по напряжению сравниваемых схем фиг.11 и фиг.12.

Графики фиг.15 показывают, что заявляемый ШУ, фиг.12, является аналоговым перемножителем двух сигналов Vx и Vy.

Из графиков фиг.9, фиг.10, фиг.13 следует, что предлагаемый ШУ обеспечивает усиление сигналов до частоты 16-18 ГГц.

Широкополосный усилитель, фиг.2, содержит первый 1 и второй 2 входные транзисторы, эмиттеры которых связаны с первым 3 источником питания через первый 4 и второй 5 токостабилизирующие двухполюсники и через первый 6 и второй 7 паразитные конденсаторы соединены по переменному току с общей шиной 8 первого 3 и второго 9 источников, источник входного сигнала 10, связанный с базой первого 1 входного транзистора и общей шиной 8 первого 3 и второго 9 источников питания, масштабирующий резистор 11, первый вывод которого подключен к эмиттеру первого 1 входного транзистора, цепь согласования потенциалов 12, включенная между вторым 9 источником питания и объединенными первыми выводами первого 13 и второго 14 логарифмирующих p-n переходов, первый 15 выходной транзистор, база которого соединена с коллектором первого 1 входного транзистора и вторым выводом первого 13 логарифмирующего p-n перехода, второй 16 выходной транзистор, база которого соединена с коллектором второго 2 входного транзистора и вторым выводом второго 14 логарифмирующего p-n перехода, причем эмиттеры первого 15 и второго 16 выходных транзисторов соединены с первым 17 источником опорного тока, а коллекторы первого 15 и второго 16 выходных транзисторов связаны с выходной цепью нагрузки устройства 18. В схему введен третий 19 входной транзистор, база которого соединена с общей шиной 8 первого 3 и второго 9 источников питания, эмиттер связан с шиной первого 3 источника питания через третий 20 токостабилизирующий двухполюсник и соединен со вторым выводом масштабирующего резистора 11, а коллектор подключен к эмиттеру вспомогательного транзистора 21, база которого соединена с цепью согласования потенциалов 12, коллектор подключен ко второму 9 источнику питания, причем база второго 2 входного транзистора соединена с базой первого 1 входного транзистора. Выходная цепь нагрузки 18 содержит, в частном случае, резисторы 22 и 23.

На фиг.3 в соответствии с п.2 формулы изобретения в качестве первого 17 источника опорного тока используется управляемый вспомогательным управляющим напряжением (Uy) источник опорного тока, который реализован на элементах 24, 25, 26, 27, 28.

На фиг.4 в соответствии с п.3 формулы изобретения в схему введены третий 30 и четвертый 31 выходные транзисторы, база третьего 30 выходного транзистора соединена с базой первого 15 выходного транзистора, база четвертого 31 выходного транзистора соединена с базой второго 16 выходного транзистора, коллектор третьего 30 выходного транзистора связан с коллектором второго 16 выходного транзистора, коллектор четвертого 31 выходного транзистора соединен с коллектором первого 15 выходного транзистора, причем объединенные эмиттеры третьего 30 и четвертого 31 выходных транзисторов соединены со вторым 3 источником питания, через второй 32 источник опорного тока. Схема фиг.4 может реализовывать функции премножения сигналов uвх и uy.

На фиг.5 в соответствии с п.4 формулы изобретения в качестве первого 17 и второго 32 источников опорного тока используются противофазно-управляемые вспомогательным управляющим напряжением uy источники опорного тока, реализованные на транзисторах 33, 35, источниках тока 34, 36 и резисторе 37.

Рассмотрим преимущества заявляемой схемы ШУ, фиг.2.

В схеме ШУ-прототипа, фиг.1, на высоких частотах при несимметричном (однофазном) включении источника сигнала uвх (10) образуются неодинаковые пути передачи uвx на базы выходных транзисторов 15 и 16. Это обусловлено наличием паразитных конденсаторов 6 и 7 (емкостей на подложку транзисторов, образующих первый 4 и второй 5 токостабилизирующие двухполюсники). Поэтому фазовая погрешность преобразования uвx начинает проявляться уже на частотах f=5,5 ГГц (фиг.10).

В заявляемом ШУ, фиг.2, каналы передачи сигнала (10) uвx на входы второго каскада (базы первого 15 и второго 16 выходных транзисторов) одинаковы, что способствует расширению частотного диапазона устройства. Данные выводы подтверждены результатами компьютерного моделирования (фиг.10), которые показывают, что верхняя граничная частота (fв) коэффициента усиления по напряжению ШУ, фиг.2, увеличивается в 2-3 раза до 18,5 ГГц.

В качестве источников опорного тока 17 и 32 авторы рекомендуют использование классических преобразователей «напряжение-ток» на основе дифференциальных каскадов с местной обратной связью (на фиг.3 - это транзисторы 25 и 24, на фиг.4 - транзисторы 33 и 35).

Цепь согласования потенциалов 12 может быть реализована на основе стабилитронов или резисторов.

В качестве первого 4 и второго 5 токостабилизирующих двухполюсников, а также первого 17 и второго 32 источников опорного тока и второго могут применяться высокоомные резисторы, а также классические схемы на транзисторах, например токовые зеркала.

На базе предлагаемого ШУ в соответствии с п.3 и п.4 формулы изобретения реализуются управляемые усилители (фиг.3) и аналоговые перемножители сигналов, схемы и характеристики которых приведены на фиг.5, фиг.12, фиг.14 и фиг.15.

Таким образом, заявляемый широкополосный усилитель характеризуется более широким (в 2÷3 раза) частотным диапазоном.

БИБЛИОГРАФИЧЕСКИЙ СПИСОК

1. Патент США №5.521.544, fig.6.

2. Патент США №6.111.463, fig.1.

3. Патент США №4.572.975, fig.1.

4. Патент США №5.550.512, fig.3.

5. Патент США №5.115.409, fig.1.

6. Патент США №4.439.696, fig.2.

7. Патент США №5.883.539, fig.2.

8. Патент США №4.288.707.

9. Патент США №5.774.020, fig.1.

10. Патент США №5.677.646.

11. Патент США №5.039.952, fig.5.

12. Патент США №5.734.294, fig.4.

13. Патент США №5.886.916, fig.1.

11. Патент США №6.369.618, fig.2.

15. Патентная заявка США №2002/0053935, fig.4.

16. Патентная заявка США №2004/0251965, fig.5.

17. Патентная заявка США №2004/0032298, fig.1.

18. Патент WO 2002/071597.

1. Широкополосный усилитель, содержащий первый (1) и второй (2) входные транзисторы, эмиттеры которых связаны с первым (3) источником питания через первый (4) и второй (5) токостабилизирующие двухполюсники и через первый (6) и второй (7) паразитные конденсаторы соединены по переменному току с общей шиной (8) первого (3) и второго (9) источников питания, источник входного сигнала (10), связанный с базой первого (1) входного транзистора и общей шиной (8) первого (3) и второго (9) источников питания, масштабирующий резистор (11), первый вывод которого подключен к эмиттеру первого (1) входного транзистора, цепь согласования потенциалов (12), включенная между вторым (9) источником питания и объединенными первыми выводами первого (13) и второго (14) логарифмирующих р-n переходов, первый (15) выходной транзистор, база которого соединена с коллектором первого (1) входного транзистора и вторым выводом первого (13) логарифмирующего р-n перехода, второй (16) выходной транзистор, база которого соединена с коллектором второго (2) входного транзистора и вторым выводом второго (14) логарифмирующего р-n перехода, причем эмиттеры первого (15) и второго (16) выходных транзисторов соединены с первым (17) источником опорного тока, а коллекторы первого (15) и второго (16) выходных транзисторов связаны с выходной цепью нагрузки устройства (18), отличающийся тем, что в схему введен третий (19) входной транзистор, база которого соединена с общей шиной (8) первого (3) и второго (9) источников питания, эмиттер связан с шиной первого (3) источника питания через третий (20) токостабилизирующий двухполюсник и соединен со вторым выводом масштабирующего резистора (11), а коллектор подключен к эмиттеру вспомогательного транзистора (21), база которого соединена с цепью согласования потенциалов (12), коллектор подключен ко второму (9) источнику питания, причем база второго (2) входного транзистора соединена с базой первого (1) входного транзистора.

2. Широкополосный усилитель по п.1, отличающийся тем, что в качестве первого (17) источника опорного тока используется управляемый вспомогательным управляющим напряжением источник опорного тока.

3. Широкополосный усилитель по п.1, отличающийся тем, что в схему введены третий (30) и четвертый (31) выходные транзисторы, база третьего (30) выходного транзистора соединена с базой первого (15) выходного транзистора, база четвертого (31) выходного транзистора соединена с базой второго (16) выходного транзистора, коллектор третьего (30) выходного транзистора связан с коллектором второго (16) выходного транзистора, коллектор четвертого (31) выходного транзистора соединен с коллектором первого (15) выходного транзистора, причем объединенные эмиттеры третьего (30) и четвертого (31) выходных транзисторов соединены со вторым (3) источником питания через второй (32) источник опорного тока.

4. Широкополосный усилитель по п.3, отличающийся тем, что в качестве первого (17) и второго (32) источников опорного тока используются противофазно-управляемые вспомогательным управляющим напряжением источники опорного тока.