Способ и устройство кодирования и декодирования данных

Иллюстрации

Показать всеИзобретение относится к кодированию и декодированию данных, в частности к способу и устройству турбокодирования и турбодекодирования. При осуществлении способов и устройства для турбокодирования при работе турбокодера (101) размер турбоперемежителя (201) определяется в зависимости от размера информационного блока, и выбираются соответствующие параметры перемежения. Эти параметры конфигурируют турбоперемежитель, который представляет собой бесконфликтный перемежитель и который основывается на перемежителе с перестановкой с использованием квадратного многочлена QPP или перемежителе с почти регулярной перестановкой ARP. Если размер информационного блока не совпадает с поддерживаемым размером перемежителя, тогда информационный блок заполняется при помощи вставки битов заполнителя. Технический результат - обеспечение высокого уровня параллельной обработки без конфликтов при обращении к памяти. 6 н. и 2 з.п. ф-лы, 6 ил., 3 табл.

Реферат

Область техники, к которой относится изобретение

Настоящее изобретение относится, в основном, к кодированию и декодированию данных, в частности к способу и устройству турбокодирования и турбодекодирования.

Уровень техники

Передачи цифровых данных по проводным и беспроводным линиям связи могут искажаться, например, шумом в линии связи или канале, помехой от других передач или других окружающих факторов. Для борьбы с ошибками, вводимыми каналом, многие системы связи применяют методы коррекции ошибок, способствующие выполнению связи.

Одним методом, используемым для коррекции ошибок, является турбокодирование информационного блока, перед тем как он будет передан по каналу. Используя такой метод, кодер в передатчике системы связи кодирует входной блок u длины K' битов в блок x кодового слова из N битов. Блок кодового слова затем передается по каналу, возможно после дополнительной обработки, такой как канальное перемежение, как определено в спецификациях Института инженеров по электротехнике и радиоэлектронике IEEE 802 16е. В приемнике турбодекодер принимает вектор y принятого сигнала длины N в качестве входа и генерирует оценку вектора u.

Обычно турбокодер состоит из двух составных сверточных кодеров. Первый составной кодер принимает входной блок u в качестве входа в его исходном порядке, и второй составной кодер принимает входной блок u в его перемеженном порядке после пропускания u через турбоперемежитель π. Выходной сигнал x турбокодера состоит из систематических битов (равных входному блоку u), битов контроля четности от первого составного кодера и битов контроля четности от второго составного кодера.

Соответственно, турбодекодер в приемнике системы связи состоит из двух составных сверточных декодеров, один для каждого составного кода. Составные декодеры разделяются перемежителем π и соответствующим деперемежителем π-1. Сообщения в формате логарифмических отношений правдоподобия (LLR) пропускаются между составными декодерами итеративно. Решение принимается после нескольких итераций.

Турбоперемежитель π является ключевым компонентом в турбокодовой конструкции. Он отвечает за скремблирование входного блока u псевдослучайным образом, таким образом обеспечивая кодовые слова x с хорошим распределением весов, следовательно, с хорошими возможностями исправления ошибок. В дополнение к рабочим характеристикам декодирования определение турбоперемежителя π в значительной степени оказывает влияние на реализацию турбодекодера в приемнике. Чтобы сделать возможным высокий уровень параллельной обработки без конфликтов при обращении к памяти, турбоперемежитель π должен иметь бесконфликтные свойства.

Краткое описание чертежей

Фиг.1 представляет собой блок-схему передатчика.

Фиг.2 представляет собой блок-схему турбокодера по фиг.1.

Фиг.3 представляет собой блок-схему приемника.

Фиг.4 представляет собой блок-схему турбодекодера по фиг.4.

Фиг.5 представляет собой блок-схему последовательности операций, изображающую принцип действия передатчика по фиг.1.

Фиг.6 представляет собой блок-схему последовательности операций, изображающую принцип действия приемника по фиг.3.

Подробное описание чертежей

Чтобы обратить внимание на вышеупомянутую потребность в бесконфликтных перемежителях, в данном документе обеспечивается способ и устройство выбора размеров перемежителя для турбокодов.

Во время работы принимается информационный блок размера K. Определяется размер K' перемежителя, где K' связан с K”, где K” из набора размеров; причем набор размеров содержит K”=a p×f, p min≤p≤p max; f min≤f≤f max, где a представляет собой целое число, f представляет собой постоянное целое число между f min и f max, и p принимает целочисленные значения между p min и p max, a>1, p max>p min, p min>1. Информационный блок размера K заполняется во входной блок размера K'. Входной блок перемежается с использованием перемежителя размера K'. Исходный входной блок и перемеженный входной блок кодируются для получения блока кодового слова. Блок кодового слова передается по каналу.

В другом варианте осуществления настоящего изобретения этап определения размера K' перемежителя, который связан с K”, содержит этап использования K'=K”.

В еще другом варианте осуществления настоящего изобретения этап определения размера K' перемежителя, который связан с K”, содержит этап использования K'=K”, когда K” не является кратным (2m-1); в противном случае, использования K'=K”+δ(K”), когда K” является кратным (2m-1), причем m представляет собой емкость памяти составного сверточного кодера, и δ(K”) представляет собой небольшое положительное или отрицательное целое число, не равное кратному (2m-1). В одном варианте осуществления m=3.

В еще другом варианте осуществления настоящего изобретения этап перемежения входного блока содержит этап использования перестановки π(i)=(iP 0+A+d(i))modK', где 0≤i≤K'-1 представляет собой последовательный индекс положений символа после перемежения, π(i) представляет собой индекс символа перед перемежением, соответствующий положению i, K' представляет собой размер перемежителя в символах, P 0 представляет собой число, которое является относительно простым для K', А представляет собой постоянную, С представляет собой небольшое число, которое делит K', и d(i) представляет собой вектор возмущения вида d(i)=β(imodC)+P 0×α(imodC), где α(·) и β(·) представляют собой векторы, каждый длиной С, периодически применяемый для 0≤i≤K'-1.

В еще другом варианте осуществления настоящего изобретения этап перемежения входного блока содержит этап использования перестановки π(i)=(f 1×i+f 2×i 2)modK', где 0≤i≤K'-1 представляет собой последовательный индекс положений символа после перемежения, π(i) представляет собой индекс символа перед перемежением, соответствующий положению i, K' представляет собой размер перемежителя в символах, и f 1 и f 2 представляют собой коэффициенты, определяющие перемежитель.

Перед описанием кодирования и декодирования данных предоставляются следующие определения, чтобы установить необходимые основные принципы.

- K обозначает размер информационного блока.

- K' обозначает размер перемежителя (т.е. размер входного блока, для которого определяется перемежитель турбокода).

- K” обозначает вспомогательную переменную, которая может использоваться при определении размера перемежителя.

- K filler обозначает количество битов заполнителя, добавляемых к информационному блоку.

- π обозначает внутренний перемежитель турбокода.

- Операция определения нижнего значения обозначает наибольшее целое число, которое меньше или равно x, и операция определения верхнего значения обозначает наименьшее целое число, которое больше или равно x.

- u обозначает входной блок, который имеет длину K' и который посылается на турбокодер в передатчике. обозначает оцененный входной блок, который имеет длину K' и который создается турбодекодером в приемнике. Отметьте, что , когда нет ошибки декодирования. В противном случае, .

Обратимся теперь к чертежам, на которых подобные позиции обозначают подобные компоненты, фиг.1 представляет собой блок-схему передатчика 100. Как показано, передатчик 100 содержит схему 109 вставки заполнителя, турбокодер 101, схему 103 определения размера перемежителя, таблицу 105 параметров перемежителя и передатчик 107. Кодер 101, предпочтительно, представляет собой турбокодер Проекта партнерства по созданию системы 3-го поколения (3GPP) со скоростью 1/3, однако, методы, описанные в данном документе для работы кодера 101, могут быть применены к другим кодерам, включая, но не ограничиваясь турбокодерами, выполняющими турбокодирование с хвостовыми битами или без хвостовых битов, циклически замкнутыми, бинарными или дуобинарными турбокодерами, турбокодерами, использующими различные методы согласования скорости и выкалывания, и т.д. Схема 103 определяет размер K' перемежителя, который связан с K”, где K” из набора размеров; причем набор размеров содержит K”=a p×f, p min≤p≤p max; f min≤f≤f max, причем a представляет собой целое число, f представляет собой постоянное целое число между f min и f max, и p принимает целые значения между p min и p max , a>1, p max>p min, p min>1.

Во время работы передатчика 100 информационный блок размера K должен кодироваться турбокодером 101. Для некоторых систем связи, где используется большое количество различных K, является неэффективным (и часто невозможным) определение бесконфликтного (CF) перемежителя для каждого размера K информационного блока. Является предпочтительным, если малый набор (K') хорошо сконструированных CF-перемежителей может охватывать все размеры информационных блоков. При заданном размере K информационного блока подходящий размер K' перемежителя может быть выбран схемой 103 из набора доступных размеров (например, размеров перемежителя, перечисленных в таблице 105). Информационный блок затем заполняется во входной блок размера K' посредством схемы 109 и посылается в качестве входа на турбокодер 101. Типовым размещением является заполнение информационного блока K filler битами заполнителя (при помощи схемы 109 вставки заполнителя). Отметьте, что термины «размер» и «длина» используются попеременно для указания количества элементов в блоке или векторе.

Если K' выбрано схемой 103, оно подается на турбокодер 101. Во время кодирования может использоваться бесконфликтный перемежитель (не показан на фиг.1). Например, перемежитель может использовать перестановку π(i)=(iP 0+A+d(i))modK', причем 0≤i≤K'-1 представляет собой последовательный индекс положений символа после перемежения, π(i) представляет собой индекс символа перед перемежением, соответствующий положению i, K' представляет собой размер перемежителя в символах, P 0 представляет собой число, которое является относительно простым для K', А представляет собой постоянную, С представляет собой небольшое число, которое делит K', и d(i) представляет собой вектор «возмущения» вида d(i)=β(imodC)+P 0×α(imodC), где α(·) и β(·) представляют собой векторы, каждый длиной C, периодически применяемый для 0≤i≤K'-1. В качестве другого примера, перемежитель может использовать перестановку π(i)=(f 1×i+f 2×i 2)modK', где 0≤i≤K'-1 представляет собой последовательный индекс положений символа после перемежения, π(i) представляет собой индекс символа перед перемежением, соответствующий положению i, K' представляет собой размер перемежителя в символах, и f 1 и f 2 представляют собой коэффициенты, определяющие перемежитель. Как правило, символ может состоять из многочисленных битов, и этап перемежения может использовать дополнительный этап перестановки битов в символе. Без потери общности, обсуждение ниже рассматривает типовой случай, где символ состоит только из одного бита (таким образом, нет необходимости переставлять биты в символе), и термины «бит» и «символ» могут использоваться попеременно.

Выходной результат турбокодера 101 содержит блок x кодового слова, и x посылается на передатчик 107, где он передается по каналу. Передатчик может выполнять дополнительную обработку, такую как согласование скоростей, канальное перемежение, модуляция и т.д. перед передачей блока x кодового слова по каналу.

Фиг.2 представляет собой блок-схему кодера 101 по фиг.1. Как показано, кодер 101 содержит перемежитель 201, схему 202 кодирования и схему 203 кодирования. Пример кодера представляет собой турбокодер, определенный в спецификации 3GPP. Исходная скорость кодирования турбокодера, определенного в 3GPP, имеет присущую данной системе скорость кодирования R=1/3. На выходе турбокодера три бита создаются для каждого бита во входном блоке: один систематический бит (равный биту во входном блоке), один бит контроля четности от составного кодера 1, один бит контроля четности от составного кодера 2. Кроме того, выходной результат турбокодера также может включать в себя N TB хвостовых битов, которые используются для завершения решетки составных кодов. Например, для турбокода 3GPP N TB=12 битов на выходе турбокодера, 6 хвостовых битов на составной код. С другой стороны, можно использовать циклически замкнутые составные сверточные коды, таким образом делая N TB=0.

Перемежителем 201 может быть бесконфликтный перемежитель. Перемежитель π(i), 0≤i≤K', например, является бесконфликтным для размера W окна, если и только если он удовлетворяет следующему ограничению как для ψ=π (перемежитель), так и для ψ=π-1 (деперемежитель),

(1),

где 0≤j<W, 0≤t; ν<M(=K'/W) и t≠ν. Хотя это не всегда необходимо, для эффективной конструкции турбодекодера обычно все M окон заполнены, где K'=MW. Члены в (1) представляют собой адреса банка памяти, по которым одновременно обращаются M процессоров при записи косвенных значений в выходные банки памяти во время итеративного декодирования. Если все эти адреса банка памяти являются уникальными в течение каждой операции считывания и записи, то нет конфликтов при обращении к памяти и, следовательно, может быть исключена задержка перемежения (деперемежения), приводя к высокоскоростной реализации декодера.

Во время работы турбокодера 101 входной блок длиной K' битов поступает как на перемежитель 201, так и на схему 202 кодирования. Перемежителем 201 может быть бесконфликтный перемежитель размера K'.

Перемежитель 201 перемежает входной блок и пропускает входной блок в перемеженном порядке на схему 203 кодирования. Схема 203 кодирования затем кодирует перемеженный входной блок. Аналогичным образом, схема 202 кодирования кодирует исходный входной блок. Блок x кодового слова состоит из систематического блока (равного входному блоку), выходного результата схемы 202 кодирования и выходного результата схемы 203 кодирования. Блок x кодового слова затем посылается на передатчик 107, который также может непосредственно принимать копию входного блока.

В качестве примера бесконфликтного перемежителя, перемежитель с почти регулярной перестановкой (ARP) определяется следующим выражением:

π(i)=(iP 0+A+d(i))modK',

где 0≤i≤K'-1 представляет собой последовательный индекс положений бита после перемежения, π(i) представляет собой индекс бита перед перемежением, соответствующий положению i, K' представляет собой размер перемежителя, P 0 представляет собой число, которое является относительно простым для K', А представляет собой постоянную, С представляет собой небольшое число, которое делит K', и d(i) представляет собой вектор возмущения вида d(i)=β(imodC)+P 0×α(imodC), где α(·) и β(·) представляют собой векторы, каждый длиной С, периодически применяемые для 0≤i≤K'-1. Как α(·), так и β(·) состоят из кратных C. Общий перемежитель π(·), составленный таким образом, имеет квазициклические (т.е. периодические) свойства с периодом C, и при использовании циклически замкнутых турбокодов сам турбокод становится квазициклическим, приводя к упрощенной процедуре конструирования кода.

В качестве другого примера бесконфликтного перемежителя, перемежитель с перестановкой с использованием квадратного многочлена (QPP) определяется следующим выражением π(i)=(f 1×i+f 2×i 2)modK', где 0≤i≤K'-1 представляет собой последовательный индекс положений символа после перемежения, π(i) представляет собой индекс символа перед перемежением, соответствующий положению i, K' представляет собой размер перемежителя в символах, и f 1 и f 2 представляют собой коэффициенты, определяющие перемежитель. Подобно перемежителям ARP турбокод также является квазициклическим, если он циклически замкнутый.

Если перемежитель 201 может удовлетворять (1) различным значениям M, тогда декодер может быть реализован с использованием различных степеней параллельности (один для каждого M). Таким образом, желательно выбрать K', который имеет различные коэффициенты. Для перемежителя ARP длины K' может использоваться любой размер W окна, где W представляет собой кратное C и коэффициента K', для высокоскоростного декодирования без конфликтов при обращении к памяти. С различным определением параллельных окон можно использовать любой коэффициент K в качестве числа параллельных окон. Для перемежителя QPP любой коэффициент размера K' перемежителя представляет собой возможный уровень параллельности M. Это обеспечивает гибкость и масштабируемость конструкции декодера, допуская широкий диапазон коэффициентов M параллельности. Таким образом, хороший компромисс между скоростью декодирования и сложностью может быть достигнут на основе требований к системе (или классам пользовательских элементов).

Выбор размера K' перемежителя

Как описано выше, схема 103 определения размера перемежителя должна определять размер K' перемежителя для данного K. Этот раздел описывает путь выбора ограниченного количества размеров (т.е. K'), для которых перемежители турбокода могут быть определены. Как указано ранее, схема вставки заполнителя (вместе со способами выкалывания или согласования скорости) может использоваться для обработки любого размера K информационного блока. Как правило, выбор размера перемежителя должен принимать во внимание нагрузку декодирования и ухудшение рабочих характеристик из-за битов заполнителя.

Желательно, чтобы количество битов K filler заполнителя, добавляемых к информационному блоку для формирования входного блока, ограничивалось небольшим процентом (например, примерно 10-13%) от размера K информационного блока. Это достигается посредством ограничения разности между соседними размерами перемежителя, т.е. соседними значениями K' (предполагая, что все доступные значения K' хранятся в возрастающем порядке). Количество битов заполнителя минимизируется посредством выбора наименьшего доступного K', так что K'≥K. Количество битов заполнителя равно K filler=K'-K. Однако также могут быть выбраны другие доступные значения K'≥K, если потребуется.

Рассмотрим следующий набор размеров, определенный для охвата размеров информации между K min и K max.

K"=a p ×f, P min ≤P≤P max, f min ≤f≤f max (2),

где a представляет собой целое число, f представляет собой постоянное целое число между f min и f max, и p принимает целые значения между p min и p max, a>1, p max>p min, p min>1. Хотя это и не является обязательным, можно выбрать эти параметры, так что и в тоже время отбрасывая любые размеры, которые могут быть необязательными. Этот способ выбора ограниченного набора размеров для охвата диапазона размеров информационного блока упоминается как полулогарифмическое расслоение. Для данного информационного блока размера K размер K' связан с K”, основанном на таблице полулогарифмического расслоения, и размером K входного блока.

Полулогарифмическое расслоение подобно операции сжатия, применяемой при сжатии сигналов с большим динамическим диапазоном, например, компандеры по А-закону и мю-закону, используемые в речевых кодеках. Правило полулогарифмического расслоения позволяет эффективной конструкции охватывать большой диапазон размеров информационного блока.

Из нескольких путей выбора параметров одним путем выбора значений f min и f max является выравнивание значений K”, вытекающих из p, друг с другом, т.е. a p×(f max+1)=a p+1×f min, таким образом

f max =a×f min -1.

Для данного значения p разделение между двумя соседними размерами K” блоков определяется посредством a p, которое означает, что добавляется максимум a p-1 битов заполнителя, если размер K информационного блока находится в группе p, и размер перемежителя равен K”. Таким образом, доля битов K filler заполнителя относительно размера K информационного блока ограничивается так, как показано ниже, что происходит тогда, когда размер K блока несколько больше размера, определяемого посредством (p, f min), и, используя K'=K”, определяемого посредством (p, f min+1), следующим:

Альтернативно, значения K”, вытекающие из соседнего p, могут выравниваться друг с другом посредством a p×f max=a p+1×(f min-1), приводя к f max=a×(f min-1). Это даст аналогичную границу K filler/K. Поэтому параметры для полулогарифмического расслоения могут быть настроены в соответствии с диапазоном поддерживаемых размеров блока и также по допустимой доли битов заполнителя. Выбор f min требует равновесия между следующими двумя требованиями:

- f min должна быть большой, чтобы уменьшить долю битов заполнителя;

- f min должна быть малой, чтобы ограничивать размер таблицы перемежителя, так как количество размеров блока, определенных для каждого p, равно f max-f min+1=(a-1)×f min, предполагая, что f max=a×f min-1.

Способ полулогарифмического расслоения является очень простым в том, что для любого размера блока подлежащий использованию размер K' перемежителя может легко определяться на основе K”, вычисленного из (2). Если размеры полулогарифмического расслоения определены (K”), размер K' перемежителя может быть получен из размеров полулогарифмического расслоения (без существенного отклонения) посредством, например:

1. Используя K'=K”. Другими словами, размеры полулогарифмического расслоения могут непосредственно использоваться в качестве действительных размеров перемежителя.

2. Используя K'=K”, когда K” не является кратным (2m-1), в противном случае, используя K'=K”+δ(K”), когда K” является кратным (2m-1), причем m является емкостью памяти составного сверточного кодера, и δ(K”) представляет собой небольшое положительное или отрицательное целое число, не равное кратному (2m-1). Это полезно, если составные сверточные коды являются циклически замкнутыми, где кратные (2m-1) являются недопустимыми. Размеры, определенные по способу полулогарифмического расслоения по (2), иногда могут включать в себя размеры, которые являются неподходящими размерами перемежителя для турбокодирования. Например, циклически замкнутая версия турбокодера 3GPP с восемью состояниями (m=3) не поддерживает размеры входного блока (т.е. размеры перемежителя), которые являются кратными 7 (т.е. 2m-1). В таких случаях, всякий раз, когда уравнение (2) приводит к размеру, который является кратным 2m-1, малое значение вычитается или добавляется к нему, так что результирующий размер больше не является кратным 2m-1.

Например, если a=2, f min=8 и f max=15, тогда размеры перемежителя вида K'=K”=2p×14 являются кратными 7, и, следовательно, являются недействительными размерами перемежителя при использовании циклически замкнутого турбокода (TC) 3GPP. Поэтому этот случай должен обрабатываться с небольшим изменением, например, используя K'=K”, когда K” не является кратным 7; в противном случае, используя K'=K”+δ(K”), когда K” является кратным 7, и δ(K”) является малым положительным или отрицательным целым числом, не равным кратному 7.

Для размеров K”, которые являются недействительным выбором для циклически замкнутых перемежителей, одним простым путем определения связанного размера K' перемежителя является посредством вычитания (добавление также допустимо) d×C из K”, где d представляет собой малое положительное целое число, и d не является кратным 7. Для перемежителя ARP C может быть длиной цикла перемежителя ARP, используемой для размеров блока, близких к K', в наборе доступных размеров. (Вспомните, что размер блока перемежителя ARP представляет собой кратное длин C цикла.) Другими словами,

K'=K”-dC (3)

или

K'=K”+dC (4),

где K” является кратным 7. Так как C обычно представляет собой четное целое число, такое как 4, 8, 12 или 16, эта подстройка дает два преимущества, а именно, (а) K' не является кратным 7, и (b) K' является кратным C и, следовательно, может быть разработан перемежитель ARP для размера K'.

Для простоты, один и тот же d может выбираться для всех K”, которые необходимо подстраивать. Одним важным моментом для выбора d является то, что он должен быть таким, чтобы все размеры, полученные посредством (3) или (4), имели значительное количество коэффициентов, которые позволяют поддерживать широкий диапазон параллельности для CF-перемежителя, определенного таким образом.

Пример выбора размера перемежителя

Для системы долгосрочной эволюции (LTE) 3GPP не является существенным определение CF-перемежителя для каждого размера блока между 40 и 5114 битами. Ограниченный или малый набор хорошо разработанных CF-перемежителей достаточен для того, чтобы охватить все размеры блока. Для неопределенных размеров блока (т.е. для которых не определены CF-перемежители) дополнение нулями (т.е. присоединение битов заполнителя) может эффективно использоваться, как описано выше.

В качестве первого примера, набор перемежителей, пригодный для охватывания размеров информационного блока для долгосрочной эволюции (LTE) 3GPP в таблице 105, определяется на основе способа полулогарифмического расслоения, описанного выше. Конкретно,

K"=2 p ×f, p=4,5,…,9; f=8,9,…,15, (5)

и K' определяется из K”. Размеры перемежителя определяются следующим образом: используя K'=K” и для p=4,5,6,7,8,9 и f=8,9,10,11,12,13,15, и используя K'=K”-dC для p=4,5,6,7,8,9 и f=14, охватывая K от 128 до 7680. Последние три размера (f=13,14,15), соответствующие p=9, могут быть удалены, так что K max=6144 при K min=128. Уравнение (3) используется вместе с d=2, когда f=14 (т.е. чтобы исключить размеры перемежителя, которые являются множителями 7), чтобы обрабатывать циклически замкнутые ТС. Если определены размеры перемежителя в 105, CF-перемежитель может быть разработан для каждого размера перемежителя.

При заданном любом размере K информационного блока схема 103 может определять размер K' перемежителя, подлежащий использованию для K, посредством выбора наименьшего значения K' из 105, которое больше или равно K. С известным K и f min=2b, f max=2b+1-1, где b представляет собой целое число, параметры p и f могут быть вычислены следующим образом:

(6)

В частности, для параметров в (5) b=3, и

С параметрами p и f размер K' блока может вычисляться с использованием (2) или (5), и, кроме того, когда f является кратным 7, и используется циклически замкнутое кодирование, дополнительно может использоваться размер перемежителя, вычисленный с использованием (3) или (4). Затем выполняется поиск параметров, ассоциированных с перемежителем размера K', из запоминающего средства для параметра 105 перемежителя, который обычно хранится в памяти для устройства связи.

В качестве второго примера, предполагаемый набор полных размеров K' перемежителя для охватывания К от 40 до 8192 битов представляет собой:

Для K'∈[264, 8192], K'=2p×f, p=3,…,7; f=33,34,…,64.

Для K' менее 264 используется размер шага 8, так что K'=40, 48, …, 256.

Эти размеры также перечислены ниже.

| 40 | 48 | 56 | 64 | 72 | 80 | 88 | 96 | 104 | 112 |

| 120 | 128 | 136 | 144 | 152 | 160 | 168 | 176 | 184 | 192 |

| 200 | 208 | 216 | 224 | 232 | 240 | 248 | 256 | 264 | 272 |

| 280 | 288 | 296 | 304 | 312 | 320 | 328 | 336 | 344 | 352 |

| 360 | 368 | 376 | 384 | 392 | 400 | 408 | 416 | 424 | 432 |

| 440 | 448 | 456 | 464 | 472 | 480 | 488 | 496 | 504 | 512 |

| 528 | 544 | 560 | 576 | 592 | 608 | 624 | 640 | 656 | 672 |

| 688 | 704 | 720 | 736 | 752 | 768 | 784 | 800 | 816 | 832 |

| 848 | 864 | 880 | 896 | 912 | 928 | 944 | 960 | 976 | 992 |

| 1008 | 1024 | 1056 | 1088 | 1120 | 1152 | 1184 | 1216 | 1248 | 1280 |

| 1312 | 1344 | 1376 | 1408 | 1440 | 1472 | 1504 | 1536 | 1568 | 1600 |

| 1632 | 1664 | 1696 | 1728 | 1760 | 1792 | 1824 | 1856 | 1888 | 1920 |

| 1952 | 1984 | 2016 | 2048 | 2112 | 2176 | 2240 | 2304 | 2368 | 2432 |

| 2496 | 2560 | 2624 | 2688 | 2752 | 2816 | 2880 | 2944 | 3008 | 3072 |

| 3136 | 3200 | 3264 | 3328 | 3392 | 3456 | 3520 | 3584 | 3648 | 3712 |

| 3776 | 3840 | 3904 | 3968 | 4032 | 4096 | 4224 | 4352 | 4480 | 4608 |

| 4736 | 4864 | 4992 | 5120 | 5248 | 5376 | 5504 | 5632 | 5760 | 5888 |

| 6016 | 6144 | 6272 | 6400 | 6528 | 6656 | 6784 | 6912 | 7040 | 7168 |

| 7296 | 7424 | 7552 | 7680 | 7808 | 7936 | 8064 | 8192 |

Отметьте, что показанные выше размеры представляют собой только пример, определенный для максимального K' из 8192 битов и используемый в сравнительном исследовании 42 размеров информационного блока. Если используется другой максимум из 6144 битов, тогда любой K', который больше максимума, будет удаляться из списка. Также, для упрощения, размеры не учитывали различие между использованием составных кодов без циклического замыкания или циклически замкнутых составных кодов. Если турбокодер сделан циклически замкнутым, тогда могут использоваться K, которые являются кратными 7. Они или удаляются, или модифицируются, как описано ранее. Наконец, дополнительные размеры перемежителя могут добавляться к этим вышеупомянутым, чтобы уменьшить промежуток между перемежителями. Например, если используется максимальный промежуток 64, дополнительные перемежители определяются между перемежителями с промежутком 128 в таблице. Если тогда используется циклически замкнутый, и K' кратные 7 удалены, то максимальный промежуток тогда снова составляет 128.

В качестве еще другого примера выбора размера перемежителя, система может использовать CF-перемежитель только тогда, когда транспортный блок (TB) (количество информационных битов до сегментирования) превышает некоторое значение. Например, если максимальным определенным размером является 5114, когда транспортный блок превышает 5114, может использоваться CF-перемежитель, такой как ARP или QPP. В этих случаях, сегментирование может создать K' менее 5114, но CF-перемежитель используется для этого K'. K, поэтому может турбоперемежаться, используя как первый перемежитель (такой как не-CF-перемежитель 3GPP, или другой перемежитель), так и второй перемежитель (такой как бесконфликтный перемежитель), в зависимости от размера транспортного блока перед сегментированием. Первый и второй перемежитель может иметь различные наборы K'. Например, первый перемежитель может, по существу, определяться для всех K=K', тогда как второй перемежитель определяется с K', как указано выше. В некоторых случаях, единственный процессор или меньшее количество процессоров может использоваться для первого перемежителя.

Пример перемежителя ARP

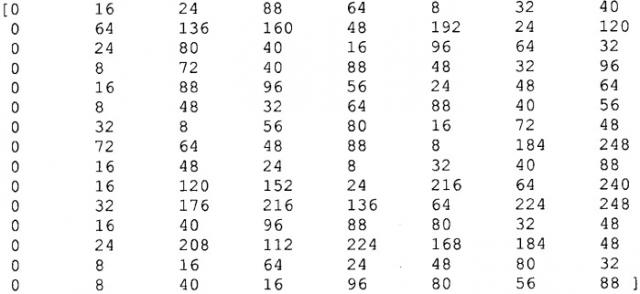

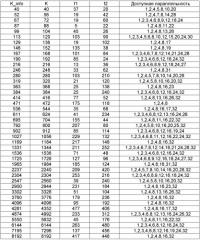

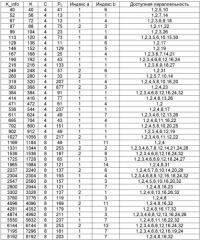

Поднабор из 42 CF-перемежителей ARP, пригодных для того, чтобы охватить размеры информационных блоков для долгосрочной эволюции (LTE) 3GPP, показаны в таблице 1. Длина цикла C=4 используется для K<1024, C=8 - для K≥1024. Большая длина C цикла приводит к лучшему минимальному расстоянию d min при больших размерах блока. Также, вместо A=3, A=0 используется для всех размеров. Кроме того, вместо того, чтобы каждый K имел различный вектор α(·) и β(·), разрешен только небольшой набор значений α и β, чтобы уменьшить объем хранения определения перемежителя. Набор разрешенных значений α и β определен ниже.

Когда длина цикла C=4,

α=

β=

Когда длина цикла C=8,

α=

β=

Таким образом, каждая строка α может использоваться в качестве вектора α, каждая строка β может использоваться в качестве вектора β. Индекс a и b, поэтому определяются для каждого K, чтобы индексировать строки α и β, где 1<=a<=2, 1<=b<=2C. Способ индексирования существенно уменьшает запоминающее устройство перемежителя ARP, так как только P 0 (8 битов), индекс a (1 бит) и b (3-4 бита) необходимо хранить для перемежителя. Длина C цикла может определяться на основе того, меньше ли K 1024 битов. Кроме того, величина запоминающего устройства параметров для использования C=8 в сопоставлении с C=4 представляет собой только разницу в размере матрицы α и β, что является тривиальным, поэтому допускает свободу использования больших C, если необходимо.

Запоминающее средство для параметра 105 перемежителя может хранить параметры перемежителя ARP, используя значения K', C, P 0, α(·) и β(·), которые берутся, по меньшей мере, из одной строки таблицы 1. Перемежитель 201 может использовать перемежитель ARP со значениями K', C, P 0, α(·) и β(·), которые берутся, по меньшей мере, из одной строки следующей таблицы:

| Таблица 1.Параметры набора перемежителей ARP, определенных для LTE. Постоянное смещение A=0 используется для всех размеров. Перечислены возможные параллельности М, использующие естественно параллельные окна, меньшие или равные 32 | ||||||

| K_info | K | C | P 0 | Индекс а | Индекс b | Доступная параллельность |

| 40 | 40 | 4 | 41 | 1 | 6 | 1,2,5,10 |

| 52 | 56 | 4 | 13 | 1 | 1 | 1,2,7,14 |

| 67 | 72 | 4 | 13 | 1 | 4 | 1,2,3,6,9,18 |

| 87 | 88 | 4 | 75 | 2 | 3 | 1,2,11,22 |

| 99 | 104 | 4 | 23 | 1 | 1 | 1,2,3,26 |

| 113 | 120 | 4 | 73 | 1 | 8 | 1,2,3,5,6,10,15,30 |

| 129 | 136 | 4 | 11 | 1 | 6 | 1,2,17 |

| 146 | 152 | 4 | 129 | 1 | 5 | 1,2,19 |

| 167 | 168 | 4 | 25 | 1 | 4 | 1,2,3,6,7,14,21 |

| 190 | 192 | 4 | 43 | 1 | 1 | 1,2,3,4,6,8,12,16,24 |