Устройство управляемой перестановки битов бинарной строки

Иллюстрации

Показать всеУстройство относится к области кодирования информации и может быть использовано в системах защиты информации от несанкционированного доступа. Техническим результатом является ускорение процесса управляемой перестановки бит исходной строки данных длиной N за счет параллельного выполнения преобразования за один такт генератора тактовых импульсов и двойной буферизации данных. Устройство содержит блок регистров кодов битовой транспозиции и две группы идентичных блоков, каждая из которых содержит последовательно соединенные через шины данных регистр исходной строки, дешифратор битовой транспозиции, блок сборки битовой транспозиции и регистр результирующей строки. 3 ил.

Реферат

Устройство относится к области кодирования информации и может быть использовано в системах защиты информации от несанкционированного доступа.

Известны устройства, обеспечивающие генерацию перестановок исходных величин (см., например, авт.св. СССР №№957215, 995093, 1124319, 1180917, 1190388, 1397933 и др.). Недостатком этих устройств является невозможность управления перестановками.

Известно устройство, обеспечивающее генерацию управляемых перестановок (авт.св. СССР №1410056, МПК G05F 15/20). Данное устройство реализует процедуру преобразования номера перестановки в однозначно соответствующую ему перестановку. Недостатком устройства является невысокая скорость выполнения заданной перестановки.

Известен дешифратор управляемой побитовой транспозиции информации, хранимой в персональной ЭВМ (см. патент РФ №2320000, МПК G06F 7/76).

Однако он работает в последовательном режиме, осуществляет преобразование N-разрядной строки за N-тактов и не обладает необходимым быстродействием.

Наиболее близким к заявляемому является устройство, реализующее процедуру управляемой перестановки исходных данных (см. патент РФ №2012054, МПК G06F 15/419, G06F 15/20), содержащее группу блоков деления, блок выбора минимального числа, две группы регистров, группу сумматоров, первый и второй элементы ИЛИ, регистр, дешифратор и две группы элементов задержки, введены регистр, первый и второй демультиплексоры, две группы элементов ИЛИ, группа элементов задержки, группа первого и второго элементов И, группа триггеров, регистр и дешифратор. При этом информационный выход введенного регистра соединен с информационным входом дешифратора и управляющими входами демультиплексоров, информационный вход первого демультиплексора соединен с входом запуска устройства, а его выходы соединены с входами соответствующих элементов ИЛИ первой группы, информационный вход второго демультиплексора соединен с выходом регистра, а его выходы соединены с входами соответствующих элементов ИЛИ второй группы, выходы элементов ИЛИ первой группы соединены с входами элементов задержки первой группы, а выходы элементов ИЛИ второй группы соединены с информационными входами блоков деления, выходы дешифратора соединены с входом первого элемента и инверсным входом второго элемента группы, другие входы элементов И объединены со считывающим входом соответствующих сумматоров и входами записи регистров группы и соединены с выходом соответствующего элемента задержки третьей группы, вход которых соединен с выходом соответствующего элемента задержки второй группы, входы которых соединены с выходом второго элемента И группы, а выходы первых элементов И группы соединены с входами первого элемента ИЛИ, выход элемента ИЛИ соединен с объединенными нулевыми входами триггеров, инверсные выходы которых соединены со считывающими входами регистров группы, а единичные входы - с выходами дешифратора, информационные выходы регистров группы соединены с входами блока выбора минимального числа.

Работа устройства основана на реализации процедуры преобразования исходного числа m в однозначно соответствующую ему перестановку исходных, предварительно пронумерованных числами 1, 2, …, k элементов.

Недостатком устройства является невысокая скорость выполнения заданной перестановки.

Задачей настоящего решения является ускорение процесса управляемой перестановки бит (a1, a, …, ai, … aN) исходной строки данных длиной N за счет параллельного выполнения преобразования за один такт генератора тактовых импульсов и двойной буферизации данных.

Техническим результатом является возможность высокоскоростной перестановки данных с использованием управляющих кодов.

Поставленная задача решается тем, что устройство управляемой перестановки битов бинарных строк содержит блок регистров кодов битовой транспозиции и две группы идентичных блоков, каждая из которых содержит последовательно электрически соединенные через шины данных регистр исходной строки, дешифратор битовой транспозиции, блок сборки битовой транспозиции и регистр результирующей строки, при этом блок регистров кодов битовой транспозиции содержит первую и вторую группы регистров для параллельной записи с внешнего устройства памяти и хранения управляющих кодов дешифраторов битовой транспозиции первой и второй групп, регистры исходных строк первой и второй группы имеют входы для параллельной записи данных с внешнего устройства при установке разрешающего сигнала установки каждого из регистров, блоки сборки битовой транспозиции первой и второй групп имеют также входы тактовых импульсов от внешних генераторов и входы разрешения установки регистров результирующих строк первой и второй группы и соединены дополнительными шинами данных с регистром результирующей строки другой группы для управляемой замены результирующих строк местами.

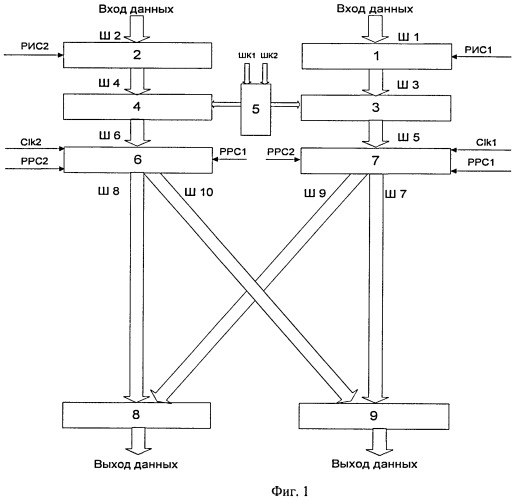

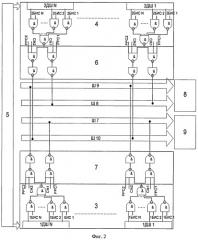

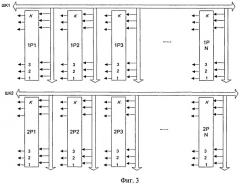

Изобретение поясняется чертежами, на фиг.1 приведена блок-схема устройства, на фиг.2 приведена логическая схема устройства, на фиг.3 приведена схема блока регистров кодов битовой транспозиции, где

1 - регистр исходной строки первой группы;

2 - регистр исходной строки второй группы;

3 - дешифратор битовой транспозиции первой группы;

4 - дешифратор битовой транспозиции второй группы;

5 - блок регистров кодов битовой транспозиции;

6 - блок сборки битовой транспозиции второй группы;

7 - блок сборки битовой транспозиции первой группы;

8 - регистр результирующей строки второй группы;

9 - регистр результирующей строки первой группы;

РИС1 - сигнал разрешения установки регистра исходной строки первой группы;

РИС2 - сигнал разрешения установки регистра исходной строки второй группы;

РРС1 - сигнал разрешения установки регистра результирующей строки первой группы;

РРС2 - сигнал разрешения установки регистра результирующей строки второй группы;

Clk1 - сигнал от внешнего генератора тактовых импульсов для тактирования блока сборки битовой транспозиции первой группы;

Clk2 - сигнал от внешнего генератора тактовых импульсов для тактирования блока сборки битовой транспозиции второй группы;

& - логический элемент;

1БИС 1-1БИС N - биты исходной строки первой группы (N - длина строки);

2БИС 1-2БИC N - биты исходной строки второй группы;

1P1-1PN - регистры хранения кодов транспозиции битов исходной строки первой группы;

2P1-2PN - регистры хранения кодов транспозиции битов исходной строки второй группы;

1ДШ 1-1ДШ N - дешифраторы переадресации первой группы;

2ДШ 1-2ДШ N - дешифраторы переадресации второй группы;

ШК1 - шина параллельной записи управляющих кодов в блок регистров кодов битовой транспозиции для дешифраторов битовой транспозиции первой группы;

ШК2 - шина параллельной записи управляющих кодов в блок регистров кодов битовой транспозиции для дешифраторов битовой транспозиции второй группы;

Ш1-Ш10 - шины параллельной передачи данных.

Предлагаемое устройство состоит из блока регистров кодов битовой транспозиции 5, предназначенного для хранения кодов текущей перестановки, и двух групп идентичных блоков последовательно электрически соединенных через шины данных. Первая группа содержит регистр исходной строки 1, в который записывается исходная строка бит данных (a1, a, …, ai, … aN) по сигналу РИС1, дешифратор битовой транспозиции 3, осуществляющий перестановку бит исходной строки в соответствии с текущими кодами регистров хранения кодов транспозиции битов исходной строки первой группы, входящих в состав блока регистров кодов битовой транспозиции 5, блок сборки битовой транспозиции 7, принимающий перестановленные биты от блока дешифрации, и регистр результирующей строки 9, в который по сигналу внешнего тактового генератора записывается перестановка исходной строки битов регистра 1, если установлен сигнал РРС1, или регистра 2, если установлен сигнал РРС2. Вторая группа идентичных блоков содержит регистр исходной строки 2, дешифратор битовой транспозиции 4, блок сборки битовой транспозиции 6 и регистр результирующей строки 8.

При этом блок регистров кодов битовой транспозиции 5 одной группой выходов соединен с шинами кодов дешифратора битовой транспозиции первой группы 3, а другой группой выходов соединен с шинами кодов дешифраторов битовой транспозиции второй группы 4, блок сборки битовой транспозиции первой группы 7 соединен дополнительной шиной данных с регистром результирующей строки второй группы 8, а блок сборки битовой транспозиции второй группы 6 соединен дополнительной шиной данных с регистром результирующей строки первой группы 9.

Возможная схема блока регистров кодов битовой транспозиции приведена на фиг.3. Блок регистров кодов битовой транспозиции используется для хранения поразрядных форматирующих функций для управления битовыми транспозициями исходных строк.

Блок регистров кодов битовой транспозиции содержит 2 группы из N К-разрядных (K=log2N) регистров 1Р1, 1Р2, 1Р3, …, 1PN и 2Р1, 2Р2, 2Р3, …, 2PN. Каждый из указанных регистров имеет вход параллельной записи управляющих кодов. Запись в каждую группу регистров может осуществляться независимо через шины ШК1, ШК2. Код, записываемый в каждый из регистров первой или второй группы, должен быть уникален в этой группе.

Устройство работает следующим образом. Перед началом осуществления цикла перестановок в блок регистров кодов битовой транспозиции через шины параллельной записи заносятся управляющие коды дешифраторов битовой транспозиции первой и второй групп. По сигналу РИС1 исходная строка (a1, a, …, ai, … aN) длиной N бит с внешней шины данных записывается в регистр 1. Независимо, по сигналу РИС2 с внешней шины данных в регистр 2 записывается другая исходная строка.

На один вход логических элементов 2И-НЕ, входящих в блоки дешифраторов битовой транспозиции первой группы подается значение соответствующего бита исходной строки (1БИС 1-1БИС N) от регистра исходной строки первой группы (фиг.2). На второй вход этих логических элементов подается сигнал переадресации. Сигналы переадресации для каждого бита формируются дешифраторами переадресации 1ДШ 1-1ДШ N, имеющими К битовых входов и N битовых выходов и входящими в дешифратор битовой транспозиции первой группы. На входы дешифраторов переадресации подаются сигналы регистров хранения кодов транспозиции битов исходной строки первой группы, входящих в состав блока регистров кодов битовой транспозиции 5. На соответствующем выходе дешифраторов переадресации образуется высокий уровень. В результате, на выходе элемента И-НЕ с N-входами появляется сигнал БИС с порядковым номером, соответствующим управляющему коду, поступающему на дешифратор с блока регистров кодов битовой транспозиции 5. Если сигнал РРС1 имеет высокий логический уровень, а сигнал РРС2 имеет низкий логический уровень, то по сигналу Clk1 перестановка исходной строки данных записывается в регистр результирующей строки первой группы 9. Если сигнал РРС1 имеет низкий логический уровень, а сигнал РРС2 высокий логический уровень, то по сигналу Clk2 перестановка исходной строки данных записывается в регистр результирующей строки второй группы 8.

Работа второй группы блоков 2, 4, 6 аналогична работе первой группы блоков 1, 3, 7. На один вход логических элементов 2И-НЕ, входящих в блоки дешифраторов битовой транспозиции второй группы подается значение соответствующего бита исходной строки (2БИС 1-2БИС N) от регистра исходной строки второй группы (фиг.2). На второй вход этих логических элементов подается сигнал переадресации. Сигналы переадресации для каждого бита формируются дешифраторами переадресации 2ДШ 1-2ДШ N, имеющими К битовых входов и N битовых выходов и входящими в дешифратор битовой транспозиции второй группы. На входы дешифраторов переадресации подаются сигналы регистров хранения кодов транспозиции битов исходной строки второй группы, входящих в состав блока регистров кодов битовой транспозиции 5. На соответствующем выходе дешифраторов переадресации образуется высокий уровень. В результате, на выходе элемента И-НЕ с N-входами появляется сигнал БИС с порядковым номером, соответствующим управляющему коду, поступающему на дешифратор с блока регистров кодов битовой транспозиции 5. Если сигнал РРС1 имеет высокий логический уровень, а сигнал РРС2 низкий логический уровень, то по сигналу Clk2 перестановка исходной строки данных записывается в регистр результирующей строки второй группы 8. Если сигнал РРС1 имеет низкий логический уровень, а сигнал РРС2 высокий логический уровень, то по сигналу Clk2 перестановка исходной строки данных записывается в регистр результирующей строки первой группы 9.

Сигналы РРС1 и РРС2 управляют перестановкой строк на выходе устройства. Если сигнал РРС1 имеет высокий логический уровень, а сигнал РРС2 низкий логический уровень, порядок входных строк совпадает с порядком выходных строк. Если сигнал РРС1 имеет низкий логический уровень, а сигнал РРС2 высокий логический уровень, то пары выходных строк имеют обратный порядок парам входных строк. Если РРС1 и РРС2 имеют низкий логический уровень, возникает пропуск тактовых импульсов и задержка в работе устройства.

Таким образом, перестановка выполняется за один такт внешнего генератора тактовых импульсов. Это дает возможность осуществить высокоскоростной обмен данными между внешними устройствами с одновременным выполнением управляемой перестановки исходных строк данных местами, что может быть использовано в системах защиты информации.

Устройство управляемой перестановки битов бинарных строк, характеризующееся тем, что содержит блок регистров кодов битовой транспозиции и две группы идентичных блоков, каждая из которых содержит последовательно электрически соединенные через шины данных регистр исходной строки, дешифратор битовой транспозиции, блок сборки битовой транспозиции и регистр результирующей строки, при этом блок регистров кодов битовой транспозиции содержит первую и вторую группы регистров для параллельной записи с внешнего устройства памяти и хранения управляющих кодов дешифраторов битовой транспозиции первой и второй групп, регистры исходных строк первой и второй группы имеют входы для параллельной записи данных с внешнего устройства при установке разрешающего сигнала установки каждого из регистров, блоки сборки битовой транспозиции первой и второй групп имеют также входы тактовых импульсов от внешних генераторов и входы разрешения установки регистров результирующих строк первой и второй группы и соединены дополнительными шинами данных с регистром результирующей строки другой группы для управляемой замены результирующих строк местами.