Дифференциальный операционный усилитель с парафазным выходом

Иллюстрации

Показать всеИзобретение относится к области радиотехники и связи и может быть использовано в качестве устройства усиления аналоговых сигналов, в структуре аналоговых микросхем различного функционального назначения. Технический результат заключается в создании условий, при которых выходное статическое синфазное напряжение ДУ будет иметь высокую стабильность и нулевое значение. Дифференциальный операционный усилитель с парафазным выходом содержит входной дифференциальный каскад, первый и второй выходные транзисторы, с первого по третий токостабилизирующие двухполюсники, первый и второй двухполюсники коллекторной нагрузки, с первого по четвертый дополнительные транзисторы, первый и второй резисторы обратной связи. 1 з.п. ф-лы, 8 ил.

Реферат

Изобретение относится к области радиотехники и связи и может быть использовано в качестве устройства усиления аналоговых сигналов, в структуре аналоговых микросхем различного функционального назначения (например, решающих усилителях (ОУ), компараторах, мостовых усилителях мощности и т.п.).

Известны схемы классических двухкаскадных дифференциальных операционных усилителей (ДУ) с парафазным выходом, которые стали основой многих серийных аналоговых микросхем [1-12].

Кроме того, ДУ данного класса активно применяются в структуре СВЧ-устройств, реализованных на базе новейших SiGe-технологий. Это связано с возможностью построения на их основе активных RC-фильтров гигагерцового диапазона для современных и перспективных систем связи, мостовых усилителей мощности.

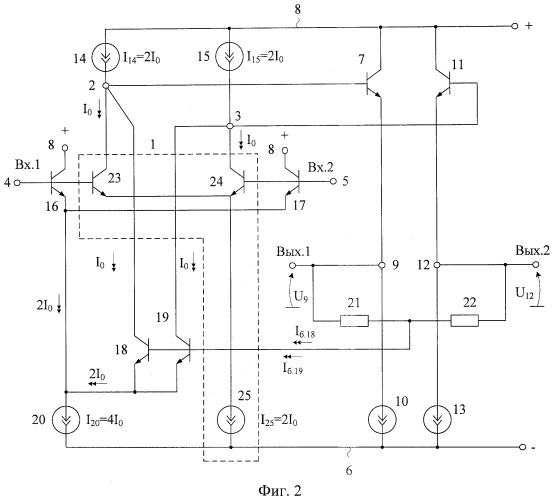

Ближайшим прототипом (фиг.1) заявляемого устройства является дифференциальный усилитель, описанный в патентной заявке US 2006/0038616 fig.1, содержащий входной дифференциальный каскад 1 с первым 2 и вторым 3 токовыми выходами, а также первым 4 и вторым 5 входами, являющимися входами устройства, шину первого 6 источника питания, связанную с общей эмиттерной цепью входного дифференциального каскада 1, первый 7 выходной транзистор, база которого соединена с первым 2 токовым выходом входного дифференциального каскада 1, коллектор подключен к шине второго 8 источника питания, а эмиттер связан с первым 9 вспомогательным выходом устройства и через первый 10 токостабилизирующий двухполюсник соединен с шиной первого 6 источника питания, второй 11 выходной транзистор, база которого соединена со вторым 3 токовым выходом входного дифференциального каскада 1, коллектор подключен к шине второго 8 источника питания, а эмиттер связан со вторым 12 вспомогательным выходом устройства и через второй 13 токостабилизирующий двухполюсник соединен с шиной первого 6 источника питания, первый 14 двухполюсник коллекторной нагрузки, включенный между первым 2 токовым выходом входного дифференциального каскада 1 и шиной второго 8 источника питания, второй 15 двухполюсник коллекторной нагрузки, включенный между вторым 3 токовым выходом входного дифференциального каскада 1 и шиной второго 8 источника питания.

Основная задача предлагаемого изобретения состоит в создании условий, при которых выходное статическое синфазное напряжение ДУ будет иметь высокую стабильность и нулевое значение.

Поставленная задача решается тем, что в дифференциальном операционном усилителе с парафазным выходом фиг.1, содержащем входной дифференциальный каскад 1 с первым 2 и вторым 3 токовыми выходами, а также первым 4 и вторым 5 входами, являющимися входами устройства, шину первого 6 источника питания, связанную с общей эмиттерной цепью входного дифференциального каскада 1, первый 7 выходной транзистор, база которого соединена с первым 2 токовым выходом входного дифференциального каскада 1, коллектор подключен к шине второго 8 источника питания, а эмиттер связан с первым 9 вспомогательным выходом устройства и через первый 10 токостабилизирующий двухполюсник соединен с шиной первого 6 источника питания, второй 11 выходной транзистор, база которого соединена со вторым 3 токовым выходом входного дифференциального каскада 1, коллектор подключен к шине второго 8 источника питания, а эмиттер связан со вторым 12 вспомогательным выходом устройства и через второй 13 токостабилизирующий двухполюсник соединен с шиной первого 6 источника питания, первый 14 двухполюсник коллекторной нагрузки, включенный между первым 2 токовым выходом входного дифференциального каскада 1 и шиной второго 8 источника питания, второй 15 двухполюсник коллекторной нагрузки, включенный между вторым 3 токовым выходом входного дифференциального каскада 1 и шиной второго 8 источника питания, предусмотрены новые элементы и связи - в схему введены первый 16, второй 17, третий 18 и четвертый 19 дополнительные транзисторы, эмиттеры которых связаны друг с другом и через третий 20 токостабилизирующий двухполюсник связаны с шиной первого 6 источника питания, коллекторы первого 16 и второго 17 дополнительных транзисторов объединены и подключены к шине второго 8 источника питания, база первого 16 дополнительного транзистора связана с первым 4 входом входного дифференциального каскада, являющимся входом устройства, база второго 17 дополнительного транзистора связана со вторым 5 входом входного дифференциального каскада, являющимся входом устройства, коллектор третьего 18 дополнительного транзистора подключен к базе второго 7 выходного транзистора, коллектор четвертого 19 дополнительного транзистора соединен с базой второго 11 выходного транзистора, причем первый 9 вспомогательный выход устройства соединен с базами третьего 18 и четвертого 19 дополнительных транзисторов через первый 21 резистор обратной связи, а второй 12 вспомогательный выход устройства соединен с базами третьего 18 и четвертого 19 дополнительных транзисторов через второй 22 резистор обратной связи.

На фиг.1 показана схема ДУ-прототипа.

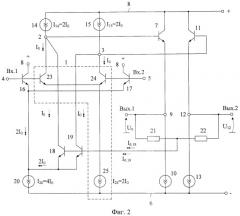

На фиг.2 показана схема заявляемого устройства в соответствии с п.1 формулы изобретения.

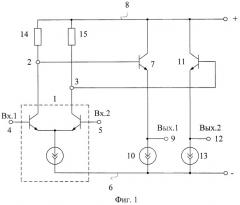

На фиг.3 показана схема заявляемого устройства в соответствии с п.2 формулы изобретения.

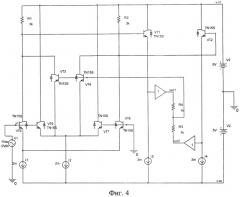

На фиг.4 представлена схема фиг.3 в среде компьютерного моделирования PSpice на моделях интегральных транзисторов ФГУП НПП «Пульсар».

На фиг.5 показана частотная зависимость коэффициента усиления по напряжению ОУ фиг.4, а на фиг.6 - временные зависимости напряжений на выходах ОУ фиг.4 при входном напряжении 20 мВ.

На фиг.7 приведена схема драйвера дифференциальной линии связи на основе ДУ фиг.3 с элементами общей отрицательной обратной связи резисторами (R5, R8, R6, R7).

График фиг.8 показывает частотную зависимость коэффициента усиления по напряжению драйвера дифференциальной линии связи фиг.7.

Дифференциальный операционный усилитель с парафазным выходом фиг.2 содержит входной дифференциальный каскад 1 с первым 2 и вторым 3 токовыми выходами, а также первым 4 и вторым 5 входами, являющимися входами устройства, шину первого 6 источника питания, связанную с общей эмиттерной цепью входного дифференциального каскада 1, первый 7 выходной транзистор, база которого соединена с первым 2 токовым выходом входного дифференциального каскада 1, коллектор подключен к шине второго 8 источника питания, а эмиттер связан с первым 9 вспомогательным выходом устройства и через первый 10 токостабилизирующий двухполюсник соединен с шиной первого 6 источника питания, второй 11 выходной транзистор, база которого соединена со вторым 3 токовым выходом входного дифференциального каскада 1, коллектор подключен к шине второго 8 источника питания, а эмиттер связан со вторым 12 вспомогательным выходом устройства и через второй 13 токостабилизирующий двухполюсник соединен с шиной первого 6 источника питания, первый 14 двухполюсник коллекторной нагрузки, включенный между первым 2 токовым выходом входного дифференциального каскада 1 и шиной второго 8 источника питания, второй 15 двухполюсник коллекторной нагрузки, включенный между вторым 3 токовым выходом входного дифференциального каскада 1 и шиной второго 8 источника питания. В схему введены первый 16, второй 17, третий 18 и четвертый 19 дополнительные транзисторы, эмиттеры которых связаны друг с другом и через третий 20 токостабилизирующий двухполюсник связаны с шиной первого 6 источника питания, коллекторы первого 16 и второго 17 дополнительных транзисторов объединены и подключены к шине второго 8 источника питания, база первого 16 дополнительного транзистора связана с первым 4 входом входного дифференциального каскада, являющимся входом устройства, база второго 17 дополнительного транзистора связана со вторым 5 входом входного дифференциального каскада, являющимся входом устройства, коллектор третьего 18 дополнительного транзистора подключен к базе второго 7 выходного транзистора, коллектор четвертого 19 дополнительного транзистора соединен с базой второго 11 выходного транзистора, причем первый 9 вспомогательный выход устройства соединен с базами третьего 18 и четвертого 19 дополнительных транзисторов через первый 21 резистор обратной связи, а второй 12 вспомогательный выход устройства соединен с базами третьего 18 и четвертого 19 дополнительных транзисторов через второй 22 резистор обратной связи.

В качестве первого 10, второго 13 и третьего 20 токостабилизирующих двухполюсников авторы рекомендуют использовать классические источники опорного тока на транзисторах или сравнительно высокоомные резисторы.

Первый 14 и второй 15 двухполюсники коллекторной нагрузки реализуются на основе сравнительно высокоомных резисторов либо в виде источников опорного тока на p-n-p транзисторах, если их применение допускается.

На фиг.2 входной дифференциальный каскад 1 реализован на транзисторах 23, 24 и классическом источнике опорного тока 25.

На фиг.3, в соответствии с п.2 формулы изобретения, первый 9 вспомогательный выход устройства связан с базами третьего 18 и четвертого 19 дополнительных транзисторов через последовательно соединенные первый 26 дополнительный буферный усилитель и первый 21 резистор обратной связи, а второй 12 вспомогательный выход устройства связан с базой третьего 18 и четвертого 19 дополнительных транзисторов через последовательно соединенные второй 27 дополнительный буферный усилитель и второй 22 резистор обратной связи.

Рассмотрим работу ДУ фиг.2.

Статический режим по току транзисторов предлагаемого ДУ устанавливается двухполюсниками 14, 15, 20, 25, 10 и 13:

где Iкi - коллекторный ток i-го транзистора.

В соответствии со вторым законом Кирхгофа статические напряжения на вспомогательных выходах 9 и 12:

где Uэб.17=Uэб.16=Uэб.19=Uэб.18 - напряжения «эмиттер-база» транзисторов 17, 16, 19 и 18;

Iб.18=Iб.19 - токи базы дополнительных транзисторов 18 и 19.

Если выбрать R21=R22, ТО:

С учетом типовых численных значений Iб.18=Iб.19 и R21=R22 практических схем ДУ из уравнения (3) можно сделать вывод о том, что в заявляемом ДУ статические выходные напряжения U9=U12 близки к единицам милливольт.

Графики фиг.6 показывают, что в схемах ДУ фиг.2 диапазон изменения uвых при низковольтном питании (±2 В) лежит в пределах ±1 В. При этом коэффициент усиления по напряжению ДУ при использовании резисторов в качестве двухполюсников коллекторной нагрузки 14 и 15 более 40 дБ (фиг.5).

В схеме фиг.3. которая отличается от схемы фиг.2 наличием буферных усилителей 26 и 27, значительно снижаются требования к величине сопротивлений резисторов обратной связи 21 и 22, что позволяет получить на выходах Вых.*1 и Вых.*2 нулевые уровни статических напряжений независимо от статических параметров дополнительных буферных усилителей 26 и 27. Однако в схеме фиг.3, соответствующей п.2 формулы изобретения, в низкоомной нагрузке, включенной между выходами Вых.*1 и Вых.*2, могут быть получены значительно большие мощности, которые определяются свойствами буферных усилителей 26 и 27. Кроме этого в архитектуре рис.3 максимальные амплитуды выходных напряжений положительной и отрицательной полярностей близки к сумме напряжений первого 6 и второго 8 источников питания.

Таким образом, заявляемый дифференциальный операционный усилитель имеет нулевой уровень выходного синфазного напряжения. Это весьма существенно для его согласования с последующими функциональными узлами различных систем на кристалле, а также для получения боле широкого диапазона изменения выходных противофазных напряжений.

Источники информации

1. Патентная заявка США №2009/108882, fig.3.

2. Патентная заявка США №2005/0088232, fig.1.

3. Патент Франции №2409640, fig.1.

4. Патентная заявка США №2009/0221259, fig.13.

5. Патентная заявка США №2005/0200414.

6. Патент США №4.680.553, fig.13.

7. Патентная заявка США №2004/0046592, fig.2.

8. Патент США №4.276.485, fig.1.

9. Патент JP №54079553, fig.1.

10. Патент GB №2008883, fig.l.

11. Патент США №6.462.618.

12. Патентная заявка США №2005/0110571, fig.6, fig.7.

1. Дифференциальный операционный усилитель с парафазным выходом, содержащий входной дифференциальный каскад (1) с первым (2) и вторым (3) токовыми выходами, а также первым (4) и вторым (5) входами, являющимися входами устройства, шину первого (6) источника питания, связанную с общей эмиттерной цепью входного дифференциального каскада (1), первый (7) выходной транзистор, база которого соединена с первым (2) токовым выходом входного дифференциального каскада (1), коллектор подключен к шине второго (8) источника питания, а эмиттер связан с первым (9) вспомогательным выходом устройства и через первый (10) токостабилизирующий двухполюсник соединен с шиной первого (6) источника питания, второй (11) выходной транзистор, база которого соединена со вторым (3) токовым выходом входного дифференциального каскада (1), коллектор подключен к шине второго (8) источника питания, а эмиттер связан со вторым (12) вспомогательным выходом устройства и через второй (13) токостабилизирующий двухполюсник соединен с шиной первого (6) источника питания, первый (14) двухполюсник коллекторной нагрузки, включенный между первым (2) токовым выходом входного дифференциального каскада (1) и шиной второго (8) источника питания, второй (15) двухполюсник коллекторной нагрузки, включенный между вторым (3) токовым выходом входного дифференциального каскада (1) и шиной второго (8) источника питания, отличающийся тем, что в схему введены первый (16), второй (17), третий (18) и четвертый (19) дополнительные транзисторы, эмиттеры которых связаны друг с другом и через третий (20) токостабилизирующий двухполюсник связаны с шиной первого (6) источника питания, коллекторы первого (16) и второго (17) дополнительных транзисторов объединены и подключены к шине второго (8) источника питания, база первого (16) дополнительного транзистора связана с первым (4) входом входного дифференциального каскада, являющимся входом устройства, база второго (17) дополнительного транзистора связана со вторым (5) входом входного дифференциального каскада, являющимся входом устройства, коллектор третьего (18) дополнительного транзистора подключен к базе второго (7) выходного транзистора, коллектор четвертого (19) дополнительного транзистора соединен с базой второго (11) выходного транзистора, причем первый (9) вспомогательный выход устройства соединен с базами третьего (18) и четвертого (19) дополнительных транзисторов через первый (21) резистор обратной связи, а второй (12) вспомогательный выход устройства соединен с базами третьего (18) и четвертого (19) дополнительных транзисторов через второй (22) резистор обратной связи.

2. Дифференциальный операционный усилитель с парафазным выходом по п.1, отличающийся тем, что первый (9) вспомогательный выход устройства связан с базами третьего (18) и четвертого (19) дополнительных транзисторов через последовательно соединенные первый (26) дополнительный буферный усилитель и первый (21) резистор обратной связи, а второй (12) вспомогательный выход устройства связан с базой третьего (18) и четвертого (19) дополнительных транзисторов через последовательно соединенные второй (27) дополнительный буферный усилитель и второй (22) резистор обратной связи.