Каскодный дифференциальный усилитель с повышенным коэффициентом усиления

Иллюстрации

Показать всеИзобретение относится к области радиотехники и связи и может быть использовано в качестве устройства усиления аналоговых сигналов, в структуре аналоговых микросхем различного функционального назначения. Технический результат заключается в повышении предельных значений коэффициента усиления по напряжению ДУ при низковольтном питании. Каскодный дифференциальный усилитель с повышенным коэффициентом усиления содержит входной дифференциальный каскад, с первого по четвертый выходные транзисторы, цепь смещения потенциалов, первый и второй стабилизирующие двухполюсники, первый и второй двухполюсники коллекторной нагрузки, дополнительный транзистор. 2 з.п. ф-лы, 6 ил.

Реферат

Изобретение относится к области радиотехники и связи и может быть использовано в качестве устройства усиления аналоговых сигналов, в структуре аналоговых микросхем различного функционального назначения (например, SiGe-операционных усилителях (ОУ), СВЧ-усилителях, компараторах, непрерывных стабилизаторах напряжения и т.п.).

В современной микроэлектронике находят применение классические каскодные дифференциальные операционные усилители (ДУ) с резисторами в коллекторной цепи выходных транзисторов [1-9]. Данная архитектура является основой широкого класса аналоговых и цифровых устройств. Причем применение резисторов (или неуправляемых активных нагрузок) в ряде случаев является обязательным техническим решением для таких ДУ [6].

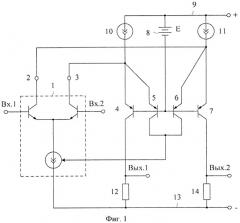

Наиболее близким по технической сущности к заявляемому устройству является дифференциальный усилитель по патенту RU 2384936, фиг.1.

Существенный недостаток известного ДУ, архитектура которого присутствует также в других усилительных каскадах [7-9], состоит в том, что при ограничениях на напряжение питания (Еп), характерных для SiGe технологических процессов (Еп≤2,0÷2,5 В), его коэффициент усиления по напряжению (Ку) получается небольшим (Куmax=10÷20). В первую очередь это обусловлено ограничениями на сопротивления резисторов коллекторной нагрузки выходного «перегнутого» каскода, которые из-за малых Еп не могут выбираться высокоомными.

Таким образом, при малых напряжениях питания, а особенно в тех случаях, когда требуется получить более-менее значительные амплитуды выходного напряжения, известные схемотехнические решения ДУ не эффективны.

Основная задача предлагаемого изобретения состоит в повышении предельных значений коэффициента усиления по напряжению ДУ при низковольтном питании.

Поставленная задача решается тем, что в каскодном дифференциальном операционном усилителе (ДУ), фиг.1, содержащем входной дифференциальный каскад 1 с первым 2 и вторым 3 токовыми выходами, первый 4, второй 5, третий 6, четвертый 7 выходные транзисторы, объединенные базы которых через цепь смещения потенциалов 8 соединены с первым 9 источником питания, первый 10 токостабилизирующий двухполюсник, включенный между вторым 3 токовым выходом входного дифференциального каскада 1, связанным с эмиттерами первого 4 и второго 5 выходных транзисторов и первым 9 источником питания, второй 11 токостабилизирующий двухполюсник, включенный между первым 2 токовым выходом входного дифференциального каскада 1, связанным с эмиттерами третьего 6 и четвертого 7 выходных транзисторов и первым 9 источником питания, первый 12 двухполюсник коллекторной нагрузки, включенный между коллектором второго 5 выходного транзистора, связанным с выходом устройства и вторым 13 источником питания, связанным также с эмиттерной цепью первого 1 входного дифференциального каскада, второй 14 двухполюсник коллекторной нагрузки, включенный между коллектором четвертого 7 выходного транзистора, источником питания, предусмотрены новые элементы и связи - введен дополнительный транзистор 15, база которого соединена с коллекторами третьего 6 и четвертого 7 выходных транзисторов, эмиттер подключен к объединенным базам первого 4, второго 5, третьего 6 и четвертого 7 выходных транзисторов, коллектор связан с коллектором второго 5 выходного транзистора, причем коллектор первого 4 выходного транзистора соединен со вторым 13 источником питания, связанным также с эмиттерной цепью первого 1 входного дифференциального каскада.

На чертеже фиг.1 показана схема ДУ-прототипа.

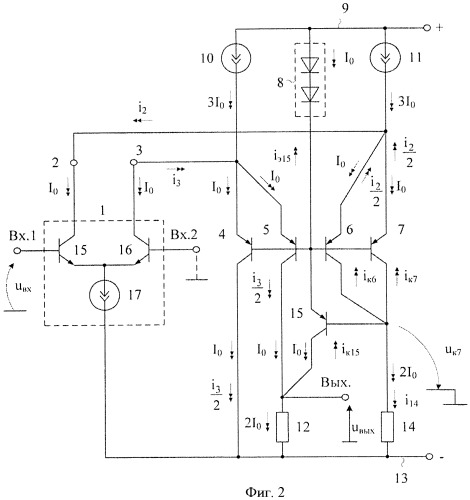

Схема заявляемого устройства, соответствующего п.1 и п.2 формулы изобретения, показана на чертеже фиг.2.

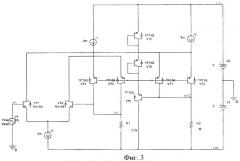

На чертеже фиг.3 представлена схема ДУ-прототипа фиг.1 с традиционной обратной связью в среде компьютерного моделирования PSpise на моделях интегральных транзисторов ФГУ НПП «Пульсар».

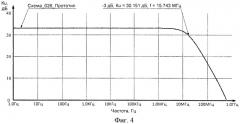

График фиг.4 характеризует частотную зависимость коэффициента усиления по напряжению (Ку) ДУ-прототипа фиг.3.

На чертеже фиг.5 показана схема фиг.2 в среде PSpise на моделях интегральных транзисторов ФГУ НПП «Пульсар», а на чертеже фит.6 - частотная зависимость ее коэффициента усиления по напряжению.

Каскодный дифференциальный усилитель с повышенным коэффициентом усиления, фиг.2, содержит входной дифференциальный каскад 1 с первым 2 и вторым 3 токовыми выходами, первый 4, второй 5, третий 6, четвертый 7 выходные транзисторы, объединенные базы которых через цепь смещения потенциалов 8 соединены с первым 9 источником питания, первый 10 токостабилизирующий двухполюсник, включенный между вторым 3 токовым выходом входного дифференциального каскада 1, связанным с эмиттерами первого 4 и второго 5 выходных транзисторов и первым 9 источником питания, второй 11 токостабилизирующий двухполюсник, включенный между первым 2 токовым выходом входного дифференциального каскада 1, связанным с эмиттерами третьего 6 и четвертого 7 выходных транзисторов и первым 9 источником питания, первый 12 двухполюсник коллекторной нагрузки, включенный между коллектором второго 5 выходного транзистора, связанным с выходом устройства и вторым 13 источником питания, связанным также с эмиттерной цепью первого 1 входного дифференциального каскада, второй 14 двухполюсник коллекторной нагрузки, включенный между коллектором четвертого 7 выходного транзистора, источником питания. В схему введен дополнительный транзистор 15, база которого связана с коллекторами третьего 6 и четвертого 7 выходных транзисторов, эмиттер подключен к объединенным базам первого 4, второго 5, третьего 6 и четвертого 7 выходных транзисторов, коллектор связан с коллектором второго 5 выходного транзистора, причем коллектор первого 4 выходного транзистора соединен со вторым 13 источником питания, связанным также с эмиттерной цепью первого 1 входного дифференциального каскада.

На чертеже фиг.2, в соответствии с п.2 формулы изобретения, цепь смещения потенциалов 8 выполнена в виде последовательно включенных прямосмещенных p-n переходов.

В соответствии с п.3 формулы изобретения, цепь смещения потенциалов 8 может быть также выполнена в виде транзисторного источника опорного напряжения с малым внутренним дифференциальным сопротивлением, например диода Видлара и т.п.

Входной дифференциальный каскад (1) на чертеже фиг.2 содержит входные транзисторы 15, 16 и источник тока 17.

В качестве первого 10 и второго 11 токостабизирующих двухполюсников могут применяться резисторы или классические транзисторные источники тока.

Статический режим по току транзисторов ДУ, фиг.2, устанавливается элементами 17, 10, 12 и 14. Если выбрать ток I17=2I0, a I10≈3I0, то статические токи эмиттеров (Iэi) и коллекторов (Iкi) транзисторов 4, 5, 6, 7 и токи двухполюсников 12, 14 и цепи смещения потенциалов 8:

где I0 - масштабный параметр статического режима, например I0=1 мА.

Таким образом, при введении транзистора 15, а также за счет подключения коллектора транзистора 15 к выходу устройства в схеме фиг.2 созданы условия, при которых эмиттерные токи транзисторов 4, 5, 6, 7, 15 одинаковы.

Рассмотрим работу ДУ, фиг.2, на переменном токе.

Положительное изменение входного напряжения uвх приводит к изменению эмиттерных токов Iэi транзисторов 15, 16, токов выходов 2 и 3 (i2, i3) и токов коллекторов (iкi) транзисторов 4, 5, 6, 7:

где rэi - сопротивление эмиттерного перехода i-го транзистора при статическом эмиттерном токе I0;

rэi=φт/I0 - дифференциальное сопротивление эмиттерного перехода i-го транзистора;

φт≈25 мВ - температурный потенциал.

Причем суммарное изменение тока во втором 14 двухполюснике коллекторной нагрузки i14=iк6+iк7≈i2.

При этом приращение коллекторного тока транзистора 15, вызванное изменением напряжения uк7 на втором 14 двухполюснике коллекторной нагрузки:

где - эквивалентное сопротивление в эмиттерной цепи дополнительного транзистора 15.

Таким образом, суммарное приращение тока через первый 12 коллекторный двухполюсник (резистор) и напряжение на нем:

В этой связи коэффициент усиления ДУ, фиг.2:

В ДУ-прототипе:

Следовательно, выигрыш по Кy, который дает предлагаемое техническое решение:

Данные теоретические выводы подтверждаются результатами сравниваемого компьютерного моделирования, фиг.4, фиг.6, которые показывают, что предлагаемый усилитель имеет более чем в 10 раз лучшее усиление.

Таким образом, в предлагаемом ДУ, фиг.2, при сравнительно низкоомных резисторах коллекторной нагрузки 12 и 14 реализуются более высокие значения коэффициента усиления по напряжению.

Заявляемая схема перспективна для использования в микроэлектронных SiGe изделиях СВЧ устройств.

Источники информации

1. Патент RU №2384936, фиг.1.

2. Патент US №4.600.893, fig.5.

3. Патент US №4.406.990, fig.3.

4. Патент US №3.579.134.

5. Патент RU №2349024, фиг.1.

6. Патент CR №7.605.658, fig.5.

7. Патент US №6.366.170.

8. Патент US №3.644.838, fig.2.

9. Патент US №4.390.850.

1. Каскодный дифференциальный усилитель с повышенным коэффициентом усиления, содержащий входной дифференциальный каскад (1) с первым (2) и вторым (3) токовыми выходами, первый (4), второй (5), третий (6), четвертый (7) выходные транзисторы, объединенные базы которых через цепь смещения потенциалов (8) соединены с первым (9) источником питания, первый (10) токостабилизирующий двухполюсник, включенный между вторым (3) токовым выходом входного дифференциального каскада (1), связанным с эмиттерами первого (4) и второго (5) выходных транзисторов и первым (9) источником питания, второй (11) токостабилизирующий двухполюсник, включенный между первым (2) токовым выходом входного дифференциального каскада (1), связанным с эмиттерами третьего (6) и четвертого (7) выходных транзисторов и первым (9) источником питания, первый (12) двухполюсник коллекторной нагрузки, включенный между коллектором второго (5) выходного транзистора, связанным с выходом устройства и вторым (13) источником питания, связанным также с эмиттерной цепью первого (1) входного дифференциального каскада, второй (14) двухполюсник коллекторной нагрузки, включенный между коллектором четвертого (7) выходного транзистора, источником питания, отличающийся тем, что в схему введен дополнительный транзистор (15), база которого связана с коллекторами третьего (6) и четвертого (7) выходных транзисторов, эмиттер подключен к объединенным базам первого (4), второго (5), третьего (6) и четвертого (7) выходных транзисторов, коллектор связан с коллектором второго (5) выходного транзистора, причем коллектор первого (4) выходного транзистора соединен со вторым (13) источником питания, связанным также с эмиттерной цепью первого (1) входного дифференциального каскада.

2. Каскодный дифференциальный усилитель с повышенным коэффициентом усиления по п.1, отличающийся тем, что цепь смещения потенциалов (8) выполнена в виде последовательно включенных прямосмещенных p-n переходов.

3. Каскодный дифференциальный усилитель с повышенным коэффициентом усиления по п.1, отличающийся тем, что цепь смещения потенциалов (8) выполнена в виде транзисторного источника опорного напряжения с малым внутренним дифференциальным сопротивлением.