Ограничитель в дополнительном коде

Иллюстрации

Показать всеИзобретение относится к электронным схемам общего назначения и может быть использовано в системах автоматического управления для ограничения сигналов в дополнительном цифровом коде, превышающих динамический диапазон, в частности в радиолокационных станциях для подавления пассивных помех. Техническим результатом является увеличение быстродействия, увеличение надежности и упрощения устройства. Устройство содержит логические элементы И, И-НЕ, ИЛИ, НЕ и коммутатор. 1 ил., 2 табл.

Реферат

Изобретение относится к электронным схемам общего назначения и может быть использовано в системах автоматического управления для ограничения сигналов в дополнительном цифровом коде, превышающих динамический диапазон, в частности в радиолокационных станциях для подавления пассивных помех.

Известны методы ограничения сигналов, такие как усечение, аппроксимация на низшем уровне, округление (В.Каппелини и др. «Цифровые фильтры и их применение», Москва, Энергоатомиздат, 1983, стр.159).

Известно устройство для преобразования динамического диапазона выходного сигнала, которое содержит квадратурный фазовращатель, корректор, квадратичные детекторы, сумматоры, аналоговые делители (а.с. СССР №1058077, кл. H04B 1/64).

Известно также устройство для преобразования динамического диапазона звукового сигнала, которое содержит квадратурный фазовращатель, аналоговые делители, квадратичные детекторы, сумматоры, блоки коррекции, вычитатель (а.с. СССР №1363489, кл. H04B 1/64).

Наиболее близким аналогом заявляемого устройства является ограничитель в дополнительном коде для цифрового тракта (заявка №2008147793), содержащий логический элемент И-НЕ, логический элемент ИЛИ, логический элемент НЕ, два логических элемента И, два коммутатора.

Данное устройство предназначено для преобразования сигналов, превышающих динамический диапазон, из (n+k)-разрядных в n-разрядные с отбрасыванием k старших и преобразованием n младших разрядов, что позволяет повысить надежность и быстродействие.

Недостатком данного устройства является то, что большое количество логических элементов, коммутаторов и связей между ними ведет к снижению быстродействия, уменьшению надежности и усложнению устройства.

Задачей, на решение которой направлено изобретение, является создание более надежного, быстродействующего и простого устройства, позволяющего преобразовать сигналы, превышающие динамический диапазон, из (n+k)-разрядных в n-разрядные с отбрасыванием k старших и преобразованием n младших разрядов.

Эта задача решается тем, что ограничитель в дополнительном коде содержит логический элемент ИЛИ, логический элемент И-НЕ, логический элемент НЕ, логический элемент 2И, коммутатор, n входов преобразуемых разрядов, k входов отбрасываемых разрядов, вход знакового разряда, выход знакового разряда, вход логической «1», n выходов преобразованных разрядов, причем n входов преобразуемых разрядов соединены соответственно с n вторыми информационными входами коммутатора, k входов отбрасываемых разрядов соединены соответственно с k первыми входами логических элементов ИЛИ и И-НЕ, вход знакового разряда соединен с входом логического элемента НЕ, выход логического элемента НЕ соединен со 2, …, n-ым входами первого информационного входа коммутатора, вход логической «1» соединен с 1-ым входом первого информационного входа коммутатора, при этом 1-ый вход первого информационного входа коммутатора является входом младшего разряда, вход знакового разряда соединен со вторыми входами логических элементов ИЛИ и И-НЕ, выход логического элемента ИЛИ соединен с первым входом логического элемента 2И, выход логического элемента И-НЕ соединен со вторым входом логического элемента 2И, выход логического элемента 2И соединен с адресным входом коммутатора.

За счет комбинационной логической схемы производится преобразование входных сигналов, превышающих динамический диапазон, из (n+k)-разрядных в n-разрядные с отбрасыванием k старших и преобразованием n младших разрядов. Сокращение количества входящих в схему элементов и связей между этими элементами позволяет создать более надежное и быстродействующее устройство.

Отличительными признаками предлагаемого изобретения является то, что вход знакового разряда соединен со вторыми входами логических элементов ИЛИ и И-НЕ, выход логического элемента ИЛИ соединен с первым входом логического элемента 2И, выход логического элемента И-НЕ соединен со вторым входом логического элемента 2И, выход логического элемента 2И соединен с адресным входом.

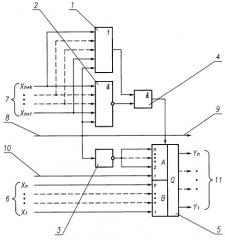

На чертеже приведена схема электрическая принципиальная ограничителя в дополнительном коде.

Устройство содержит логический элемент ИЛИ 1, логический элемент И-НЕ 2, логический элемент НЕ 3, логический элемент 2И 4, коммутатор 5, n входов преобразуемых разрядов 6, k входов отбрасываемых разрядов 7, вход знакового разряда 8, выход знакового разряда 9, вход логической «1» 10, n выходов преобразованных разрядов 11. Коммутатор 5 содержит два n-разрядных информационных входа «А» и «В», адресный вход и n-разрядный выход «Q».

Входы n преобразуемых разрядов 6 соединены соответственно с 1…n-ым вторыми информационными входами «В» коммутатора 5, входы k отбрасываемых разрядов 7 соединены соответственно с первыми k входами логических элементов ИЛИ 1 и И-НЕ 2, вход знакового разряда 8 соединен со вторыми входами логических элементов ИЛИ 1 и И-НЕ 2 и с входом логического элемента НЕ 3, выход логического элемента НЕ 3 соединен с 2…n-ым входами первого информационного входа «А» коммутатора 5, вход логической «1» соединен с 1-ым входом первого информационного входа «А» коммутатора 5, являющимся входом младшего разряда. Выход логического элемента ИЛИ 1 соединен с первым входом логического элемента 2И 4, выход логического элемента И-НЕ 2 соединен со вторым входом логического элемента 2И 4, выход логического элемента 2И 4 соединен с адресным входом коммутатора 5. Выходы 11 коммутатора 5 является выходами n преобразованных разрядов.

В таблице 1 приведено состояние выходов преобразованных разрядов 11 коммутатора 5.

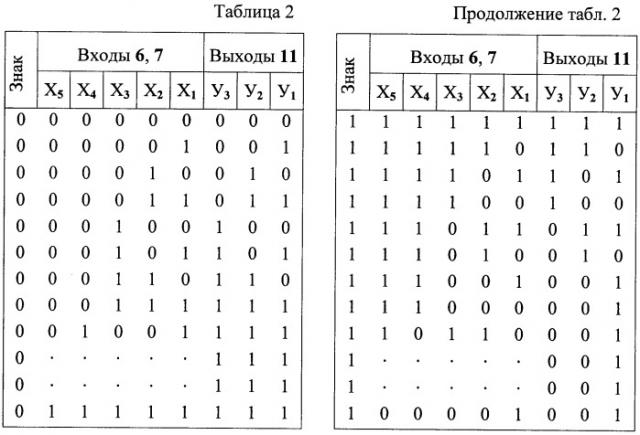

В таблице 2 приведено соответствие n входов преобразуемых разрядов 6 (X1, …, Xn), k входов отбрасываемых разрядов 7 (Xn+1, …, Xn+k) и n выходов преобразованных разрядов 11 (Y1, …, Yn) в примере исполнения при n=3 и k=2.

| Таблица 1 | |

| Адресный вход | Выход 11 |

| 1 | Первый информационный вход «А» |

| 0 | Второй информационный вход «В» |

Ограничитель в дополнительном коде работает следующим образом.

На входы преобразуемых разрядов 6 и входы отбрасываемых разрядов 7 поступает (n+k)-разрядный сигнал. На вход знакового разряда 8 поступает логический «0» или логическая «1».

Если на вход знакового разряда 8 поступает логический «0», т.е. число положительное, и хотя бы в одном из Xn+1, …, Xn+k разрядов есть логическая «1», то на выходах логического элемента ИЛИ 1, логического элемента И-НЕ 2 и логического элемента 2И 4 будет логическая «1». На выходах 11 коммутатора 5 в соответствии с табл.1 повторяется первый информационный вход «А» коммутатора 5, т.е. преобразованный сигнал будет представлен максимальным числом Хn.

Если на вход знакового разряда 8 поступает логический «0», т.е. число положительное, и во всех разрядах Xn+1, …, Xn+k логический «0», то на выходе логического элемента ИЛИ 1 будет логический «0», на выходе логического элемента И-НЕ 2 будет логическая «1», на выходе логического элемента 2И 4 будет логический «0». На выходах 11 коммутатора 5 в соответствии с табл.1 повторяется второй информационный вход «В» коммутатора 5, т.е. сигнал будет представлен числом Хn.

Если на вход знакового разряда 8 поступает логическая «1», т.е. число отрицательное, и хотя бы в одном из Xn+1, …, Xn+k разрядов есть логический «0», то на выходах логического элемента ИЛИ 1, логического элемента И-НЕ 2 и логического элемента 2И 4 будет логическая «1». На выходах 11 коммутатора 5 в соответствии с табл.1 повторяется первый информационный вход «А» коммутатора 5, т.е. преобразованный сигнал будет представлен максимальным отрицательным числом Хn.

Если на вход знакового разряда 8 поступает логическая «1», т.е. число отрицательное, и в разрядах Xn+1, …, Xn+k отсутствует логический «0», то на выходе логического элемента ИЛИ 1 будет логический «0», на выходе логического элемента И-НЕ 2 будет логическая «1», на выходе логического элемента 2И 4 будет логический «0». На выходах 11 коммутатора 5 в соответствии с табл.1 повторяется второй информационный вход «В» коммутатора 5, т.е. сигнал будет представлен числом Хn.

Таким образом, ограничитель в дополнительном коде обеспечивает преобразование сигналов, превышающих динамический диапазон, из (n+k)-разрядных в n-разрядные с отбрасыванием k старших и преобразованием n младших разрядов. При этом сокращается объем оборудования, что позволяет повысить надежность и быстродействие, а также упростить конструкцию.

Ограничитель в дополнительном коде, содержащий логический элемент ИЛИ, логический элемент И-НЕ, логический элемент НЕ, логический элемент 2И, коммутатор, n входов преобразуемых разрядов, k входов отбрасываемых разрядов, вход знакового разряда, выход знакового разряда, вход логической «1», n выходов преобразованных разрядов, причем n входов преобразуемых разрядов соединены соответственно с n вторыми информационными входами коммутатора, k входов отбрасываемых разрядов соединены соответственно с k первыми входами логических элементов ИЛИ и И-НЕ, вход знакового разряда соединен с входом логического элемента НЕ, выход логического элемента НЕ соединен со 2, …, n-м входами первого информационного входа коммутатора, вход логической «1» соединен с 1-м входом первого информационного входа коммутатора, при этом 1-й вход первого информационного входа коммутатора является входом младшего разряда, отличающийся тем, что вход знакового разряда соединен со вторыми входами логических элементов ИЛИ и И-НЕ, выход логического элемента ИЛИ соединен с первым входом логического элемента 2И, выход логического элемента И-НЕ соединен со вторым входом логического элемента 2И, выход логического элемента 2И соединен с адресным входом коммутатора.