Способ и устройство кодирования кода порождающей матрицы низкой плотности

Иллюстрации

Показать всеИзобретение касается способа и устройства кодирования кода низкоплотной порождающей матрицы. Данный способ включает в себя следующие шаги: S102, построит порождающую матрицу Gldgc из L строк N+L-K столбцов, где квадратическая матрица Gldgc (1:L, 1:L) из L строк и первых L столбцов данной матрицы является верхней или нижней треугольной матрицей, K, L, N - положительные целые числа, к тому же K<L<N; S104, добавит L-K известных заполняющих битов в последовательность информационных битов длины K, требующую кодирования, генерирует последовательность информационных битов m с длиной L; S106, в соответствии с уравнением Gldgc (1:L, l:L)=m, с помощью квадратической матрицы Gldgc (1:L, 1:L) из L строк и первых L столбцов данной матрицы, и последовательности информационных битов m длины L, порождает промежуточную переменную I, в то же время по C=I×Gldgc, производит кодирование промежуточной переменной I с использованием матрицы Gldgc, генерирует кодированную последовательность длины N+L-K; S108, удалит L-K добавленных известных битов из кодированной последовательности длины N+L-K, генерирует кодированную последовательность длины N. Технический результат - поддерживает кодирование любой длины информационного блока с оптимальными характеристиками кода. 4 н. и 11 з.п. ф-лы, 9 ил.

Реферат

Область техники

Данное изобретение относится к области коммуникации, конкретнее, связано со способом и устройством кодирования кода порождающей матрицы низкой плотности.

Уровень техники

Канал со стиранием (Erasure Channel) является важной моделью канала. Например, когда передача документов по Интернету производится с помощью пакетов, терминал-получатель обычно либо безошибочно принимает каждый пакет, либо отнюдь не принимает данного пакета. По протоколу управления передачей (Transmission Control Protocol, TCP) осуществляется механизм обнаружения ошибок и повторной передачи в случае потери пакетов, то есть применяется канал обратной связи, расположенный между вводным и выходным портами, с целью управления требующими переотправки пакетами. Терминал-получатель обнаруживает потерю пакета, порождает сигнал управления повторной передачей, пока целый пакет не получится безошибочно. После получения отправленного пакета терминал-получатель тоже порождает сигнал приема. В то же время терминал-источник следит за каждым пакетом, пока не получит обратный сигнал, а то снова отправляет данный пакет.

Служба информационного вещания, основанная на поточном режиме и режиме загрузки документов, представляет собой службу Point to Multi-Point (P2MP), не допуская обратной связи, и так что традиционный механизм обнаружения ошибок и повторной передачи здесь не работает, и требуется техника упреждающей коррекции ошибок (Forward Error Correction, FEC) для обеспечения надежной передачи. Типичные FEC коды на уровне приложений включают в себя код Рида-Соломона (Reed-Solomon codes), фонтанный код (digital fountain code) и т.д. Код Рида-Соломона обладает высокой сложностью кодирования и декодирования, обычно предназначен только для малой ширины кода. LT код (Luby Transform codes) и Raptor код являются фонтанными кодами, применимыми в практике. По сравнению с RS кодом LT код имеет линейное время кодирования и декодирования, и Raptor код применяет технику предварительного кодирования, что значительно повышает эффективность декодирования. 3GPP служба блочного мультимедийного вещания (Multimedia Broadcast / Multicast Service, MBMS) и служба цифрового видеовещания (Digital Video Broadcasting, DVB) применяют Raptor код в качестве проекта кодирования FEC кода.

Линейный блочный код представляет собой группу кодов с постоянной длиной, дается выражением в форме (n, k), обычно предназначается для упреждающей коррекции ошибок. При кодировании k информационных битов кодируются с n-разрядной длиной группы кодов. 2k кодовых слов блочного кода (n, k) образуют k -мерное пространство, так что 2k кодовых слов порождаются k линейно независимыми базисами. Если эти k базисов дается выражением в форме матрицы, тогда

Где любое слово из блочного кода (n, k) может порождаться линейной комбинацией этих базисов, то есть

Мы называем G порождающей матрицей кода. Очевидно, что каждая строка порождающей матрицы удовлетворяет только одному условию как линейной независимости (без расчета на минимальное расстояние), а базис k-мерного пространства может выбирать любой из k векторов линейной независимости, поэтому как порождающая матрица кода G не является единственной, но в независимости от того, какой вид они принимают, все эти матрицы порождают одинаковое подпространство, значит, одинаковый блочный код (n, k).

Если после кодирования первые k-разрядные слова кода одинаковы с информационным битами, то этот код называется системным. Процесс кодирования представляет собой процесс порождения k информационными битами n-разрядной длины кода, в котором осуществляется обнаружение и коррекции ошибок добавлением n-k контрольных битов.

LT код кодируется с помощью разреженности порождающей матрицы, но в сравнении с кодом порождающей матрицы низкой плотности компании Чжунсин (LDGC код), данный код не поддерживает режим кодирования системного кода, таким образом, LT код трудно удовлетворяет определенным практическим требованиям к кодированию FEC кода; и Raptor код поддерживает системный код, но требует процесса специального предкодирования, то есть требует матрицы предварительного кодирования, поэтому сложность кодирования слишком высока; а LDGC код ведет кодирование непосредственно с использованием порождающей матрицы, не требует дополнительно матрицы предварительного кодирования, в то же время при кодировании LDGC код применяет способ обратной подстановки для решения верхнего (или нижнего) тригонометрического уравнения, поэтому у него сложность кодирования значительно ниже, чем у Raptor кода. Одним словом, по сравнению с LT кодом, LDGC код отличается поддерживанием системного кода, и его сложность кодирования значительно ниже, чем у Raptor кода.

Раскрытие изобретения

Настоящее изобретение дает способ и устройство кодирования кода низкоплотной порождающей матрицы с целью обеспечивать хорошие характеристики кода, понижая его сложность кодирования.

В соответствии с одним аспектом настоящего изобретения, предлагается способ кодирования кода низкоплотной порождающей матрицы. По примеру реализации настоящего изобретения, данный способ включает в себя следующие шаги: построится порождающая матрица Gldgc из L строк и N+L-K столбцов, где квадратическая матрица Gldgc (1:L, 1:L) из L строк и первых L столбцов порождающей матрицы Gldgc является верхней или нижней треугольной матрицей, K, L, N - положительные целые числа, к тому же K<L<N; добавляются L-K известных заполняющих битов в последовательность информационных битов длины K, требующую кодирования, и порождается последовательность информационных битов m длины L; в соответствии с уравнением I×Gldgc (1:L, 1:L)=m, с помощью квадратной матрицы Gldgc (1:L, 1:L) из L строк и первых L столбцов порождающей матрицы Gldgc и последовательности информационных битов m длины L порождается промежуточная переменная I, и по уравнению С=I×Gldgc с помощью порождающей матрицы Gldgc производится кодирование промежуточной переменной I, порождается кодированная последовательность длины N+L-K; удалением L-K известных битов из кодированной последовательности длины N+L-K порождается кодированная последовательность длины N.

Где, в случае, когда квадратическая матрица Gldgc (1:L, 1:L) из L строк и первых L столбцов порождающей матрицы Gldgc является левой верхней или левой нижней треугольной матрицей, добавим L-K известных битов перед последовательностью информационных битов длины K, требующей кодирования. А в случае, когда данная матрица - правая верхняя или нижняя треугольная, тогда добавим упомянутые биты за данной последовательностью, где вес столбцов порождающей матрицы Gldgc удовлетворяет принцип распределения степеней, подобный у LT кода.

В соответствии с другим аспектом настоящего изобретения дается способ кодирования кода низкоплотной порождающей матрицы. По примеру реализации настоящего изобретения, данный способ включает в себя следующие шаги: построится порождающая матрица Gldgc из K строк и N столбцов, где квадратическая матрица Gldgc (1:K, 1:K) из K строк и первых K столбцов порождающей матрицы Gldgc является верхней или нижней треугольной матрицей, и K, N - положительные целые числа, к тому же K<N; в соответствии с уравнением I×Gldgc (1:K, 1:K)=s, с помощью квадратной матрицы Gldgc (1:K, 1:K) из K строк и первых K столбцов порождающей матрицы Gldgc, последовательности информационных битов m с длиной K, порождается промежуточная переменная I; и по уравнению C=I×Gldgc с помощью порождающей матрицы GIdgc производится кодирование промежуточной переменной I, порождается кодированная последовательность с длиной N, где вес столбцов порождающей матрицы Gldgc удовлетворяет принципу распределения степеней, подобному у LT кода. Квадратическая матрица Gldgc (1:K, 1:K) из K строк и первых K столбцов порождающей матрицы Gldgc может быть левой верхней, левой нижней, правой верхней или правой нижней треугольной матрицей.

В соответствии с другим аспектом настоящего изобретения предлагается устройство кодирования кода низкоплотной порождающей матрицы. По примеру реализации настоящего изобретения, данное устройство в себя включает следующие: блок для порождения матрицы, предназначающийся для того, что порождает порождающую матрицу Gldgc из L строк и N+L-K столбцов, выведет данную матрицу в блок для кодирования блочного кода и выведет квадратическую матрицу Gldgc (1:L, 1:L) из L строк и первых L столбцов матрицы Gldgc, где квадратическая матрица Gldgc (1:L, 1:L) - верхняя или нижняя треугольная матрица, K, L, N - положительные целые числа, к тому же K<L<N; блок для заполнения битов, предназначающийся для того, что добавит L-K известных битов в последовательность информационных битов длины K, требующую кодирования, и порождается последовательность информационных битов m длины L, и выведет данную последовательность в блок для предварительного кодирования; блок для предварительного кодирования, предназначающийся для того, что по I×Gldgc (1:L, 1:L)=m, с помощью квадратической матрицы Gldgc (1:L, 1:L) из L строк и первых L столбцов порождающей матрицы Gldgc, и последовательности информационных битов длины m, порождает промежуточную переменную I, и выведет ее в блок для кодирования блочного кода (данный блок может быть блоком для решения верхнего или нижнего тригонометрического уравнения, имеет два входа Gldgc (1:L, 1:L), m и один выход I); блок для кодирования блочного кода, предназначающийся для того, что по C=I×Gldgc, с помощью порождающей матрицы Gldgc производит кодирование промежуточной переменной I, и порождает кодированная последовательность C с длиной N+L-K (данный блок может быть блоком для матричного умножения, имеет два входа Gldgc, I и выход С); блок для удаления битов, предназначающийся для того, что удалит L-K известных битов из вышеупомянутой кодированной последовательности длины N+L-K, и порождает кодированную последовательность длины N.

Где квадратическая матрица Gldgc (1:L, 1:L) из L строк и первых L столбцов порождающей матрицы Gldgc может быть левой верхней, левой нижней, правой верхней или правой нижней треугольной матрицей, в случае, когда квадратическая матрица Gldgc (1:L, 1:L) из L строк и первых L столбцов порождающей матрицы Gldgc является левой верхней или левой нижней треугольной матрицей, добавляем L-K известных битов перед последовательностью информационных битов длины K, требующей кодирования. А в случае, когда данная матрица - правая верхняя или нижняя треугольная, тогда добавляем упомянутые биты за последовательностью, где вес столбца порождающей матрицы Gldgc удовлетворяет принципу распределения степеней, подобному у LT кода.

В соответствии с другим аспектом настоящего изобретения предлагается устройство кодирования кода низкоплотной порождающей матрицы. По примеру реализации настоящего изобретения, данное устройство в себя включает следующие: блок для порождения матрицы, предназначающийся для порождения матрицы Gldgc из K строк и N столбцов, где квадратическая матрица Gldgc (1:K, 1:K) из K строк и первых K столбцов порождающей матрицы Gldgc - верхняя или нижняя треугольная матрица, K, N - положительные целые числа, к тому же K<N; блок для предварительного кодирования, предназначающийся для того, что по I× Gldgc (1:K, 1:K)=s, с помощью квадратической матрицы Gldgc (1:K, 1:K) из K строк и первых K столбцов порождающей матрицы Gldgc, и последовательности информационных битов s длины K, порождает промежуточную переменную I; блок для кодирования блочного кода, предназначающийся для того, что по C=I×Gldgc, с помощью порождающей матрицы Gldgc, производит кодирование промежуточной переменной I, и порождает кодированное слово длины N.

Где квадратическая матрица Gldgc (1:K, 1:K) из K строк и первых K столбцов порождающей матрицы Gldgc может быть левой верхней, левой нижней, правой верхней или правой нижней треугольной матрицей. Вес столбца порождающей матрицы Gldgc удовлетворяет принципу распределения степеней, подобный у LT кода.

Настоящее изобретение обеспечивает хорошие характеристики кода, понижая его сложность кодирования.

Краткое описание чертежей

Приложенные чертежи, предназначенные для конкретного описания настоящего изобретения, составляют неотъемлемую часть данного заявления. Показательные примеры реализации и их объяснения предназначены для интерпретации данного изобретения и не носят никаких ограничений настоящему изобретению. На чертежах:

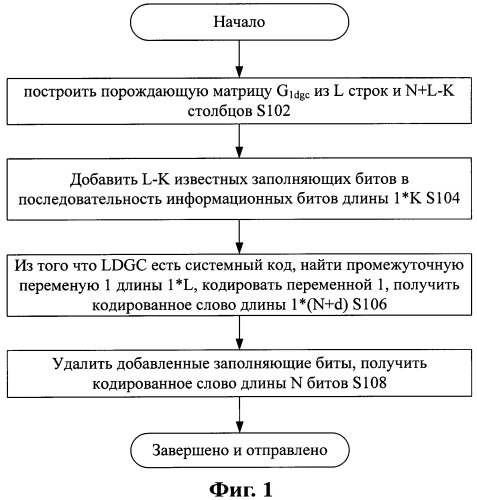

фиг.1 - схема способа кодирования LDGC кода по примеру реализации настоящего изобретения;

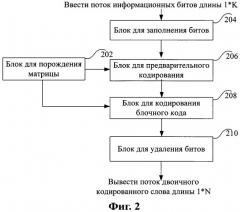

фиг.2 - схема устройства кодирования LDGC кода по примеру реализации настоящего изобретения;

фиг.3 - схема порождающей матрицы LDGC кода;

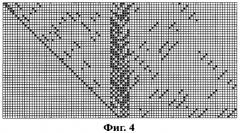

фиг.4- конкретный пример порождающей матрицы LDGC кода заполняющего бита по примеру реализации настоящего изобретения;

фиг.5 - схема способа кодирования LDGC кода по другому примеру реализации настоящего изобретения;

фиг.6 - схема устройства кодирования LDGC кода по другому примеру реализации настоящего изобретения;

фиг.7 - конкретный пример порождающей матрицы LDGC кода заполняющего бита;

фиг.8 - схема блока для предварительного кодирования из устройства кодирования LDGC по другому примеру реализации настоящего изобретения;

фиг.9 - схема блока для блочного кодирования из устройства кодирования LDGC по другому примеру реализации настоящего изобретения.

Осуществление изобретения

Код порождающей матрицы низкой плотности (Low Density Generator Matrix Code, LDGC) представляет собой линейный блочный код, в том числе ненулевые элементы из его порождающей матрицы обычно разрежены. В то же время, LDGC есть системный код, и его квадратическая матрица из первых k столбцов обычно является верхней или нижней треугольной матрицей, и обращение данной матрицы производится методом интеграции. При кодировании LDGC кода, сначала используя соответствие между информационным битом из системного кода и промежуточной переменной, найдется промежуточная переменная, затем получится кодированное слово умножением данной переменной на порождающую матрицу. А при декодирвании LDGC кода сначала найдется промежуточная переменная с помощью порождающей матрицы, затем получатся информационные биты по соотношению трансформации между информационным битом и промежуточной переменной. Описываем конкретные способы реализации настоящего изобретения с помощью приложенных чертежей.

Фиг.1 показывает такой процесс, что производится кодирование последовательности информационных битов длины K, затем выходит кодированное слово длины N в другие блоки для дальнейшей обработки. Где длина контрольного бита составляет M=N-K, кодовая скорость r=K/N. Как показано на фиг.1, по примеру реализации настоящего изобретения способ кодирования LDGC кода включает в себя следующие шаги:

S102, построит порождающую матрицу Gldgc из L строк и N+L-K столбцов, где квадратическая матрица Gldgc (1:L, 1:L) из L строк и первых L столбцов данной матрицы является верхней (или нижней) треугольной матрицей, K, L, N - заданные положительные целые числа, к тому же K<L<N;

S104, добавит d=L-K известных заполняющих битов в последовательность информационных битов s длины 1*K, получит последовательность информационных битов m длины 1*L;

S106, из того, что LDGC - системный код, получит I×Gldgc (1:L, 1:L)=m, и что Gldgc (1:L, 1:L) является верхней (или нижней) треугольной матрицей, найдет промежуточную переменную I решением уранения, и по C=I× Gldgc производит кодирование промежуточной переменной I, найдет кодированное слово длины 1*(N+d);

S108, удалит добавленные в шаге S104 известные биты из кодированных слов длины 1*(N+d), получит кодовое слово длины N битов и отправит его.

Где в каждом столбце порождающей матрицы число элементов 1 (вес столбца) обязательно соответствует определенному принципу распределения. Квадратическая матрица из первых L столбцов и всех строк порождающей матрицы может быть левой верхней, левой нижней, правой верхней или правой нижней треугольной матрицей (как показано на фиг.3).

Где если матрица Gldgc (1:L, 1:L) является левой верхней или левой нижней треугольной матрицей, тогда относительно последовательности информационных битов исходной длины K, добавим d=L-K известных битов перед последовательностью K информационных битов. Если матрица Gldgc (1:L, 1:L) - правая верхняя или правая нижняя треугольная матрица, добавим d=L-K известных битов за данной последовательностью. Следует отметить, что место для добавления заполняющих битов не ограничивается вышесказанными.

Фиг.2 показывает устройство кодирования LDGC кода по примеру реализации настоящего изобретения. Устройство кодирования LDGC предназначается для того, что кодирует введенный поток двоичных информационных битов длины K, затем выведет битовый поток двоичных кодированных слов длины N в другие блоки для дальнейшей обработки. Как показано на фиг.2, данное устройство включает в себя:

блок для порождения матрицы 202, предназначающийся для порождения матрицы Gldgc из L строк и N+L-K столбцов, где квадратическая матрица Gldgc (1:L, 1:L) из L строк и первых L столбцов данной матрицы представляет собой верхнюю (или нижнюю) треугольную матрицу. Матричный генератор выведет матрицу Gldgc (1:L, 1:L) в блок для предварительного кодирования, и выведет Gldgc (1:L, 1:N+L-K) в блок для кодирования блочного кода, где K, L, N - положительные целые числа, к тому же K<L<N;

блок для заполнения битов 204, предназначающийся для того, что добавит d=L-K известных битов в последовательность информационных битов длины 1*К, зато порождает поток информационных битов m длины 1*L и выведет его в блок для предварительно кодирования;

блок для предварительно кодирования 206, предназначающийся для того, что производит решение уравнения для потока информационных битов m длины 1*L, порождает промежуточную переменную длины 1*L-I и выведет ее в кодер блочного кода (как показано на фиг.8, блок для предварительного кодирования может быть блоком для того, что ведет решение верхнего или нижнего тригонометрического уравнения, имеет два входа Gldgc (1:L, 1:L), m и один выход I).

Блок для кодирования блочного кода 208, предназначающийся для того, что производит кодирование промежуточной переменной I, порождает битовой поток вторичного слова C длины 1*(N+d) и выведет его в блок для удаления битов (как показано на фиг.9, блок для блочного кодирования может быть блоком для матричного умножения, имеет два входа Gldgc, I и один выход C).

Блок для удаления битов 210, предназначающийся для того, что удалит d известных битов из блока для заполнения битов, и окончательно получит кодированное слово длины N битов.

Где блок для порождения матрицы порождает матрицу в соответствии со следующим принципом: в каждом столбце порождающей матрицы число элементов 1 (т.е. вес столбца) обязательно соответствует определенному принципу распределения степеней. Квадратическая матрица из первых L столбцов и всех строк порождающей матрицы может быть левой верхней, левой нижней, правой верхней или правой нижней треугольной матрицей (как показано на фиг.3).

Где если матрица Gldgc (1:L, 1:L) является левой верхней или левой нижней треугольной матрицей, тогда относительно последовательности информационных битов исходной длины K добавим d=L-K известных битов перед последовательностью K информационных битов. Если матрица Gldgc (1:L, 1:L) - правая верхняя или правая нижняя треугольная матрица, добавим d=L-K известных битов за данной последовательностью. Следует отметить, что место для добавления заполняющих битов не ограничивается вышесказанными.

Где из того что LDGC - системный код, получится I×Gldgc (1:L, 1:L)=m, таким образом блок для предварительного кодирования найдет промежуточную переменную I длины 1*L решением уравнения, из того что Gldgc (1:L, 1:L) - верхняя (или нижняя) треугольная матрица.

Где по C=I×Gldgc блок для кодирования блочного кода производит кодирование промежуточной переменной I, получит кодированное слово длины 1*(N+d).

Например, поток двоичных информационных битов s длины 1*K=1*24 (s дается выражением D8AB13 в 16-ичной форме) кодируется устройством кодирования по примеру реализации настоящего изобретения и порожается кодированное слово LDGC кода длины 72 битов, получится K=24, N=72.

Блок для порождения матрицы порождает матрицу Gldgc из L=48 строк, N+L-K=96 столбцов, где Gldgc применяет принцип распределения степеней, подобный у LT кода, и квадратическая матрица Gldgc (1:L, 1:L)=Gldgc (1:48, 1:48) из всех строк и первых L столбцов данной матрицы является правой верхней треугольной матрицей, как показано на фиг.4, где черная точка - элемент 1, пустая позиция - 0. Блок для порождения матрицы выведет матрицу Gldgc (1:L, 1:L)=Gldgc (1:48, 1:48) в блок для предварительного кодирования, и выведет матрицу Gldgc (1:L, 1:N+L-K)= Gldgc (1:48, 1:96) в блок для кодирования блочного кода.

Блок для заполнения битов добавит d=L-K=24 известных заполняющих битов P (p дается выражением 9А0С2С в 16-ичной форме) за потоком введенных информационных битов длины 1*K=1*24, и порождает поток информационных битов m длины 1*L=1*48 (m дается выражением D8AB139A0C2C в 16-ичной форме), и выведет ее в блок для предварительного кодирования.

Из того что LDGC - системный код (получится I×Gldgc (1:48, 1:48)=m), и что Gldgc (1:L, 1:L)= Gldgc (1:48, 1:48) - правая верхняя треугольная матрица, блок для предварительного кодирования производит решение уравнения для введенного потока информационных битов s длины 1*K=1*24, найдет промежуточную переменную I длины 1*L=1*48 (I дается выражением 942DA94E0A24 в 16-ичной форме), и выведет данную величину в блок для кодирования блочного кода.

По C=I×Gldgc блок для кодирования блочного кода кодирует введенную промежуточную переменную I, порождает двоичное кодовое слово с длины 1*(N+d)=1*96 (с дается выражением D8AB139A0C2CCD3AC516ED52 в 16-ичной форме), и выведет данное слово в блок для удаления битов.

Блок для удаления битов удалит d=24 известных заполняющих битов из двоичного кодированного слова с длины 1*(N+d)=1*96 и получит кодированное слово длины N=72 битов (дается выражением D8AB13CD3AC516ED52 в 16-ичной форме) и отправит его.

С целью понижения сложности кодирования настоящее изобретение предлагает другой способ кодирования кода низкоплотной порождающей матрицы. В отличие от вышеупомянутого способа, данный способ не ведет заполнение и удаление битов. Фиг.5 показывает такой процесс, что производится кодирование последовательности информационных битов длины K, затем выходит последовательность кодированного слова длины N в другие блоки для дальнейшей обработки, где длина контрольного бита составляет M=N-K, кодовая скорость r=K/N. Как показано на фиг.5, способ кодирования LDGC кода по другому примеру реализации настоящего изобретения включает в себя следующие шаги:

S502, построит порождающую матрицу Gldgc из K строк и N столбцов, где квадратическая матрица Gldgc (1:K, 1:K) из K строк и первых K столбцов данной матрицы - верхняя (или нижняя) треугольная матрица, K, N - положительные целые числа, к тому же K<N;

S504, из того что LDGC есть системный код, получит I×Gldgc (1:K, 1:K)=s, и что G1dgc (1:K, 1:K) - верхняя (или нижняя) треугольная матрица, найдет промежуточную переменную для 1*K решением уравнения.

S506, в соответствии с уравнением С=I×Gldgc, производит кодирование промежуточной переменной I, получит кодированное слово длины 1*N.

Где в каждом столбце порождающей матрицы число элементов 1 (т.е. вес столбца) необходимо удовлетворяет определенному принципу распределения степеней. Квадратическая матрица из первых L столбцов и всех строк порождающей матрицы может быть левой верхней, левой нижней, правой верхней или правой нижней треугольной матрицей (как показано на фиг.3).

Фиг.6 показывает устройства кодирования LDGC кода по другому примеру реализации настоящего изобретения. Данное устройство предназначается для того, что производит кодирование введенного потока двоичных информационных битов длины K, затем выведет битовый поток двоичного кодового слова длины N в другие блоки для дальнейшей обработки. Как показано на фиг.6, устройство включает в себя:

Блок для порождения матрицы 602, предназначающийся для порождения матрицы Gldgc, из K строк и N столбцов, где квадратическая матрица Gldgc (1:K, 1:K) из K строк и первых K столбцов данной матрицы есть верхняя (или нижняя) треугольная матрица. Блок для порождения матрицы выведет матрицу Gldgc (1:K, 1:K) в блок для предварительного кодирования, и выведет Gldgc (1:K, 1:N) в блок для кодирования блочного кода, где K<N;

Блок для предварительного кодирования 604, предназначающийся для того, что производит решение уравнения для введенного потока информационных битов s с длиной 1*K, порождает промежуточную переменную I для 1*K, и выведет ее в кодер блочного кода (как показано на фиг.8, блок для предварительного кодирования может быть блоком для решения верхнего или нижнего тригонометрического уравнения, имеет два входа Gldgc (1:L, 1:L) и последовательность информационных битов m с длиной L).

Блок для кодирования блочного кода 606, предназначающийся для того, что производит кодирование введенной промежуточной переменной I, порождает двоичное кодированное слово C длины 1*N, затем отправит его (как показано на фиг.9, блок для кодирования блочного кода может быть блоком для матричного умножения, имеет два входа: Gldgc и промежуточную переменную I с длиной L);

Где в каждом столбце порождающей матрицы элементов 1 (вес столбца) необходимо удовлетворяет определенному принципу распределения степеней. Квадратическая матрица из первых L столбцов и всех строк порождающей матрицы может быть левой верхней, левой нижней, правой верхней или правой нижней треугольной матрицей (как показано на фиг.3).

Где, из того что LDGC есть системный код (получится I×Gldgc (1:K, 1:K)=s), и что Gldgc (1:K, 1:K) - верхняя (нижняя) треугольная матрица, блок для предварительного кодирования найдет промежуточную переменную I длины 1*K решением уравнения и ее отправит.

Где блок для кодирования блочного кода кодирует промежуточную переменную I в соответствии с уравнением C=I×Gldgc, получит двоичное кодированное слово длины 1*N и его отправит.

Например, поток двоичных информационных битов s длины 1*K=1*24 (s дается выражением D99274 в 16-ичной форме) кодируется устройством кодирования по примеру реализации настоящего изобретения и порождается кодированное слово LDGC кода длины 72 битов, получится K=24, N=72.

Блок для порождения матрицы порождает матрицу Gldgc из L=24 строк, N=72 столбцов, где Gldgc применяет принцип распределения степеней, подобный у LT кода, и квадратическая матрица Gldgc (1:K, 1:K)= Gldgc (1:24, 1:24) из всех строк и первых K столбцов данной матрицы является правой верхней треугольной матрицей, как показано на фиг.7 (где черная точка - элемент 1, пустая позиция - 0). Блок для порождения матрицы выведет матрицу Gldgc (1:K, 1:K)=Gldgc (1:24, 1:24) в блок для предварительного кодирования, и выведет матрицу Gldgc (1:K, 1:N)=Gldgc (1:24, 1:72) в блок для кодирования блочного кода.

Из того что LDGC - системный код (получится I×Gldgc (1:K, 1:K)=s), и что Gldgc (1:K, 1:K)=Gldgc (1:24, 1:24) - правая верхняя треугольная матрица, блок для предварительного кодирования производит решение уравнения для введенного потока информационных битов s длины 1*K, найдет промежуточную переменную I длины 1*L=1*48 (I дается выражением В4В304 в 16-ичной форме), и выведет данную величину в блок для кодирования блочного кода.

По C=I×Gldgc блок для кодирования блочного кода кодирует введенную промежуточную переменную I, порождает двоичное кодовое слово с длины 1*N=1*72 (с дается выражением D99274A593CC1AC461 в 16-ичной форме) и его отправит.

Следует отметить, в описании применяются матрица Gldgc (1:48, 1:48) и Gldgc (1:24, 1:24) как правая верхняя треугольная матрица, и для других форм матрицы настоящее изобретение также подходит. Соответственно, место для заполнения битов не ограничивается вышесказанным. Как только найдется промежуточная переменная с помощью характеристик системного кода, и порождается выход кодированного слова через промежуточный вектор, получится одинаковый технический эффект.

Кроме этого надо добавить, что в вышеупомянутых примерах применяется распределение степеней, подобное у LT кода, как у порождающей матрицы Gldgc, но не ограничивается этим. Всякая низкоплотная порождающая матрица, порождаемая с помощью определенного распределения степеней, может обеспечивать одинаковые технические эффекты.

Одним словом, настоящее изобретение поддерживает кодирование с любой длиной информационного блока и с любой кодовой скоростью, обладает оптимальными характеристиками, подобными Raptor коду.

Вышеупомянутое описание только представляет собой примеры реализации, не составляет ограничения для настоящего изобретения. Для технического персонала в данной области настоящее изобретение может иметь разные модификации и изменения. Все модификации, замены, улучшение и тому подобное, выполненные в соответствии с принципом настоящего изобретения, принадлежат защите в претензии.

1. Способ кодирования кода низкоплотной порождающей матрицы, характеризующийся тем, что он включает в себя следующие шаги:построить порождающую матрицу Gldgc из L строк и N+L-K столбцов, где квадратическая матрица Gldgc (1:L, 1:L) из L строк и первых L столбцов данной матрицы является верхней или нижней треугольной матрицей, К, L, N - положительные целые числа, к тому же K<L<N;добавить L-K известных заполняющих битов в последовательность информационных битов длины К, требующую кодирования, и генерировать последовательность информационных битов m длины L;в соответствии с уравнением IxGldgc (1:L, l:L)=m с помощью квадратической матрицы Gldgc (1:L, 1:L) из L строк и первых L столбцов данной матрицы и последовательности информационных битов m длины L генерировать промежуточную переменную I, в то же время по уравнению C=IxGldgc производят кодирование данной переменной I с использованием порождающей матрицы Gldgc и определяют кодированную последовательность длины N+L-K; иудалить L-K добавленных известных битов из кодированной последовательности длины N+L-K и генерировать кодированную последовательность длины N; гдеm - последовательность информационных битов длиной L, С-кодированная последовательность длиной N+L-K.

2. Способ кодирования по п.1, характеризующийся тем, что в случае, когда квадратическая матрица G1dgc (1:L, 1:L) из L строк и первых L столбцов порождающей матрицы G1dgc является левой верхней или левой нижней треугольной матрицей, добавим L-K известные биты перед последовательностью информационных битов длины К, требующей кодирования.

3. Способ кодирования по п.1, характеризующийся тем, что квадратическая матрица G1dgc (1:L, 1:L) из L строк и первых L столбцов порождающей матрицы G1dgc является правой верхней или правой нижней треугольной матрицей, добавим L-K известных битов за последовательностью информационных битов длины К, требующей кодирования.

4. Способ кодирования по любому из пп.1-3, характеризующийся тем, что вес столбца порождающей матрицы G1dgc удовлетворяет принцип распределения степеней, подобный у LT кода.

5. Способ кодирования кода низкоплотной порождающей матрицы, характеризующийся тем, что он включает в себя следующие шаги:построить порождающую матрицу G1dgc из К строк и N столбцов, где квадратическая матрица G1dgc (1:K, 1:К) из К строк и первых К столбцов порождающей матрицы G1dgc является верхней или нижней треугольной матрицей, К, N - положительные целые числа, к тому же K<N;в соответствии с уравнением I×G1dgc (1:K, 1:K)=s с помощью квадратической матрицы G1dgc (1:K, 1:К) из К строк и первых К столбцов данной порождающей матрицы G1dgc и последовательности информационных битов s с длиной К генерировать промежуточную переменную I;в соответствии с уравнением C=I×G1dgc производят кодирование промежуточной переменной I с использованием порождающей матрицы G1dgc и определяют кодированное слово длины N; гдеs - последовательность информационных битов длиной К, С - кодированная последовательность длиной N.

6. Способ кодирования по п.5, характеризующийся тем, что квадратическая матрица G1dgc (1:K, 1:К) из К строк и первых К столбцов данной порождающей матрицы G1dgc является левой верхней, левой нижней, правой верхней или правой нижней треугольной матрицей.

7. Способ кодирования по п.5 или 6, характеризующийся тем, что вес столбца порождающей матрицы G1dgc удовлетворяет принцип распределения степеней, подобный у LT кода.

8. Устройство кодирования кода низкоплотной порождающей матрицы, характеризующееся тем, что оно в себя включает следующее:блок для генерирования матрицы, предназначающийся для того, что генерирует порождающую матрицу G1dgc из L строк и N+L-K столбцов и выведет ее в блок для кодирования блочного кода, в то же время выведет квадратическую матрицу G1dgc (1:L, 1:L) из L строк и первых L столбцов порождающей матрицы G1dgc в блок для предварительного кодирования, где G1dgc (1:L,1:L) из L строк и первых L столбцов матрицы G1dgc является верхней или нижней треугольной матрицей, К, L, N - положительные целые числа, к тому же K<L<N;блок для заполнения битов, предназначающийся для того, что добавит L-K известных битов в последовательность информационных битов длины К, требующую кодирования, затем генерирует поток информационных битов m с длиной L и выведет его в блок для предварительно кодирования;блок для предварительно кодирования, предназначающийся для того, что по уравнению I×G1dgc (1:L, 1:L)=m с помощью квадратической матрицы G1dgc (1:L, 1:L) из L строк и первых L столбцов матрицы G1dgc и последовательности информационных битов m с длиной L генерирует промежуточную переменную I и выведет ее в блок для кодирования блочного кода;блок для кодирования блочного кода, предназначающийся для того, что по уравнению C=I×G1dgC с помощью порождающей матрицы G1dgc производит кодирование промежуточной переменной I и генерирует кодированную последовательность длины N+L-K;блок для удаления битов, предназначающийся для того, что удалит L-K известных битов из кодированной последовательности длины N+L-K и генерирует кодированную последовательность длины N; гдеm - последовательность информационных битов длиной L, С-кодированная последовательность длиной N+L-K.

9. Устройство кодирования по п.8, характеризующееся тем, что квадратическая матрица G1dgc (1:L, 1:L) из L строк и первых L столбцов порождающей матрицы G1dgc является левой верхней, левой нижней, правой верхней или правой нижней треугольной матрицей.

10. Устройство кодирования по п.9, характеризующееся тем, что в случае, когда G1dgc (1:L, 1:L) из L строк и первых L столбцов порождающей матрицы G1dgc является левой верхней или левой нижней треугольной матрицей, вышеупомянутый блок для заполнения битов добавит L-K известных битов перед последовательностью информационных битов длины К, требующей кодирования.

11. Устройство кодирования по п.9, характеризующееся тем, что в случае, когда G1dgc (1:L, 1:L) из L строк и первых L столбцов порождающей матрицы G1dgc является правой верхней или правой нижней треугольной матрицей, вышеупомянутый блок для заполнения битов добавит L-K известных битов за последовательностью информационных битов длины К, требующей кодирования.

12. Устройство кодирования по любому из пп.8-11, характеризующееся тем, что вес столбца порождающей матрицы G1dgc удовлетворяет принцип распределения степеней, подобный у LT кода.

13. Устройство кодирования кода низкоплотной порождающей матрицы, характеризующееся тем, что оно включает в себя следующее:блок для генерирования матрицы, предназначающийся для генерирования порождающей матрицы G1dgc из К строк и N столбцов, где квадратическая матрица G1dgc (1:K, 1:К) из К строк и первых К столбцов данной матрицы является верхней или нижней треугольной матрицей, К, N - положительные целые числа, к тому же K<N;блок для предварительного кодирования, предназначающийся для того, что в соответствии с уравнением I×G1dgc (1:K, 1:K)=s с помощью квадратической матрицы G1dgc (1:К, 1:К) из К строк и первых К столбцов порождающей матрицы и последовательности информационных битов s с длиной К генерирует промежуточную переменную I;блок дл