Цифровой синтезатор частот

Иллюстрации

Показать всеИзобретение относится к радиотехнике и может использоваться в радиопередающих и измерительных устройствах. Достигаемый технический результата - расширение функциональных возможностей устройства за счет возможности формирования высокочастотных сигналов для приемопередатчиков и служебных сигналов с различным управляемым сдвигом фаз и с разными частотами. Технический результат достигается за счет введения в цифровой синтезатор частот буферного усилителя-формирователя импульсов (31), первого счетчика-делителя (32), второго счетчика-делителя (33), основного счетчика-делителя (34), дополнительного счетчика-делителя (35). 3 ил.

Реферат

Изобретение относится к радиотехнике и может использоваться в радиостанциях в качестве возбудителя передатчика (ПРД) и гетеродина приемника (ПРМ), а также для формирования сигналов для устройств квадратурной угловой модуляции и автокомпенсации амплитудно-фазовых искажений, возникающих в трактах формирования и обработки радиосигналов.

Известен двухкольцевой цифровой синтезатор частот (ЦСЧ) с частотной модуляцией (ЧМ) с последовательным включением колец, построенный на основе системы импульсно-фазовой автоподстройки (ИФАПЧ) с делителем частоты с переменным коэффициентом деления (ДПКД) в цепи обратной связи каждого кольца (см. патент на ПМ №56747, Н03С 3/09, H03L 7/18 от 10.09.2006).

Первое кольцо ИФАПЧ в этом ЦСЧ узкополосное, работает на одной частоте с ЧМ выходного сигнала, который является опорным для второго кольца.

Второе кольцо ИФАПЧ широкодиапазонное, двухканальное - оно может работать или по каналу быстрого переключения частот по заданной программе с использованием второго (дробного) ДПКД, или по каналу обычной работы ЦСЧ с использованием третьего (целочисленного) ДПКД. Диапазон выходных частот и шаг сетки частот по обоим каналам одинаковый. Частотная модуляция в каждом канале осуществляется по двухточечной схеме с использованием ЧМ сигнала с первого кольца.

Недостаток известного устройства состоит в том, что невозможно получение высокого быстродействия при переключении с одной частоты на другую как внутри диапазона ПРМ или ПРД, так и при переключении диапазонов ПРД и ПРМ при сохранении высокой чистоты спектра выходного сигнала и широкой полосы модуляции с минимальными искажениями.

Наиболее близким по технической сущности к предлагаемому является двухкольцевой ЦСЧ с частотной модуляцией (см. патент на ПМ №63996, Н03С 3/09, H03L 7/18 от 10.06.2007), который принят за прототип.

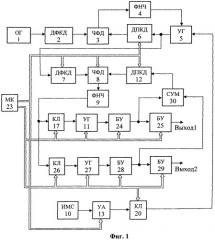

Блок-схема устройства-прототипа приведена на фиг.1, где введены следующие обозначения:

1 - опорный генератор (ОГ);

2 и 7 - первый и второй делители частоты с фиксированным коэффициентом деления (ДФКД);

3 и 8 - первый и второй частотно-фазовые детекторы (ЧФД);

4 и 9 - первый и второй фильтры нижних частот (ФНЧ);

5, 11, 27 - первый, второй и третий управляемые генераторы (УГ);

6 и 12 - первый и второй делители частоты с переменным коэффициентом деления (ДПКД);

17, 20 и 26 - первый, третий и пятый ключи (КЛ);

24, 25, 28 и 29 - первый, второй, третий и четвертый буферные усилители (БУ);

10 - источник модулирующего сигнала (ИМС);

13 - первый управляемый аттенюатор (УА);

30 - сумматор (СУМ);

23 - микроконтроллер (МК).

Устройство-прототип содержит микроконтроллер МК 23, последовательно соединенные опорный генератор ОГ 1, первый делитель частоты с фиксированным коэффициентом деления ДФКД 2, первый частотно-фазовый детектор ЧФД 3, первый фильтр нижних частот ФНЧ 4, первый управляемый генератор УГ 5 и первый делитель частоты с переменным коэффициентом деления ДПКД 6, выход которого соединен со вторым входом первого ЧФД 3; последовательно соединенные второй ДФКД 7, второй ЧФД 8, второй ФНЧ 9, первый ключ КЛ 17, второй УГ 11, первый БУ 24 и второй БУ 25, выход которого является первым выходом устройства; при этом выход УГ 5 соединен со входом ДФКД 7; последовательно соединенные пятый ключ КЛ 26, третий УГ 27, третий БУ 28 и четвертый БУ 29, выход которого является вторым выходом устройства; последовательно соединенные ИМС 10, первый УА 13 и третий ключ КЛ 20, выход которого соединен с модулирующим входом первого УГ 5; а также последовательно соединенные сумматор СУМ 30 и второй ДПКД 12. Причем выход первого буферного усилителя БУ 24 соединен с первым входом сумматора СУМ 30, а выход третьего буферного усилителя БУ 28, кроме того, соединен со вторым входом сумматора СУМ 30. При этом выход второго ДПКД 12 соединен со вторым входом второго ЧФД 8. С первого выхода микроконтроллера МК 23 первая управляющая шина соединена с управляющими входами второго ДФКД 7, второго ЧФД 8, второго ДПКД 12, первого ДПКД 6 и первого УА 13. Со второго выхода микроконтроллера МК 23 вторая управляющая шина соединена с управляющими входами первого КЛ 17, третьего КЛ 20, пятого КЛ 26, первого БУ 24, второго БУ 25, третьего БУ 28, четвертого БУ 29, второго УГ 11 и третьего УГ 27. При этом второй ФНЧ 9, кроме того, соединен с входом пятого ключа КЛ 26.

Устройство-прототип работает следующим образом.

В ЦСЧ с ЧМ функционируют два последовательно включенных кольца ИФАПЧ. Первое кольцо ИФАПЧ узкополосное, работает на одной фиксированной частоте и выполнено на основе последовательно соединенных первого УГ 5, первого ДПКД 6, первого ЧФД 3 и первого ФНЧ 4, выход которого соединен с управляющим входом УГ 5. На опорный вход первого ЧФД 3 поступает от ОГ 1 через первый ДФКД 2 опорный импульсный сигнал с достаточно высокой частотой сравнения, что при узкой полосе пропускания кольца позволяет осуществить значительное подавление помех с частотой сравнения в управляющем сигнале на входе УГ 5. В результате можно получить на его выходе спектрально чистый сигнал, который является опорным для второго кольца ИФАПЧ. В режиме ПРД в первом кольце происходит одноточечная ЧМ по модулирующему входу УГ 5, т.е. в этом режиме опорный сигнал для второго кольца является частотно-модулированным.

Второе кольцо ИФАПЧ на основе последовательно соединенных второго ДФКД 7, второго ЧФД 8 и второго ФНЧ 9, а также второго ДПКД 12, второго УГ 11 и третьего УГ 27 - быстродействующее, имеет два переключаемых выхода, работающих поочередно. С одного выхода (Выход 1) поступает сигнал для гетеродина приемника, с другого {Выход 2) - ЧМ сигнал для возбудителя передатчика. Диапазон выходных частот и даже шаг сетки частот для них могут быть разные. Диапазон выходных частот УГ 27 возбудителя ПРД определяется заданными требованиями для радиостанции, а для работы гетеродина приемника второй УГ 11 имеет диапазон частот, сдвинутый относительно УГ 27 на промежуточную частоту fГЕТ=fПРД+fПЧ. Из-за использования дробного ДПКД с большой дробностью шаг сетки частот УГ 11 можно выбрать значительно меньшим, чем для УГ 27 (для ПРД). Это позволяет более точно настраивать частоту гетеродина приемника с учетом технологического отклонения средней частоты fПЧ в кварцевых фильтрах тракта промежуточной частоты в ПРМ и этим повысить помехоустойчивость ПРМ и его быстродействие.

Управляющий сигнал во втором кольце с выхода второго ЧФД 8 через второй ФНЧ 9 поступает или через первый ключ КЛ 17 на первый управляющий вход второго коммутируемого УГ 11 или через пятый ключ КЛ 26 на первый управляющий вход третьего коммутируемого УГ 27. С выхода второго УГ 11 высокочастотный (ВЧ) сигнал через коммутируемый первый буферный усилитель БУ 24 поступает на первый вход сумматора СУМ 30 и одновременно через коммутируемый второй БУ 25 на «Выход 1» устройства. А с выхода третьего коммутируемого УГ 27 ВЧ сигнал через коммутируемый третий БУ 28 поступает на второй вход СУМ 30 и одновременно через коммутируемый четвертый БУ 29 поступает на «Выход 2» устройства. С выхода СУМ 30 тот или другой ВЧ сигнал поступает на вход второго ДПКД 12 (ДДПКД), на выходе которого формируются короткие импульсы, поступающие на второй вход второго ЧФД 8. На первый вход второго ЧФД 8 поступают короткие опорные импульсы с выхода второго ДФКД 7, сформированные после деления ВЧ сигнала с выхода УГ 5 первого кольца. В результате сравнения этих двух потоков импульсов по частоте и фазе на выходе ЧФД 8 формируется управляющее напряжение, которое фильтруется во втором ФНЧ 9 и через соответствующие ключи поступает на первые входы, или второго УГ 11, или третьего УГ 27, подстраивая их частоту с точностью до фазы под опорный сигнал.

Второй коммутируемый УГ 11 и третий коммутируемый УГ 27 переключаются поочередно и одновременно с соответствующим ключами на входе (КЛ 17 или КЛ 26) и с буферными усилителями на выходах (БУ 24, БУ 25 или БУ 28, БУ 29) по сигналам управления, поступающим по второй управляющей шине от МК 23. Когда выключается второй УГ 11, сразу включается третий УГ 27 и наоборот. При этом на первый или второй вход СУМ 30 поступает ВЧ сигнал или от УГ 11 или от УГ 27 и между выходами устройства получается хорошая развязка по «пролазам» ВЧ сигналов.

Модулирующий сигнал в режиме ЧМ с выхода ИМС 10 через первый УА 13 и третий ключ КЛ 20 поступает на модулирующий вход первого УГ 5, с выхода которого ЧМ опорный сигнал подается на вход второго кольца. На управляющий вход первого УА 13 поступает от микроконтроллера МК 23 по первой управляющей шине соответствующий сигнал управления, по которому изменяется его коэффициент передачи при изменении выходной частоты второго кольца. Тем самым автоматически стабилизируется заданный уровень девиации частоты синтезатора в широком диапазоне переключаемых частот при определенном постоянном уровне модулирующего сигнала от ИМС 10.

По первой управляющей шине от МК 23 сигналы управления в последовательном двоичном коде также поступают на первый ДПКД 6, второй ДПКД 12, второй ЧФД 8 и второй ДФКД 7 для их включения в рабочее состояние на заданную частоту и режим. По сигналам управления от МК 23 меняется режим работы второго ЧФД 8 по току: в переходном режиме ток с выхода ЧФД 8 большой, а значит полоса пропускания кольца ИФАПЧ и быстродействие большое; в режиме синхронизма ток ЧФД мал и полоса пропускания кольца уменьшается для обеспечения требуемого подавления побочных составляющих в спектре выходного сигнала ЦСЧ.

Первая управляющая шина от МК 23 представляет собой стандартный трехпроводный интерфейс, где по трем проводам поступают в последовательном двоичном коде импульсные сигналы: 1) тактовые импульсы; 2) информационный сигнал; 3) импульс разрешения записи передаваемой информации в один из блоков синтезатора.

Недостаток известного устройства-прототипа состоит в следующем.

В современных радиостанциях обычно кроме ВЧ сигналов, необходимых для работы ПРМ и ПРД, формируются различные служебные сигналы для создания информационных последовательностей, сигналов вызова и обмена, для получения квадратурных каналов модуляции, для автокомпенсации амплитудно-фазовых искажений, возникающих в трактах формирования и обработки радиосигналов и др. Эти сигналы формируются от разных источников колебаний, часто не когерентных между собой, с разной стабильностью. В результате одновременной работы различных некогерентных источников колебаний между ними могут образоваться биения, которые являются помехами в работе радиостанции.

В то же время функциональные возможности системы ЦСЧ с МК могут быть гораздо шире. Можно, например, синтезировать с помощью системы ЦСЧ с МК различные вспомогательные колебания, значительно повышающие эффективность работы современных радиоустройств. Причем все колебания от ЦСЧ формируются от одного высокостабильного источника, что исключает возможность получения биений между ними.

В устройстве-прототипе формируются только ВЧ сигналы для ПРМ и ПРД.

Таким образом, недостатком устройства-прототипа являются его ограниченные функциональные возможности.

Для устранения указанного недостатка в цифровой синтезатор частот, содержащий последовательно соединенные опорный генератор, первый делитель частоты с фиксированным коэффициентом деления, первый частотно-фазовый детектор, первый фильтр нижних частот, первый управляемый генератор и первый делитель частоты с переменным коэффициентом деления, выход которого соединен со вторым входом первого частотно-фазового детектора; последовательно соединенные второй делитель частоты с фиксированным коэффициентом деления, второй частотно-фазовый детектор, второй фильтр нижних частот, первый ключ, второй управляемый генератор, первый буферный усилитель, выход которого соединен с первым входом сумматора и входом второго буферного усилителя, выход которого является первым выходом устройства, а также второй делитель частоты с переменным коэффициентом деления, сигнальный вход которого соединен с выходом сумматора, а выход соединен со вторым входом второго частотно-фазового детектора; при этом сигнальный вход второго делителя частоты с фиксированным коэффициентом деления соединен с выходом первого управляемого генератора; последовательно соединенные пятый ключ, третий управляемый генератор и третий буферный усилитель, при этом выход третьего буферного усилителя соединен со вторым входом сумматора и входом четвертого буферного усилителя, выход которого является вторым выходом устройства, а вход пятого ключа соединен также с выходом второго фильтра нижних частот; микроконтроллер, первая управляющая шина которого соединена с управляющими входами первого и второго делителей частоты с переменным коэффициентом деления, второго частотно-фазового детектора, второго делителя частоты с фиксированным коэффициентом деления; вторая управляющая шина микроконтроллера соединена с управляющими входами первого и пятого ключей, второго и третьего управляемых генераторов, первого, второго, третьего и четвертого буферных усилителей, введены последовательно соединенные буферный усилитель-формирователь импульсов, первый счетчик-делитель и второй счетчик-делитель, выход которого является третьим выходом устройства; последовательно соединенные дополнительный счетчик-делитель и основной счетчик-делитель, выход которого является четвертым выходом устройства, причем выход буферного усилителя-формирователя импульсов, кроме того, соединен с сигнальным входом дополнительного счетчика-делителя, а выход первого счетчика-делителя, кроме того, соединен со вторым (сигнальным) входом основного счетчика-делителя; при этом вход буферного усилителя-формирователя импульсов подсоединен к выходу первого управляемого генератора, а управляющие входы первого, второго, основного и дополнительного счетчиков-делителей соединены с первой управляющей шиной микроконтроллера.

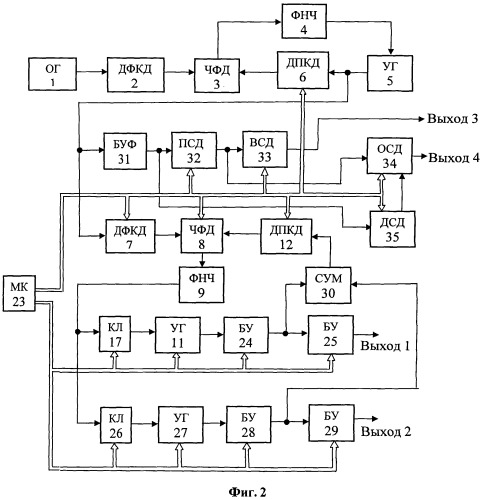

Блок-схема предлагаемого устройства представлена на фиг.2, где введены следующие обозначения:

1 - опорный генератор (ОГ);

2 и 7 - первый и второй делители частоты с фиксированным коэффициентом деления (ДФКД);

3 и 8 - первый и второй частотно-фазовые детекторы (ЧФД);

4 и 9 - первый и второй фильтры нижних частот (ФНЧ);

5, 11, 27 - первый, второй и третий управляемые генераторы (УГ);

6 и 12 - первый и второй делители частоты с переменным коэффициентом деления (ДПКД);

17 и 26 - первый и пятый ключи (КЛ);

24, 25, 28 и 29 - первый, второй, третий и четвертый буферные усилители (БУ);

30 - сумматор (СУМ);

23 - микроконтроллер (МК);

31 - буферный усилитель-формирователь импульсов (БУФ);

32 - первый счетчик-делитель (ПСД);

33- второй счетчик-делитель (ВСД);

34 - основной счетчик-делитель (ОСД);

35 - дополнительный счетчик-делитель (ДСД).

Предлагаемое устройство содержит микроконтроллер МК 23, последовательно соединенные опорный генератор ОГ 1, первый делитель частоты с фиксированным коэффициентом деления ДФКД 2, первый частотно-фазовый детектор ЧФД 3, первый фильтр нижних частот ФНЧ 4, первый управляемый генератор УГ 5 и первый делитель частоты с переменным коэффициентом деления ДПКД 6, выход которого соединен со вторым входом первого ЧФД 3. При этом выход УГ 5 соединен также с входами второго ДФКД 7 и БУФ 31, выход которого соединен с сигнальными входами ДСД 35 и ПСД 32, выход которого соединен с сигнальным входом ВСД 33, выход которого является «Выходом 3» устройства. Кроме того, выход ПСД 32 соединен с первым сигнальным входом ОСД 34, выход которого является «Выходом 4» устройства. Второй вход (вход сброса и начальной установки) ОСД 34 соединен с выходом ДСД 35.

Предлагаемое устройство содержит также последовательно соединенные второй ДФКД 7, второй ЧФД 8, второй ФНЧ 9, первый ключ КЛ 17, второй УГ 11, первый БУ 24 и второй БУ 25, выход которого является «Выходом 1» устройства; последовательно соединенные пятый ключ КЛ 26, третий УГ 27, третий БУ 28 и четвертый БУ 29, выход которого является «Выходом 2» устройства; а также последовательно соединенные сумматор СУМ 30 и второй ДПКД 12. Кроме того, выход первого буферного усилителя БУ 24 соединен с первым входом сумматора СУМ 30, а выход третьего буферного усилителя БУ 28 соединен со вторым входом сумматора СУМ 30. При этом выход второго ДПКД 12 соединен со вторым входом второго ЧФД 8. С первого выхода микроконтроллера МК 23 первая управляющая шина соединена с управляющими входами второго ДФКД 7, второго ЧФД 8, второго ДПКД 12, первого ДПКД 6, ПСД 32, ВСД 33, ОСД 34 и ДСД 35. Со второго выхода МК 23 вторая управляющая шина соединена с управляющими входами первого КЛ 17, пятого КЛ 26, первого БУ 24, второго БУ 25, третьего БУ 28, четвертого БУ 29, второго УГ 11 и третьего УГ 27. Причем выход второго ФНЧ 9 соединен, кроме того, с входом пятого ключа КЛ 26.

Предлагаемое устройство работает следующим образом.

В ЦСЧ с ЧМ функционируют два последовательно включенных кольца ИФАПЧ. Первое кольцо ИФАПЧ узкополосное, работает на одной фиксированной частоте и выполнено на основе последовательно соединенных первого УГ 5, первого ДПКД 6, первого ЧФД 3 и первого ФНЧ 4, выход которого соединен с управляющим входом УГ 5. На опорный вход первого ЧФД 3 поступает от ОГ 1 через первый ДФКД 2 опорный импульсный сигнал с достаточно высокой частотой сравнения, что при узкой полосе пропускания кольца позволяет осуществить значительное подавление помех с частотой сравнения в управляющем сигнале УГ 5. Это позволяет получить на его выходе спектрально чистый сигнал, который является опорным для второго кольца ИФАПЧ и для формирования вспомогательных и служебных сигналов.

В предлагаемом устройстве на выходе УГ 5 формируется один ВЧ сигнал с высокостабильной частотой, который поступает на вход ДФКД 7 и на вход БУФ 31, на выходе которого формируется импульсный сигнал по форме близкий к меандру (см. временные диаграммы на фиг.3а). Этот сигнал с выхода БУФ 31 поступает на сигнальные входы первого счетчика-делителя ПСД 32 и дополнительного счетчика-делителя ДСД 35. С выхода ПСД 32 импульсная последовательность (см. фиг.3б) поступает на сигнальные входы второго счетчика-делителя ВСД 33 и основного счетчика-делителя ОСД 34. На выходе ВСД 33 формируется одна из двух ветвей управляемого цифрового фазовращателя и этот сигнал без фазового сдвига (см. временные диаграммы на фиг.3в) поступает на «Выход 3» устройства. С выхода ОСД 34 поступает сигнал второй ветви управляемого фазовращателя на «Выход 4» устройства с управляемым дискретным фазовым сдвигом относительно сигнала с «Выхода 3» (см. временные диаграммы на фиг.3г-л). Блоки ПСД 32, ВСД 33, ОСД 34 и ДСД 35 образуют цифровой управляемый фазовращатель (ФВ) с практически любой дискретностью изменения фазы сигнала одной ветви ФВ относительно другой и высокой стабильностью установки заданного значения фазы. Сигнал с «Выхода 3» (без фазового сдвига) может быть использован также для формирования различных служебных сигналов. Управление работой ФВ осуществляется от МК 23 по первой управляющей шине, с выхода которой соответствующие сигналы поступают на управляющие входы ПСД 32, ВСД 33, ОСД 34 и ДСД 35. Дискретность задания фаз хорошо вписывается в структуру команд МК 23. В начале оба счетчика-делителя ВСД 33 и ОСД 34 начинают счет одновременно (синхронно) по команде от МК 23, а затем в ОСД 34 происходит заданный сдвиг фазы.

Особенность работы ФВ в предлагаемом устройстве состоит в следующем.

На сигнальный вход ДСД 35 поступает импульсный ВЧ сигнал (см. фиг.3а), а на управляющий вход ДСД 35 по первой управляющей шине поступает с выхода МК 23 сигнал управления, устанавливающий число входных ВЧ импульсов (периодов), которые ДСД 35 должен просчитать и на которые необходимо сдвинуть по фазе сигнал на выходе ОСД 34. По окончании счета на выходе ДСД 35 формируется сигнал начальной установки, который поступает на второй вход ОСД 34, сбрасывает его в начальное состояние, от которого начинает счет, и тем самым определяет заданный сдвиг фаз ФВ на «Выходе 4» относительно «Выхода 3» (см. фиг.3г-л) с высокой точностью и стабильностью.

Например, пусть частота на выходе первого УГ 5 fУГ5=100 МГц, такая же частота и на выходе БУФ 31, коэффициент деления (счета) в ПСД 32 может быть К=2 и больше (см. фиг.3б), т.к. его коэффициент деления управляемый от МК 23 (также, как и коэффициенты деления ВСД 33 и ОСД 34). При К=2 частота на выходе ПСД 32 будет 100 МГц : 2=50 МГц. На фиг.3 в показаны временные диаграммы импульсов на выходе ВСД 33 («Выход 3») при К=8. При этом частота импульсов на выходе ВСД 33 равна 50 МГц : 8=6,25 МГц. Такой же коэффициент деления и такую же частоту на выходе («Выход 4») имеет ОСД 34, только здесь можно сдвигать начальную фазу относительно фазы на «Выходе 3» по сигналу управления от МК 23.

Если нужно сдвинуть фазу импульсов на «Выходе 4» на 4 элементарных ВЧ периода (см. фиг.3а), то ДСД 35 должен просчитать 4 входных импульса и сформировать сигнал сброса и установки с выхода на второй вход ОСД 34. С этого момента ОСД 34 считает входные импульсы со сдвигом на 4 элементарных периода (см. фиг.3ж) относительно «Выхода 3» (без фазового сдвига на фиг.3в). Причем сигнал сброса и установки проходит с выхода ДСД 35 один раз после установки от МК 23 по управляющему входу ДСД 35 заданного значения сдвига фаз.

Частоту импульсов на выходах ВСД 33 и ОСД 34 можно значительно уменьшить по сигналам от МК 23. При этом также значительно уменьшается один дискретный сдвиг фазы.

На фиг.3 в, ж отдельно показан в качестве примера вариант установки на выходах ФВ («Выход 3» и «Выход 4») квадратурных сигналов (со сдвигом 90°).

Таким образом, выбор рабочих частот и дискретных значений фазового сдвига цифрового ФВ может быть самый разнообразный и устанавливается от МК 23.

Второе кольцо ИФАПЧ, как и в прототипе, на основе последовательно соединенных второго ДФКД 7, второго ЧФД 8 и второго ФНЧ 9, а также второго ДПКД 12, второго УГ 11 и третьего УГ 27 - быстродействующее, имеет два переключаемых выхода, работающих поочередно. С одного выхода (Выход 1) поступает сигнал для гетеродина приемника, с другого (Выход 2) - ЧМ сигнал для возбудителя передатчика. Диапазон выходных частот и даже шаг сетки частот для них могут быть разные. Диапазон выходных частот УГ 27 возбудителя ПРД определяется заданными требованиями для радиостанции, а для работы гетеродина приемника второй УГ 11 имеет диапазон частот, сдвинутый относительно УГ 27 на промежуточную частоту fГЕТ=fПРД+fПЧ и из-за использования дробного ДПКД с большой дробностью шаг сетки частот УГ 11 можно выбрать значительно меньшим, чем для УГ 27 (для ПРД). Это позволяет более точно настраивать частоту гетеродина приемника с учетом технологического отклонения средней частоты fПЧ в кварцевых фильтрах тракта промежуточной частоты в ПРМ и этим повысить помехоустойчивость ПРМ и его быстродействие.

Управляющий сигнал во втором кольце с выхода второго ЧФД 8 через второй ФНЧ 9 поступает или через первый ключ КЛ 17 на первый управляющий вход второго коммутируемого УГ 11, или через пятый ключ КЛ 26 на первый управляющий вход третьего коммутируемого УГ 27. С выхода второго УГ 11 высокочастотный (ВЧ) сигнал через коммутируемый первый буферный усилитель БУ 24 поступает на первый вход сумматора СУМ 30 и одновременно через коммутируемый второй БУ 25 на первый «Выход 1» устройства. А с выхода третьего коммутируемого УГ 27 ВЧ сигнал через коммутируемый третий БУ 28 поступает на второй вход СУМ 30 и одновременно через коммутируемый четвертый БУ 29 поступает на второй выход «Выход 2» устройства.

С выхода СУМ 30 тот или другой ВЧ сигнал поступает на вход второго ДПКД 12 (ДДПКД), на выходе которого формируются короткие импульсы, поступающие на второй вход второго ЧФД 8. На первый вход второго ЧФД 8 поступают короткие опорные импульсы с выхода второго ДФКД 7, сформированные после деления ВЧ сигнала с выхода УГ 5 первого кольца. В результате сравнения этих двух потоков импульсов по частоте и фазе на выходе ЧФД 8 формируется управляющее напряжение, которое фильтруется во втором ФНЧ 9 и через соответствующие ключи поступает на первые входы, или второго УГ 11, или третьего УГ 27, подстраивая их частоту с точностью до фазы под опорный сигнал.

Второй коммутируемый УГ 11 или третий коммутируемый УГ 27 переключаются поочередно и одновременно с соответствующим ключами на входе (КЛ 17 или КЛ 26) и с буферными усилителями на выходах (БУ 24, БУ 25 или БУ 28, БУ 29) по сигналам управления, поступающим по второй управляющей шине от МК 23: когда выключается второй УГ 11, сразу включается третий УГ 27 и наоборот. При этом на первый или второй вход СУМ 30 поступает ВЧ сигнал или от УГ 11 или от УГ 27 и между выходами устройства получается хорошая развязка по «пролазам» ВЧ сигналов.

По первой управляющей шине от МК 23 сигналы управления в последовательном двоичном коде также поступают на входы ПСД 32, ВСД 33, ОСД 34, ДСД 35, первый ДПКД 6, второй ДПКД 12, второй ЧФД 8 и второй ДФКД 7 для их включения в рабочее состояние на заданную частоту и режим. По сигналам управления от МК 23 меняется режим работы второго ЧФД 8 по току: в переходном режиме ток с выхода ЧФД 8 большой, а значит полоса пропускания кольца ИФАПЧ и быстродействие большое; в режиме синхронизма ток ЧФД мал и полоса пропускания кольца уменьшается для обеспечения требуемого подавления побочных составляющих в спектре выходного сигнала ЦСЧ.

По второй управляющей шине от МК 23 поступают коммутирующие сигналы на входы управления КЛ 17, КЛ 26, УГ 11, УГ 27, БУ 24, БУ 25, БУ 28, БУ 29. Эти сигналы с уровнем лог. «0» или лог. «1» позволяют включать или отключать указанные блоки.

Таким образом, в предлагаемом ЦСЧ не только формируются ВЧ сигналы для ПРМ и ПРД, но и формируются ВЧ и НЧ сигналы для квадратурных каналов угловой модуляции (которые, кстати, могут быть эффективно использованы в этой же радиостанции для частотной и фазовой модуляции сигнала ПРД), для автоматической компенсации амплитудно-фазовых искажений, возникающих при формировании и обработке радиосигналов, источники которых в ряде случаев неизвестны (см. Автоматические компенсаторы амплитудно-фазовых искажений / Попов П.А. и др; Под ред. П.А.Попова, - Воронеж: Воронежская высшая школа МВД России, 1998. - 200 с.: ил. Квадратурные формирователи радиосигналов: Монография / Попов П.А., Шерстюков С.А. и др. Под ред. П.А.Попова. - Воронеж: Воронежский институт МВД России, 2001. - 176 с.: ил.).

Известные ФВ периодических сигналов имеют или ограниченные значения дискретных сдвигов фазы (см. Фазовращатель периодических сигналов на углы 45°, 135°, 225°, 315°. Пат. на ПМ №66639 от 27.04.2007, Н03С /00, Н03Н 7/18 БИПМ №25 от 10.09. 2007, стр.719) или недостаточно стабильную и неточную установку фазовых сдвигов (см. Устройство управления фазой колебаний. Пат. на ПМ №65699, МПК Н03Н 11/00 от 09. 01. 2007).

В предлагаемом устройстве ФВ может формировать практически любое необходимое значение фазовых сдвигов с высокой стабильностью и повторяемостью под управлением МК 23, что позволяет его использовать также в автоматических измерительных устройствах и в цифровых радиоприемных устройствах (см. Побережский Е.С. Цифровые радиоприемные устройства. - М.: Радио и связь, 1987. Стр.101-114).

Возможность осуществления предлагаемого устройства определяется тем, что вводимые блоки типовые и могут быть выполнены на широкоизвестных микросхемах. Причем в одной микросхеме могут быть один или два независимых ЦСЧ с целочисленным ДПКД (Integer-N) или с дробным (Fractional-N). Например, микросхема LMX2470 фирмы National Semiconductor представляет собой двойной синтезатор с двумя раздельными контурами регулирования: один с дробным ДПКД, другой - с целочисленным. Аналогично этому микросхема ADF4252 фирмы Analog Devices и другие. Ключевые устройства могут быть выполнены на микросхеме МС 14053 фирмы Motorolla. Сумматор ВЧ сигналов выполнен по схеме обычного сумматора на резисторах. Коммутируемые буферные усилители выполнены по схеме усилителя с общим эмиттером на транзисторах типа BFR93A с транзисторным ключом в цепи эмиттера. Двоичные счетчики-делители могут быть выполнены на широкоизвестных цифровых микросхемах КМОП или ТТЛ. Например, микросхема КР1533ИЕ 11 - четырехразрядный двоично-десятичный счетчик с синхронной установкой.

Управление работой блоков ЦСЧ осуществляется от МК 23 типа C8051F220 фирмы Silicon Laboratoies (см., например, О. Николайчук «х51-совместимые микроконтроллеры фирмы Silicon Laboratoies (Cygnal)». - М.: ООО «ИД СКИМЕН», 2004 г., стр 50, 311). Все микроконтроллеры фирмы Silicon Laboratoies имеют встроенную Flash-память программ-данных (объемом от 8 до 128К), встроенную дополнительную оперативную память (объемом от 1 до 8К), стандартное количество портов ввода/вывода (4 порта - 32 линии ввода/вывода) и многое другое. Все это позволяет значительно расширить функциональные возможности предлагаемого устройства и получить новые эффективные решения.

Таким образом, в предложенном ЦСЧ имеется возможность не только сформировать ВЧ сигналы для ПРМ и ПРД, но и сформировать служебные и квадратурные сигналы для квадратурной угловой модуляции в возбудителе передатчика и сформировать сигналы с управляемым фазовращателем с практически любым дискретным фазовым сдвигом для устройств автоматической компенсации различных искажений радиосигналов, для автоматических измерительных устройств и цифровых радиоприемных устройств.

Цифровой синтезатор частот, содержащий последовательно соединенные опорный генератор, первый делитель частоты с фиксированным коэффициентом деления, первый частотно-фазовый детектор, первый фильтр нижних частот, первый управляемый генератор и первый делитель частоты с переменным коэффициентом деления, выход которого соединен со вторым входом первого частотно-фазового детектора; последовательно соединенные второй делитель частоты с фиксированным коэффициентом деления, второй частотно-фазовый детектор, второй фильтр нижних частот, первый ключ, второй управляемый генератор, первый буферный усилитель, выход которого соединен с первым входом сумматора и входом второго буферного усилителя, выход которого является первым выходом устройства, а также второй делитель частоты с переменным коэффициентом деления, сигнальный вход которого соединен с выходом сумматора, а выход соединен со вторым входом второго частотно-фазового детектора; при этом сигнальный вход второго делителя частоты с фиксированным коэффициентом деления соединен с выходом первого управляемого генератора; последовательно соединенные пятый ключ, третий управляемый генератор и третий буферный усилитель, при этом выход третьего буферного усилителя соединен со вторым входом сумматора и входом четвертого буферного усилителя, выход которого является вторым выходом устройства, а вход пятого ключа соединен также с выходом второго фильтра нижних частот; микроконтроллер, первая управляющая шина которого соединена с управляющими входами первого и второго делителей частоты с переменным коэффициентом деления, второго частотно-фазового детектора, второго делителя частоты с фиксированным коэффициентом деления; вторая управляющая шина микроконтроллера соединена с управляющими входами первого и пятого ключей, второго и третьего управляемых генераторов, первого, второго, третьего и четвертого буферных усилителей, отличающийся тем, что введены последовательно соединенные буферный усилитель-формирователь импульсов, первый счетчик-делитель и второй счетчик-делитель, выход которого является третьим выходом устройства; последовательно соединенные дополнительный счетчик-делитель и основной счетчик-делитель, выход которого является четвертым выходом устройства, причем выход буферного усилителя-формирователя импульсов, кроме того, соединен с сигнальным входом дополнительного счетчика-делителя, а выход первого счетчика-делителя, кроме того, соединен со вторым (сигнальным) входом основного счетчика-делителя; при этом вход буферного усилителя-формирователя импульсов подсоединен к выходу первого управляемого генератора, а управляющие входы первого, второго, основного и дополнительного счетчиков-делителей соединены с первой управляющей шиной микроконтроллера.