Дифференциальный операционный усилитель с парафазным выходом

Иллюстрации

Показать всеИзобретение относится к области радиотехники и связи и может быть использовано в качестве устройства усиления СВЧ-аналоговых сигналов, в структуре аналоговых СВЧ-микросхем различного функционального назначения. Технический результат заключается в расширении в 2-3 раза диапазона рабочих частот для традиционных применений ДУ - работе в схемах с общей отрицательной обратной связью. Дифференциальный операционный усилитель с парафазным выходом содержит входной дифференциальный каскад, первый и второй выходные транзисторы, первый и второй дополнительные транзисторы, первый и второй корректирующие конденсаторы, первый и второй двухполюсники коллекторной нагрузки, с первого по четвертый токостабилизирующие двухполюсники. 5 ил.

Реферат

Изобретение относится к области радиотехники и связи и может быть использовано в качестве устройства усиления СВЧ-аналоговых сигналов, в структуре аналоговых СВЧ-микросхем различного функционального назначения (например, интерфейсных усилителях и фильтрах, компараторах, драйверах дифференциальных линий связи и т.п.

Известны схемы двухкаскадных дифференциальных операционных усилителей (ДУ) с парафазным выходом, которые стали основой многих серийных аналоговых микросхем [1-17].

Операционные усилители данного класса применяются в структуре СВЧ-устройств, реализованных на базе широко используемых SiGe-технологий [16-17]. Это связано с возможностью построения на их основе активных RС-фильтров гигагерцевого диапазона для современных и перспективных систем связи, мостовых усилителей мощности и т.п.

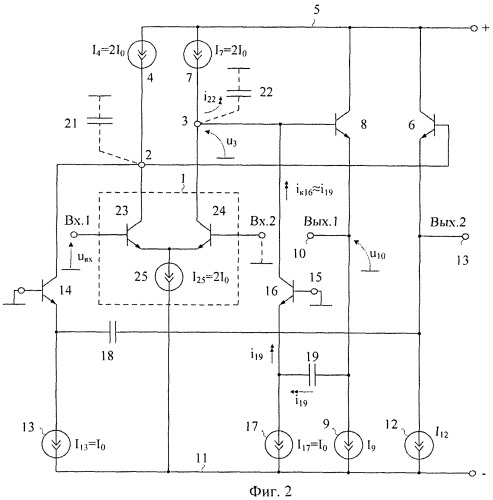

Ближайшим прототипом (фиг.1) заявляемого устройства является дифференциальный операционный усилитель, описанный в структуре модулятора по патенту US 5367271, фиг.5, содержащий входной дифференциальный каскад 1 с первым 2 и вторым 3 токовыми выходами, первый 4 двухполюсник коллекторной нагрузки, включенный между первым 5 источником питания и первым 2 токовым выходом входного дифференциального каскада 1, соединенным с базой первого 6 выходного транзистора, второй 7 двухполюсник коллекторной нагрузки, включенный между первым 5 источником питания и вторым 3 токовым выходом входного дифференциального каскада, соединенным с базой второго 8 выходного транзистора, первый 9 токостабилизирующий двухполюсник, включенный между первым 10 выходом устройства, связанным с эмиттером второго 8 выходного транзистора, и вторым 11 источником питания, второй 12 токостабилизирующий двухполюсник, включенный между вторым 13 выходом устройства, связанным с эмиттером первого 6 выходного транзистора, и вторым 11 источником питания, подключенным к эмиттерной цепи входного дифференциального каскада 1, причем коллекторы первого 6 и второго 8 выходных транзисторов связаны с первым 5 источником питания.

Существенный недостаток известного ДУ состоит в том, что из-за наличия паразитных емкостей на подложку в высокоимпедансных узлах 2 и 3 его верхняя граничная частота (fв) получается сравнительно небольшой.

Основная задача предлагаемого изобретения состоит в расширении в 2-3 раза диапазона рабочих частот (fв) для традиционных применений ДУ - работе в схемах с общей отрицательной обратной связью.

Поставленная задача решается тем, что в дифференциальном операционном усилителе с парафазным выходом, фиг.1, содержащем входной дифференциальный каскад 1 с первым 2 и вторым 3 токовыми выходами, первый 4 двухполюсник коллекторной нагрузки, включенный между первым 5 источником питания и первым 2 токовым выходом входного дифференциального каскада 1, соединенным с базой первого 6 выходного транзистора, второй 7 двухполюсник коллекторной нагрузки, включенный между первым 5 источником питания и вторым 3 токовым выходом входного дифференциального каскада, соединенным с базой второго 8 выходного транзистора, первый 9 токостабилизирующий двухполюсник, включенный между первым 10 выходом устройства, связанным с эмиттером второго 8 выходного транзистора, и вторым 11 источником питания, второй 12 токостабилизирующий двухполюсник, включенный между вторым 13 выходом устройства, связанным с эмиттером первого 6 выходного транзистора, и вторым 11 источником питания, подключенным к эмиттерной цепи входного дифференциального каскада 1, причем коллекторы первого 6 и второго 8 выходных транзисторов связаны с первым 5 источником питания, предусмотрены новые элементы и связи - в схему введен первый 14 дополнительный транзистор, эмиттер которого через третий 13 токостабилизирующий двухполюсник подключен ко второму 11 источнику питания, коллектор соединен с первым 2 токовым выходом входного дифференциального каскада 1, а база соединена с источником напряжения смещения 15, второй 16 дополнительный транзистор, эмиттер которого через четвертый 17 токостабилизирующий двухполюсник подключен ко второму 11 источнику питания, коллектор связан со вторым 3 токовым выходом входного дифференциального каскада, а база соединена с источником напряжения смещения 15, причем между эмиттером первого 14 дополнительного транзистора и эмиттером первого 6 выходного транзистора включен первый 18 корректирующий конденсатор, а между эмиттером второго 16 дополнительного транзистора и эмиттером второго 8 выходного транзистора включен второй 19 корректирующий конденсатор.

На фиг.1 показана схема ДУ-прототипа.

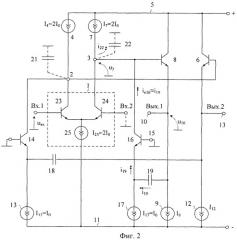

На фиг.2 приведена схема заявляемого устройства в соответствии с формулой изобретения.

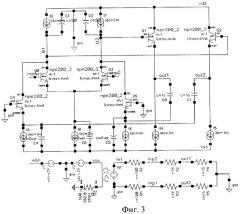

На фиг.3 представлен ДУ фиг.2 в схеме с типовой обратной связью в среде компьютерного моделирования Cadence на моделях SiGe - интегральных транзисторов.

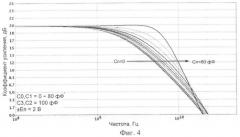

На фиг.4 показана частотная зависимость коэффициента усиления по напряжению ДУ фиг.3 при разных значениях емкости первого (18) и второго (19) корректирующих конденсаторов (C18=C19=Cn=0÷80 фФ).

График фиг.5 характеризует зависимость верхней граничной частоты fв (по уровню - 3 дБ) ДУ фиг.3 в зависимости от емкости первого (18) и второго (19) корректирующих конденсаторов C0=C1=C18=C19=Cn=0÷80 фФ при паразитных емкостях в узлах 2 и 3 С21=С22=100 фФ. График фиг.5 показывает, что при рациональном выборе C18=C19=Cn диапазон рабочих частот ДУ фиг.3 улучшается в 2÷3 раза.

Еще больший выигрыш по верхней граничной частоте реализуется, если в качестве токостабилизирующих двухполюсников 13 и 17 применить не транзисторные источники тока, а резисторы, характеризующиеся меньшей паразитной емкостью на подложку.

Дифференциальный операционный усилитель с парафазным выходом, фиг.2, содержит входной дифференциальный каскад 1 с первым 2 и вторым 3 токовыми выходами, первый 4 двухполюсник коллекторной нагрузки, включенный между первым 5 источником питания и первым 2 токовым выходом входного дифференциального каскада 1, соединенным с базой первого 6 выходного транзистора, второй 7 двухполюсник коллекторной нагрузки, включенный между первым 5 источником питания и вторым 3 токовым выходом входного дифференциального каскада, соединенным с базой второго 8 выходного транзистора, первый 9 токостабилизирующий двухполюсник, включенный между первым 10 выходом устройства, связанным с эмиттером второго 8 выходного транзистора и вторым 11 источником питания, второй 12 токостабилизирующий двухполюсник, включенный между вторым 13 выходом устройства, связанным с эмиттером первого 6 выходного транзистора, и вторым 11 источником питания, подключенным к эмиттерной цепи входного дифференциального каскада 1, причем коллекторы первого 6 и второго 8 выходных транзисторов связаны с первым 5 источником питания. В схему введен первый 14 дополнительный транзистор, эмиттер которого через третий 13 токостабилизирующий двухполюсник подключен ко второму 11 источнику питания, коллектор соединен с первым 2 токовым выходом входного дифференциального каскада 1, а база соединена с источником напряжения смещения 15, второй 16 дополнительный транзистор, эмиттер которого через четвертый 17 токостабилизирующий двухполюсник подключен ко второму 11 источнику питания, коллектор связан со вторым 3 токовым выходом входного дифференциального каскада, а база соединена с источником напряжения смещения 15, причем между эмиттером первого 14 дополнительного транзистора и эмиттером первого 6 выходного транзистора включен первый 18 корректирующий конденсатор 18, а между эмиттером второго 16 дополнительного транзистора и эмиттером второго 8 выходного транзистора включен второй 19 корректирующий конденсатор.

В качестве первого 9, второго 12, третьего 13 и четвертого 17 токостабилизирующих двухполюсников, а также первого 4 и второго 7 двухполюсников коллекторной нагрузки авторы рекомендуют использовать классические источники опорного тока на транзисторах или сравнительно высокоомные резисторы.

Конденсаторы 21 и 22 на фиг.2 моделируют наличие паразитных емкостей на подложку в узлах 2 и 3. Кроме этого на фиг.2 входной дифференциальный каскад 1 реализован на транзисторах 23, 24 и классическом источнике опорного тока 25.

Рассмотрим работу ДУ на фиг.2.

При введении отрицательной обратной связи (фиг.3) статический режим по току транзисторов предлагаемого ДУ устанавливается двухполюсниками 4, 7, 25, 13, 17, 9 и 12.

Под действием положительного сигнала uвх на входе Вх.1 изменяется напряжение u3 в узле 3, которое с единичным коэффициентом передачи передается на выход устройства в узел 10. Изменения u3 и u10 создают токи i22 и i19 через паразитную емкость на подложку 22 и через корректирующий конденсатор 19, зависящие от их численных значений и частоты сигнала.

Приращение тока i19 поступает в эмиттер транзистора 16 и далее в его коллектор, что компенсирует изменение тока i22 через паразитную емкость 22. Если емкости конденсаторов 22 и 19 (21 и 18) приблизительно одинаковы, то влияние паразитной емкости 22 на частотную характеристику ДУ компенсируется емкостью корректирующего конденсатора 19 (фиг.4).

В результате частотный диапазон заявляемого устройства, в сравнении с прототипом, расширяется минимум в 2÷3 раза (фиг.5).

БИБЛИОГРАФИЧЕСКИЙ СПИСОК

1. Патент США №5684419.

2. Патентная заявка WO 2009/042474, fig.5.

3. Патентная заявка WO 96/21271.

4; Патентная заявка США 2010/0019946, fig.3.

5. Патент США №6693489.

6. Патентная заявка WO 2005/074136, fig.1.

7. Патентная заявка США 2006/0038616, fig.1.

8. Патентная заявка США 2010/0102884, fig.2.

9. Патент США №6285245, fig.1.

10. Патент США №4517524.

11. Патент США №4276485, fig.1.

12. Патентная заявка США 2005/0088232.

13. Патент Франции №2409640, fig.1.

14. Патентная заявка США 2005/0110571, fig.7.

15. Патентная заявка США 2009/108882, fig.3.

16. Budyakov, A. Design of Fully Differential OpAmps for GHz Range Applications [Текст] / Budyakov A., Schmalz K., Prokopenko N., Scheytt C., Ostrovskyy P. // Проблемы современной аналоговой микросхемотехники: сб. материалов VI Международного научно-практического семинара. В 3-х ч. Ч.1. Функциональные узлы аналоговых интегральных схем и сложных функциональных блоков / под ред. Н.Н.Прокопенко. - Шахты: Изд-во ЮРГУЭС, 2007 - С.106-110.

17. СВЧ СФ-блоки систем связи на базе полностью дифференциальных, операционных усилителей / Н.Н.Прокопенко, А.С.Будяков, K.Schmalz, С.Scheytt // Проблемы разработки перспективных микро- и наноэлектронных систем - 2010. Сборник трудов / под общ. ред. академика РАН А.Л.Стемпковского. - М.: ИППМ РАН, 2010. - С.583-586.

Дифференциальный операционный усилитель с парафазным выходом, содержащий входной дифференциальный каскад (1) с первым (2) и вторым (3) токовыми выходами, первый (4) двухполюсник коллекторной нагрузки, включенный между первым (5) источником питания и первым (2) токовым выходом входного дифференциального каскада (1), соединенным с базой первого (6) выходного транзистора, второй (7) двухполюсник коллекторной нагрузки, включенный между первым (5) источником питания и вторым (3) токовым выходом входного дифференциального каскада, соединенным с базой второго (8) выходного транзистора, первый (9) токостабилизирующий двухполюсник, включенный между первым (10) выходом устройства, связанным с эмиттером второго (8) выходного транзистора и вторым (11) источником питания, второй (12) токостабилизирующий двухполюсник, включенный между вторым (13) выходом устройства, связанным с эмиттером первого (6) выходного транзистора и вторым (11) источником питания, подключенным к эмиттерной цепи входного дифференциального каскада (1), причем коллекторы первого (6) и второго (8) выходных транзисторов связаны с первым (5) источником питания, отличающийся тем, что в схему введен первый (14) дополнительный транзистор, эмиттер которого через третий (13) токостабилизирующий двухполюсник подключен ко второму (11) источнику питания, коллектор соединен с первым (2) токовым выходом входного дифференциального каскада (1), а база соединена с источником напряжения смещения (15), второй (16) дополнительный транзистор, эмиттер которого через четвертый (17) токостабилизирующий двухполюсник подключен ко второму (11) источнику питания, коллектор связан со вторым (3) токовым выходом входного дифференциального каскада, а база соединена с источником напряжения смещения (15), причем между эмиттером первого (14) дополнительного транзистора и эмиттером первого (6) выходного транзистора включен первый (18) корректирующий конденсатор, а между эмиттером второго (16) дополнительного транзистора и эмиттером второго (8) выходного транзистора включен второй (19) корректирующий конденсатор.