Система для передачи данных

Иллюстрации

Показать всеИзобретение относится к вычислительной технике и может быть использовано при создании управляющих вычислительных машин или систем, имеющих развитую сеть связи с внешними подсистемами. Техническим результатом является расширение функциональных возможностей за счет обеспечения доступа устройства обмена к блоку памяти, с которым работает процессор, что существенно упрощает программирование и экономит машинные ресурсы времени процессора. Система для передачи данных содержит процессор, связанный с блоком памяти, устройство управления с подключенным к нему микропрограммным запоминающим устройством, блок адреса, формирователь синхроимпульсов и буферный накопитель, выход которого является входом-выходом системы. Накопитель связан двунаправленной линией с блоком памяти и подключен синхронизирующим вводом к синхронизирующему выходу устройства управления. Установочный вход устройства управления объединен с установочным входом блока адреса и подключен к выходу процессора. Вход прерывания процессора подключен к сигнальному выходу устройства управления, управляющий выход которого подключен к входу формирователя синхроимпульсов. Выходы формирователя синхроимпульсов подключены к синхронизирующим входам процессора, блока адреса и устройства управления. Счетный выход и сигнальный вход устройства управления подключены соответственно к счетному входу и сигнальному выходу блока адреса, выход которого подключен к адресному входу блока памяти. 4 з.п. ф-лы, 5 ил.

Реферат

Изобретение относится к вычислительной технике и может быть использовано при создании управляющих вычислительных машин (УВМ) или управляющих вычислительных систем (УВС).

Особенностью УВМ и УВС является необходимость обмена информацией (данными) с большим числом периферийных устройств или подсистем, в связи с чем в общем составе задач программного обеспечения и потребляемых машинных ресурсов задачи обмена занимают значительную часть и стоит задача такой организации обмена, которая позволяет максимально высвободить машинные ресурсы (время процессора и объемы памяти) для решения функциональных задач управления. Особенно остро эта задача стоит для вычислительных машин, входящих в состав систем управления подвижными объектами. Менее остро задача оптимизации обмена стоит для электронных вычислительных машин (ЭВМ) общего назначения.

Известно «Устройство для сопряжения электронной вычислительной машины с терминалом» (См. АС №772408, G06F 13/00). Устройство содержит ряд согласующих элементов, обеспечивающих подключение процессора ЭВМ к терминалу. Обмен, т.е. ввод и вывод данных, производится по командам (операциям) обмена, выполняемым оборудованием процессора. Для организации обмена в программу вводятся команды ввода или вывода, выполняемые в общей последовательности операций. Такое построение обмена позволяет упростить программное обеспечение, облегчает отладку программ, но к сожалению потребляет значительные ресурсы машинного времени, так как в течение всего обмена процессор занят и не способен решать другие задачи, а время обмена, особенно при передаче данных последовательным кодом, может быть достаточно велико.

Известно решение, направленное на сокращение времени занятости процессора при обмене последовательным кодом (См. АС №490115 «Система для обмена данными управляющей вычислительной машины с периферийными устройствами»).

В известной системе дополнительно к процессору управляющей вычислительной машины (УВМ) введен регистр обмена, подключенный выходом и входом соответственно к входу и выходу регистра периферийного устройства, таким образом что при сдвиге информации эти регистры образуют по сути единый сдвиговый регистр. В результате после выдачи (сдвига) информации из регистра обмена его содержимое оказывается в регистре периферийного устройства, а содержимое последнего вводится в регистр обмена УВМ. Кроме того, в состав системы входит блок управления, обеспечивающий сдвиг информации синхронно в обоих регистрах, и блок выбора приоритета. Регистр обмена связан с процессором шинами для передачи данных параллельным кодом. После завершения сдвига по сигналу прерывания процессор считывает из регистра обмена принятое слово и записывает новое для следующего обмена.

Такое построение системы позволяет существенно сократить затраты машинного времени, так как передача данных последовательным кодом производится без участия процессора. Кроме того, совмещение ввода с выводом позволят получить дополнительное сокращение времени обмена. Однако процессор занят обработкой прерываний, обменом с регистром обмена и выдачей команд в устройство управления, что также расходует процессорное время, усложняет программы УВМ и затрудняет их отладку. Наиболее полно задача освобождения процессора от непроизводительных затрат на прием и выдачу данных решена в известном устройстве для передачи данных (См. АС №64 2868, H04L 17/02, G06F 3/04 « Устройство для передачи данных»).

Это устройство может быть взято за ПРОТОТИП. Устройство содержит запоминающий блок (блок памяти) буферный накопитель, связанный с периферийным блоком, блок адреса, блок контроля и устройство управления.

Важным достоинством устройства является наличие блока памяти, в который через буферный накопитель (буферный регистр сдвига) могут поступать данные от периферийного блока или, наоборот, данные из блока памяти через буферный накопитель (сдвиговый регистр) могут передаваться в периферийный блок. Такая организация обмена позволяет практически полностью освободить процессор от непроизводительных затрат на передачу данных, за процессором сохраняется задача выдачи команды в устройство управления и кода адреса в блок задания адреса.

Однако в данном устройстве не обеспечивается возможность работы процессора непосредственно с блоком памяти, что ограничивает функциональные возможности при создании программного обеспечения.

Отсутствие возможности работы процессора непосредственно с блоком памяти объясняется видимо сложностью обеспечения доступа к одному блоку двух устройств, а именно процессора и устройства управления с буферным накопителем.

Целесообразно обеспечить возможность работы с блоком памяти и процессору и устройству управления средствами обмена. Для рационального построения программ процессор должен постоянно иметь возможность работать с данными, размещенными в блоке памяти, а устройство управления должно обеспечивать передачу данных между блоком памяти и буферным накопителем (по сути периферийным устройством), не влияя на выполнение функциональных программ процессором.

Решение задачи независимой работы с общим блоком памяти двух устройств не является тривиальной и требует совершенствования известного устройства для передачи данных. С целью расширения функциональных возможностей при создании программного обеспечения за счет обеспечения доступа устройства обмена к блоку памяти, с которым работает процессор, предлагается СИСТЕМА ДЛЯ ПЕРЕДАЧИ ДАННЫХ, содержащая процессор, связанный с блоком памяти, блок адреса, устройство управления и буферный накопитель.

Дополнительно в систему введен формирователь синхроимпульсов и запоминающее устройство микропрограмм. Выход процессора подключен к установочным входам блока адреса и устройства управления. Выход блока адреса подключен к входу блока памяти, связанного двунаправленной линией с буферным накопителем, вход-выход которого являются входом-выходом системы.

Кроме того, сигнальный выход и счетный вход блока адреса подключены соответственно к входу и выходу устройства управления, синхронизирующий выход которого подключен к синхронизирующему входу буферного накопителя и является выходом системы. Управляющий выход устройства управления подключен к входу формирователя синхроимпульсов, выходы которого подключены к синхронизирующим входам процессора, блока адреса и устройства управления, сигнальный выход которого подключен к входу прерывания процессора. Адресный выход устройства управления подключен к входу запоминающего устройства микропрограмм, выходы которого подключены к информационным входам устройства управления.

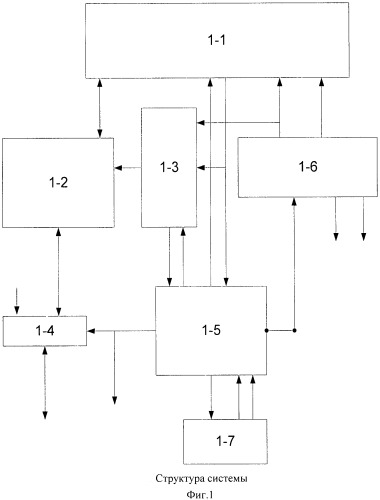

На чертеже (Фиг.1) приведена структура системы для передачи данных, где цифрой 1-1 обозначен процессор, цифрой 1-2 обозначен блок памяти, цифрой 1-3 - блок адреса, цифрой 1-4 обозначен буферный накопитель, цифрой 1-5 обозначено устройство управления, а цифрами 1-6 и 1-7 обозначены соответственно формирователь синхроимпульсов и запоминающее устройство микропрограмм.

На чертеже (Фиг.2) приведена структура устройства управления, где цифрой 2-1 обозначен формирователь адреса микропрограмм (ФАМ), цифрами от 2-2-1 до 2-2-n обозначены триггеры-формирователи управляющих сигналов, на первые входы которых поступают сигналы от формирователя синхроимпульсов, а на вторые входы - функциональные сигналы от запоминающего устройства микропрограмм.

Выходы триггеров являются выходами устройства управления.

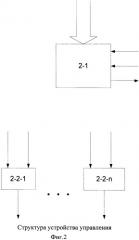

На чертеже (Фиг.3) приведена структура формирователя синхроимпульсов, где цифрой 3-1 обозначен задающий генератор, цифрой 3-2 - инвертор с логической функцией И на входе, цифрой 3-3 обозначена первая секция сдвигового регистра, цифрой 3-4 - элемент И, цифрой 3-5 обозначена вторая секция сдвигового регистра, цифрами 3-6 и 3-7 обозначены соответственно дешифратор и триггер останова, а цифрами от 3-8-1 до 3-8-k обозначены триггеры-формирователи синхросигналов.

Выход задающего генератора подключен к входу первой секции сдвигового регистра и первому входу инвертора, выход которого подключен к синхронизирующим входам сдвигового регистра (его обеих секций).

Выход переноса первой секции подключен к первому входу элемента И, ко второму входу которого подключен выход триггера останова, а выход элемента И подключен к входу второй секции сдвигового регистра, выходы нечетных разрядов которого (обеих секций) подключены к запускающим входам триггеров-формирователей, ко вторым входам которых подключены выходы четных разрядов сдвигового регистра, а выходы триггеров-формирователей являются выходами формирователя. Кроме того, выходы разрядов первой секции сдвигового регистра подключены к входам дешифратора, выход которого подключен ко второму входу инвертора.

На чертеже (Фиг.4) приведена структура блока адреса, где цифрой 4-1 обозначен счетчик числа слов, а цифрой 4-2 - счетчик адреса.

Установочные и счетные входы счетчиков объединены и являются одноименными входами блока, а их выходы являются выходами блока.

На чертеже (Фиг.5) приведена структура формирователя адреса, где цифрой 5-1 обозначен регистр кода операции, цифрами 5-2 и 5-3 обозначены соответственно старшая и младшая части счетчика адреса, а цифрой 5-4 обозначен регистр смещения, который группой входов подключен к выходу микропрограммного запоминающего устройства, а его дополнительные входы являются выходами признаков (условий), формируемых устройством управления, выходы регистров и счетчика образуют шину адреса, являющуюся выходом формирователя.

Цифрой 5-5 обозначен счетчик числа слов, установочные входы которого являются входами формирователя, подключенными к процессору, а выход переполнения счетчика является выходом формирователя. На счетный вход счетчика подается внутренний сигнал устройства управления, формируемый микропрограммным запоминающим устройством. Выход переполнения счетчика подключен к входу регистра смещения.

Система работает следующим образом.

Процессор по своей программе заносит в блок памяти массив информации, подлежащий выдаче, записывает в блок адреса начальный адрес массива, количество слов в массиве и посылает команду начала обмена в устройство управления, которое формирует сигнал останова, поступающий на блок адреса и формирователь синхроимпульсов. Формирователь, получив этот сигнал, прекращает с очередного такта сдвиг информации во второй секции сдвигового регистра и соответственно прекращает формировать синхроимпульсы для процессора. Первая секция продолжает работу и обеспечивает благодаря обратной связи через дешифратор и инвертор формирование синхроимпульсов для работы остальных узлов системы. Процессор, не получая синхроимпульсов, остается в состоянии, соответствующем окончанию обращения к блоку памяти и освобождает связи с ним, переводя их в высокоимпендасное (третье) состояние, одновременно блок адреса, получив сигнал останова, формирует обращение к блоку памяти и инкрементирует адрес, одновременно добавляя к счетчику числа слов «1». Из блока памяти очередное слово данных поступает в буферный накопитель, из которого по синхроимпульсам устройства управления сдвигается в регистр периферийного устройства.

После выдачи последнего слова массива по сигналу переполнения счетчика числа слов устройство управления снимает сигнал останова и формирует сигнал прерывания процессору, который может начать новый обмен, например прием данных.

Прием данных происходит аналогично выдаче, за исключением того, что процессор не готовит массив выдаваемой информации, а освобождает зону в блоке памяти, начальный адрес и длину которой передает в блок адреса и выдает команду устройству управления на прием данных. Устройство управления, формируя синхроимпульсы, обеспечивает сдвиг информации из регистра периферийного устройства в буферный накопитель, из которого оно передается в очередной адрес блока памяти, после чего формируется сигнал останова. Принятое слово передается из буферного накопителя в освободившийся от процессора блок памяти, инкрементируется адрес массива. После приема последнего слова по сигналу счетчика числа слов устройство обмена формирует сигнал прерывания процессору, который может начать очередной цикл обмена (ввода или вывода).

Предложенная реализация обмена существенно освобождает процессор от участия в передаче данных, оставляя за ним задачу работы только с собственным блоком памяти. Вместо прерывания на каждое слово процессор прерывается только один раз после завершения передачи (приема) массива, что существенно упрощает программирование и экономит машинные ресурсы времени процессора.

1. Система для передачи данных, содержащая процессор, связанный с блоком памяти, буферный накопитель и блок адреса, отличающаяся тем, что в ее состав введены формирователь синхроимпульсов и устройство управления с микропрограммным запоминающим устройством, при этом выход процессора подключен к установочным входам блока адреса и устройства управления, у которого управляющий выход подключен к входу формирователя синхроимпульсов, сигнальный выход подключен к входу прерывания процессора, а синхронизирующий выход устройства управления подключен к входу буферного накопителя и является выходом устройства управления и системы в целом, вход-выход которой является входом-выходом буферного накопителя, подключенного двунаправленной линией к блоку памяти, адресный вход которой подключен к выходу блока адреса, сигнальный выход и счетный вход которого подключены соответственно к сигнальному входу и счетному выходу устройства управления, подключенного сигнальным выходом к прерывающему входу процессора, а адресный выход устройства управления подключен к входу микропрограммного запоминающего устройства, выходы которого подключены к информационным входам устройства управления.

2. Система по п.1, отличающаяся тем, что устройство управления содержит формирователь адреса микропрограмм и n триггеров-формирователей, первые входы которых являются функциональными входами, формируемыми микропрограммным запоминающим устройством, вторые входы являются синхронизирующими входами, подключенными к формирователю синхроимпульсов, а выходы триггеров являются выходами устройства, установочный вход которого является входом устройства, подключенным к процессору.

3. Система по п.1, отличающаяся тем, что формирователь синхроимпульсов содержит задающий генератор, инвертор, сдвиговый регистр, состоящий из первой и второй секций, связанных между собой через элемент И, дешифратор, триггер останова и k триггеров-формирователей, первые функциональные входы которых подключены к микропрограммному запоминающему устройству, а вторые стробовые подключены к выходам обеих секций сдвигового регистра, а выходы триггеров являются выходами формирователя, при этом выход задающего генератора подключен к первому входу инвертора и входу первой секции сдвигового регистра, выходы которого подключены к стробовым входам триггеров-формирователей и входам дешифратора, выход которого подключен ко второму входу инвертора, подключенного выходом к синхронизирующим входам сдвигового регистра, выход переноса первой секции которого подключен к первому входу элемента И, выход которого подключен к входу второй секции, а второй вход элемента подключен к выходу триггера останова, стробирующий вход которого подключен к дополнительному выходу дешифратора, а вход является входом формирователя.

4. Система по п.1, отличающаяся тем, что блок адреса содержит счетчик адреса и счетчик числа слов, установочные и счетные входы которых объединены и являются входами блока, а выходы счетчиков являются выходами блока.

5. Система по п.2, отличающаяся тем, что формирователь адреса содержит регистр кода операций, регистр смещения, счетчик адреса и счетчик числа слов, установочные входы которых являются входом формирователя, выходная шина которого образована выходами регистра кода операций, счетчика адреса и регистра смещения, у которого вход смещения и входы признаков являются входами формирователя, сигнальный выход которого является выходом счетчика числа слов.