Комплементарный буферный усилитель

Иллюстрации

Показать всеИзобретение относится к области радиотехники и связи и может быть использовано в качестве выходного каскада аналоговых микросхем различного функционального назначения (например, усилителей мощности, повторителей сигналов, драйверов линий связи и т.п.). Технический результат заключается в повышении входного сопротивления буферного усилителя при низкоомной нагрузке. Комплементарный буферный усилитель содержит первый и второй входные транзисторы, первый и второй дополнительные транзисторы, первый и второй выходные транзисторы, первый и второй токостабилизирующие двухполюсники, первый и второй дополнительные токостабилизирующие двухполюсники, первое и второе дополнительные токовые зеркала. 7 ил.

Реферат

Изобретение относится к области радиотехники и связи и может быть использовано в качестве выходного каскада аналоговых микросхем различного функционального назначения (например, усилителей мощности, повторителей сигналов, драйверов линий связи и т.п.).

В современной радиоэлектронной аппаратуре находят широкое применение буферные усилители (БУ) на основе p-n-p- и n-p-n-транзисторов, так называемые бриллиантовые транзисторы, которые выпускаются как в виде самостоятельных микросхем (BUF1, BUF600, LMH6321 и др.), так и в составе мостовых входных и двухтактных выходных каскадов различных аналоговых устройств [1-46].

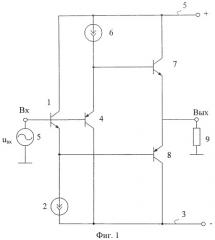

Ближайшим прототипом заявляемого устройства является классический комплементарный буферный усилитель (фиг.1), представленный в патенте США №5.557.238, fig.6.

Существенный недостаток известного БУ состоит в том, что при малых сопротивлениях нагрузки Rн его входное сопротивление не превышает величины:

где βp, βn - коэффициенты усиления по току базы n-p-n- и p-n-p-составных транзисторов БУ.

Если Rн=8 Ом, βp=βn=50, то Rвх.max=20 кОм. В большинстве случаев этого недостаточно. Небольшие значения Rвх.max уменьшают коэффициент усиления по напряжению промежуточных каскадов аналоговых устройств, связанных с буферным усилителем.

В тех случаях, когда Rн велико, применяются специальные схемотехнические методы уменьшения другой составляющей входной проводимости БУ, обусловленной конечной величиной сопротивления коллекторных переходов входных транзисторов - введение в коллекторные цепи входных транзисторов следящего питания [38-46]. Однако при малых Rн такие решения бессмысленны, так как суммарная входная проводимость БУ со следящим питанием будет определяться доминирующей составляющей (1).

Известный БУ, фиг.1, содержит первый 1 входной транзистор, эмиттер которого через первый 2 токостабилизирующий двухполюсник соединен с первой 3 шиной источника питания, база подключена к базе второго 4 входного транзистора и источнику входного сигнала, эмиттер второго 4 входного транзистора соединен со второй 5 шиной источника питания через второй 6 токостабилизирующий двухполюсник и соединен с базой выходного транзистора 7, второй выходной транзистор 8, база которого соединена с эмиттером первого 1 входного транзистора, а эмиттер подключен к эмиттеру первого 7 выходного транзистора и связан с нагрузкой 9, причем коллектор первого 7 выходного транзистора соединен со второй 5 шиной источника питания, а коллектор второго 8 выходного транзистора подключен к первой 3 шине источника питания.

Основная цель предлагаемого изобретения состоит в повышении входного сопротивления буферного усилителя при низкоомной нагрузке.

Поставленная цель достигается тем, что в буферном усилителе, фиг.1, содержащем первый 1 входной транзистор, эмиттер которого через первый 2 токостабилизирующий двухполюсник соединен с первой 3 шиной источника питания, база подключена к базе второго 4 входного транзистора и источнику входного сигнала, эмиттер второго 4 входного транзистора соединен со второй 5 шиной источника питания через второй 6 токостабилизирующий двухполюсник и соединен с базой выходного транзистора 7, второй выходной транзистор 8, база которого соединена с эмиттером первого 1 входного транзистора, а эмиттер подключен к эмиттеру первого 7 выходного транзистора и связан с нагрузкой 9, причем коллектор первого 7 выходного транзистора соединен со второй 5 шиной источника питания, а коллектор второго 8 выходного транзистора подключен к первой 3 шине источника питания, предусмотрены новые элементы и связи - в схему введены первое 10 и второе 11 дополнительные токовые зеркала, вход первого 10 дополнительного токового зеркала, согласованного со второй 5 шиной источника питания, соединен с коллектором первого 1 входного транзистора, а выход подключен к эмиттеру первого 12 дополнительного транзистора и через первый 13 дополнительный токостабилизирующий двухполюсник подключен к первой 3 шине источника питания, а вход второго 11 дополнительного токового зеркала, согласованного с первой 3 шиной источника питания, соединен с коллектором второго 4 входного транзистора, а выход подключен к эмиттеру второго 14 дополнительного транзистора и через второй 15 дополнительный токостабилизирующий двухполюсник связан со второй 5 шиной источника питания, причем коллектор первого 12 дополнительного транзистора соединен со второй 5 шиной источника питания, коллектор второго 14 дополнительного транзистора подключен к первой 3 шине источника питания, а базы первого 12 и второго 14 дополнительных транзисторов соединены с источником сигнала.

На чертеже фиг.1 показана схема БУ-прототипа.

На чертеже фиг.2 представлена схема заявляемого устройства в соответствии с формулой изобретения.

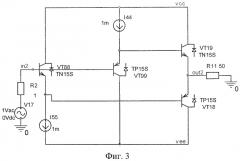

На чертеже фиг.3 приведена схема БУ-прототипа в среде компьютерного моделирования PSpice на моделях интегральных транзисторов ФГУП НПП «Пульсар».

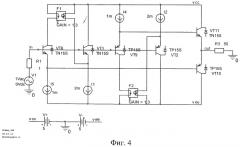

На чертеже фиг.4 приведена схема заявляемого БУ в среде компьютерного моделирования PSpice на моделях интегральных транзисторов ФГУП НПП «Пульсар».

На чертеже фиг.5 приведена зависимость входного дифференциального сопротивления БУ-прототипа (фиг.3) и заявляемого БУ (фиг.4) от частоты при коэффициентах передачи токовых зеркал Ki12=1.

На чертеже фиг.6 показана частотная зависимость Rвх при Ki12=1,3.

На чертеже фиг.7 представлена амплитудно-частотная характеристика схем фиг.3 и фиг.4.

Буферный усилитель, фиг.2, содержит первый 1 входной транзистор, эмиттер которого через первый 2 токостабилизирующий двухполюсник соединен с первой 3 шиной источника питания, база подключена к базе второго 4 входного транзистора и источнику входного сигнала, эмиттер второго 4 входного транзистора соединен со второй 5 шиной источника питания через второй 6 токостабилизирующий двухполюсник и соединен с базой выходного транзистора 7, второй выходной транзистор 8, база которого соединена с эмиттером первого 1 входного транзистора, а эмиттер подключен к эмиттеру первого 7 выходного транзистора и связан с нагрузкой 9, причем коллектор первого 7 выходного транзистора соединен со второй 5 шиной источника питания, а коллектор второго 8 выходного транзистора подключен к первой 3 шине источника питания. В схему введены первое 10 и второе 11 дополнительные токовые зеркала, вход первого 10 дополнительного токового зеркала, согласованного со второй 5 шиной источника питания, соединен с коллектором первого 1 входного транзистора, а выход подключен к эмиттеру первого 12 дополнительного транзистора и через первый 13 дополнительный токостабилизирующий двухполюсник подключен к первой 3 шине источника питания, а вход второго 11 дополнительного токового зеркала, согласованного с первой 3 шиной источника питания, соединен с коллектором второго 4 входного транзистора, а выход подключен к эмиттеру второго 14 дополнительного транзистора и через второй 15 дополнительный токостабилизирующий двухполюсник связан со второй 5 шиной источника питания, причем коллектор первого 12 дополнительного транзистора соединен со второй 5 шиной источника питания, коллектор второго 14 дополнительного транзистора подключен к первой 3 шине источника питания, а базы первого 12 и второго 14 дополнительных транзисторов соединены с источником сигнала.

Рассмотрим работу схемы фиг.2.

В статическом режиме (uвх=0) эмиттерные токи (Iэi) всех транзисторов схемы фиг.2 определяются токами I2=I6=I0 и I13=I15=2I0 токостабилизирующих двухполюсников 2, 13, 6, 15:

При этом ток в нагрузке 9 близок к нулю.

Буферный усилитель, фиг.2, содержит два симметричных повторителя напряжения (элементы 1, 2, 10, 12, 13, 8 и 4, 6, 11, 14, 15, 7), каждый из которых работает при положительной или отрицательной полярности uвх.

Если входное напряжение uвх получает положительное приращение, то это напряжение передается в цепь базы транзистора 7 и создает ток в нагрузке 9. При этом транзистор 8 подзапирается:

где Rн=R9 - сопротивление нагрузки 9.

Изменение iн вызывает изменение тока базы iб7 транзистора 7, тока эмиттера iэ4 транзистора 4, входного и выходного токов токового зеркала 11, тока эмиттера транзистора 14 и, как следствие, соответствующих противоположно направленных токов базы iб4, iб14:

где βi - коэффициент усиления по току базы i-го транзистора;

Ki12.11 - коэффициент передачи по току токового зеркала 11.

Аналогично при другой полярности uвх входное напряжение uвх вызывает приращение эмиттерных и базовых токов транзисторов 1 и 12:

Таким образом, при Ki12.10=Ki12.11=1 и малых uвх входной ток БУ, фиг.2, определяется суммой четырех попарно взаимно компенсируемых слагаемых:

Причем слагаемые iб4 и iб14 зависят от β p-n-p-транзисторов 4 и 14, а слагаемые iб1 и iб12 - определяются β n-p-n-транзисторов 1 и 12. В результате входное сопротивление БУ повышается.

При сравнительно больших уровнях uвх>0 транзистор 8 запирается и поэтому приращение его тока базы iб8≈0. Поэтому входной ток БУ iвх и его входная проводимость в этом режиме:

Для другой полуволны входного напряжения входная проводимость

Для сравнения найдем входные проводимости БУ-прототипа, фиг.1:

Таким образом, в сравнении с прототипом, фиг.1, входное сопротивление заявляемого БУ, фиг.2, повышается в Nвх-раз, где Nвх>>1 при β1≈β12, β4≈β14:

Данные теоретические выводы подтверждаются результатами компьютерного моделирования схем, фиг.3 и фиг.4 - заявляемый БУ имеет при Ki12=1 в 4 раза большее входное сопротивление при низкоомной нагрузке Rн=50 Ом. Более значительный выигрыш (30-40 раз) по Rвх обеспечивается при Ki12.10=Ki12.11=Ki12=1,3.

Таким образом, заявляемое устройство имеет существенные преимущества в сравнении с прототипом.

Источники информации

1. Патент США №6,181.204 fig.2

2. Патент ЕР 0318811

3. Патентная заявка Японии JP 2000/183666

4. Патентная заявка Японии JP 2000/106508

5. Патент Японии JP 6204759

6. Патент Японии JP 6310950

7. Патент Японии JP 11167368

8. Патент Японии JP 10163763

9. Патент Японии JP 10065457

10. Патент Японии JP 10022747

11. Патент США №6.281.752

12. Патент США №6.215.357

13. Патент США№5.512.859

14. Патент США №5.515.007

15. Патент США №5.568.090

16. Патент США №5.907.262

17. Патент США №4.160.216

18. Патент США №6.710.654

19. Патент США №6.160.451

20. Патент США №6.268.769

21. Патент США №6.501.334

22. Патент США №5.144.259

23. Патент США №5.327.095

24. Патент США №5.357.211

25. Патент США №5.479.133

26. Патент США №6.492.870

27. Патент США №4.791.383

28. Патент США №4.833.424

29. Патент США №5.179.355

30. Патент США №5.323.122

31. Патент США №5.557.238

32. Патент США №5.623.230

33. Патент РФ №2193273

34. Патент Японии JP 10270954

35. Патент США №5.374.897

36. Патент США №4.837.523

37. Патент США №6.542.032

38. Патент Японии JP 11251846

39. Патент РФ №2168263

40. Патент РФ №1160530

41. Патент РФ №1506512

42. Патент РФ №1007185

43. Патент США №6.535.063

44. Патент США №5.378.938

45. Патент ЕР 0786858

46. Патент США №5.515.007

Комплементарный буферный усилитель, содержащий первый (1) входной транзистор, эмиттер которого через первый (2) токостабилизирующий двухполюсник соединен с первой (3) шиной источника питания, база подключена к базе второго (4) входного транзистора и источнику входного сигнала, эмиттер второго (4) входного транзистора соединен со второй (5) шиной источника питания через второй (6) токостабилизирующий двухполюсник и соединен с базой выходного транзистора (7), второй выходной транзистор (8), база которого соединена с эмиттером первого (1) входного транзистора, а эмиттер подключен к эмиттеру первого (7) выходного транзистора и связан с нагрузкой (9), причем коллектор первого (7) выходного транзистора соединен со второй (5) шиной источника питания, а коллектор второго (8) выходного транзистора подключен к первой (3) шине источника питания, отличающийся тем, что в схему введены первое (10) и второе (11) дополнительные токовые зеркала, вход первого (10) дополнительного токового зеркала, согласованного со второй (5) шиной источника питания, соединен с коллектором первого (1) входного транзистора, а выход подключен к эмиттеру первого (12) дополнительного транзистора и через первый (13) дополнительный токостабилизирующий двухполюсник подключен к первой (3) шине источника питания, а вход второго (11) дополнительного токового зеркала, согласованного с первой (3) шиной источника питания, соединен с коллектором второго (4) входного транзистора, а выход подключен к эмиттеру второго (14) дополнительного транзистора и через второй (15) дополнительный токостабилизирующий двухполюсник связан со второй (5) шиной источника питания, причем коллектор первого (12) дополнительного транзистора соединен со второй (5) шиной источника питания, коллектор второго (14) дополнительного транзистора подключен к первой (3) шине источника питания, а базы первого (12) и второго (14) дополнительных транзисторов соединены с источником сигнала.