Логический вычислитель

Иллюстрации

Показать всеИзобретение относится к вычислительной техники и может быть использовано для построения средств автоматики, функциональных узлов систем управления. Техническим результатом является упрощение конструкции за счет уменьшения числа типов используемых элементов при сохранении функциональных возможностей прототипа. Устройство содержит 2n элементов ИЛИ (11 …, 12n) и n D-триггеров (21, …,2n) и выполнено с возможностью реализации простых симметричных булевых функций, зависящих от аргументов - входных двоичных сигналов. 2 ил.

Реферат

Изобретение относится к вычислительной технике и может быть использовано для построения средств автоматики, функциональных узлов систем управления и др.

Известны логические вычислители (см., например, патент РФ 2248036, кл. G06F 7/38, 2005 г.; патент РФ 2300138, кл. G06F 7/57, 2007 г.), которые реализуют любую из n простых симметричных булевых функций, зависящих от n аргументов - входных двоичных сигналов.

К причине, препятствующей достижению указанного ниже технического результата при использовании известных логических вычислителей, относится сложность устройства, обусловленная тем, что они состоят из элементов трех типов (D-триггеров, элементов И, элементов ИЛИ).

Наиболее близким устройством того же назначения к заявленному изобретению по совокупности признаков является принятый за прототип логический вычислитель (патент РФ 2248035, кл. G06F 7/38, 2005 г.), который содержит n элементов ИЛИ, n D-триггеров и реализует любую из n простых симметричных булевых функций, зависящих от n аргументов - входных двоичных сигналов.

К причине, препятствующей достижению указанного ниже технического результата при использовании прототипа, относится сложность устройства, обусловленная тем, что прототип состоит из элементов трех типов (D-триггеров, элементов И, элементов ИЛИ).

Техническим результатом изобретения является упрощение устройства за счет уменьшения числа типов используемых элементов при сохранении функциональных возможностей прототипа.

Указанный технический результат при осуществлении изобретения достигается тем, что в логическом вычислителе, содержащем n D-триггеров, объединенные тактовые входы которых подключены к его второму управляющему входу, и n элементов ИЛИ, у которых выход каждого предыдущего элемента ИЛИ соединен с вторым входом последующего элемента ИЛИ, а второй вход первого и выход n-го элементов ИЛИ подключены соответственно к шине нулевого потенциала и выходу логического вычислителя, особенность заключается в том, что в него дополнительно введены n элементов ИЛИ, причем первый, второй входы и выход (n+i)-го элемента ИЛИ соединены соответственно с первым управляющим входом логического вычислителя, вторым входом i-го элемента ИЛИ и входом сброса i-го D-триггера, неинвертирующий выход и вход данных которого подключены соответственно к первому входу i-го элемента ИЛИ и i-му информационному входу логического вычислителя.

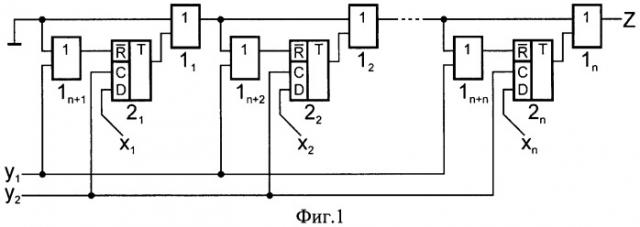

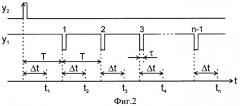

На фиг.1 и фиг.2 представлены соответственно схема предлагаемого логического вычислителя и временные диаграммы управляющих сигналов.

Логический вычислитель содержит элементы ИЛИ 11,… 12n и D-триггеры 21,… 2n, причем второй вход и выход элемента соединены соответственно с вторым входом элемента 1i и входом сброса D-триггера 2i, подключенного неинвертирующим выходом к первому входу элемента 1i, выход элемента соединен с вторым входом элемента 1k+1, а второй вход элемента 11 и выход элемента 1n подключены соответственно к шине нулевого потенциала и выходу логического вычислителя, первый, второй управляющие и i-й информационный входы которого соединены соответственно с первым входом элемента 1n+i тактовым входом и входом данных D-триггера 2i.

Работа предлагаемого логического вычислителя осуществляется следующим образом. На его первый, …, n-й информационные и первый, второй управляющие входы подаются соответственно двоичные сигналы x1, …, xn∈{0,l} и импульсные сигналы y1, y2∈{0,1} (фиг.2), причем период Т и длительность τ импульса сигнала y1 должны удовлетворять условиям T>Δt и τ<τTр+τИЛИ, где Δt=τТр+(n+1)τИЛИ, а τTp и τИЛИ есть длительности задержек, вносимых D-триггером и элементом ИЛИ. В представленной ниже таблице приведены значения сигнала, действующего на выходе предлагаемого логического вычислителя в момент времени , для всех возможных наборов значений входных сигналов х1, …, хn при n=4. С учетом данных, приведенных в таблице, можно записать

где j есть номер момента времени tj (фиг.2). Таким образом, на выходе предлагаемого логического вычислителя получим

Здесь φ1, …, φn есть простые симметричные булевы функции (см. стр.126 в книге Поспелов Д.А. Логические методы анализа и синтеза схем. - М.: Энергия, 1974). Согласно (1) и фиг.2 настройка вычислителя (фиг.1) на реализацию функции φj(j∈{1, …, n}) осуществляется с помощью импульса сигнала y2 и j-1 импульсов сигнала y1.

| x1 | x2 | x3 | x4 | Z | |||

| j=1 | j=2 | j=3 | j=4 | ||||

| 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 |

| 0 | 0 | 0 | 1 | 1 | 0 | 0 | 0 |

| 0 | 0 | 1 | 0 | 1 | 0 | 0 | 0 |

| 0 | 0 | 1 | 1 | 1 | 1 | 0 | 0 |

| 0 | 1 | 0 | 0 | 1 | 0 | 0 | 0 |

| 0 | 1 | 0 | 1 | 1 | 1 | 0 | 0 |

| 0 | 1 | 1 | 0 | 1 | 1 | 0 | 0 |

| 0 | 1 | 1 | 1 | 1 | 1 | 1 | 0 |

| 1 | 0 | 0 | 0 | 1 | 0 | 0 | 0 |

| 1 | 0 | 0 | 1 | 1 | 1 | 0 | 0 |

| 1 | 0 | 1 | 0 | 1 | 1 | 0 | 0 |

| 1 | 0 | 1 | 1 | 1 | 1 | 1 | 0 |

| 1 | 1 | 0 | 0 | 1 | 1 | 0 | 0 |

| 1 | 1 | 0 | 1 | 1 | 1 | 1 | 0 |

| 1 | 1 | 1 | 0 | 1 | 1 | 1 | 0 |

| 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 |

Вышеизложенные сведения позволяют сделать вывод, что предлагаемый логический вычислитель реализует любую из n простых симметричных булевых функций, зависящих от n аргументов - входных двоичных сигналов, и является по сравнению с прототипом более простым, так как состоит из элементов только двух типов (D-триггеров и элементов ИЛИ).

Логический вычислитель, предназначенный для воспроизведения любой из n простых симметричных булевых функций, зависящих от n аргументов - входных двоичных сигналов, содержащий n D-триггеров, объединенные тактовые входы которых подключены к его второму управляющему входу, и n элементов ИЛИ, у которых выход каждого предыдущего элемента ИЛИ соединен с вторым входом последующего элемента ИЛИ, а второй вход первого и выход n-го элементов ИЛИ подключены соответственно к шине нулевого потенциала и выходу логического вычислителя, отличающийся тем, что в него дополнительно введены n элементов ИЛИ, причем первый, второй входы и выход (n+i)-го элемента ИЛИ соединены соответственно с первым управляющим входом логического вычислителя, вторым входом i-го элемента ИЛИ и входом сброса i-го D-триггера, неинвертирующий выход и вход данных которого подключены соответственно к первому входу i-го элемента ИЛИ и i-му информационному входу логического вычислителя.