Корреляционный измеритель временных сдвигов

Иллюстрации

Показать всеИзобретение относится к специализированным средствам обработки сигналов и может быть использовано при построении систем извлечения координатно-временной информации, принцип действия которых основан на определении временного сдвига между принимаемыми сигналами. Технический результат заключается в аппаратурном упрощении корреляционного измерителя. Измеритель реализует метод определения корреляционной функции парными некоррелированными выборками и содержит входной аналоговый мультиплексор, аналого-цифровой преобразователь, регистр, дешифратор, перемножитель, группу накапливающих сумматоров, блок поиска экстремума и блок управления. 2 ил.

Реферат

Изобретение относится к специализированным средствам обработки сигналов и может быть использовано при построении систем извлечения координатно-временной информации, принцип действия которых основан на определении временного сдвига между принимаемыми сигналами.

Известен корреляционный измеритель временных сдвигов, содержащий два коррелятора, блок вычитания, блок регулируемой задержки, блок постоянной задержки, усилитель и два управляемых фильтра, причем выходы первого и второго корреляторов соединены с соответствующими входами блока вычитания, выход которого через усилитель соединен с управляющим входом блока регулируемой задержки, выход которого непосредственно и через блок постоянной задержки соответственно соединен с первыми входами первого и второго корреляторов, вторые входы которых соединены с выходом первого управляемого фильтра, выход второго управляемого фильтра соединен с информационным входом блока регулируемой задержки, информационные входы первого и второго управляемых фильтров являются соответственно первым и вторым входами устройства, управляющие входы первого и второго управляемых фильтров объединены и подключены к выходу усилителя [авт.св. СССР №1101837. Опубл. в БИ №25, 1984 г.].

Недостатком корреляционного измерителя является большой аппаратурный объем.

Наиболее близким по технической сущности к предлагаемому корреляционному измерителю является корреляционный измеритель временных сдвигов, содержащий аналого-цифровой преобразователь, регистр, перемножитель, группу k накапливающих сумматоров, мультиплексор, два демультиплексора, блок поиска экстремума и блок управления, выход мультиплексора подключен к информационному входу аналого-цифрового преобразователя, выход которого подключен к информационному входу первого демультиплексора, первый выход которого соединен с информационным входом регистра, выход которого соединен с первым входом перемножителя, второй вход перемножителя соединен с вторым выходом первого демультиплексора, выход перемножителя соединен с информационным входом второго демультиплексора, k выходов которого соединены с информационными входами соответствующих k накапливающих сумматоров, выходы которых соединены с соответствующими k информационными входами блока поиска экстремума, выход которого является выходом измерителя, информационными входами измерителя являются соответственно первый и второй информационный входы мультиплексора, адресный вход которого объединен с адресным входом первого демультиплексора и подключен к первому адресному выходу блока управления, второй адресный выход которого соединен с адресным входом второго демультиплексора, первый, второй и третий тактовые выходы блока управления соединены с тактовыми входами аналого-цифрового преобразователя, регистра и накапливающих сумматоров соответственно, входы обнуления накапливающих сумматоров объединены с обнуляющим входом блока поиска экстремума и подключены к обнуляющему выходу блока управления, управляющий выход которого соединен с запускающим входом блока поиска экстремума, входами запуска и обнуления корреляционного измерителя являются соответствующие входы блока управления, выход регистра соединен с первым входом перемножителя [патент РФ №2229157. Опубл. в БИ №14, 2004 г.].

Недостатком прототипа является сложность его реализации, что особенно проявляется при работе с многоразрядными операндами, для пересылки которых в прототипе используются многоканальные многоразрядные демультиплексоры.

Технический результат, достигаемый при использовании настоящего изобретения, заключается в упрощении корреляционного измерителя за счет исключения из его состава демультиплексоров.

Технический результат достигается тем, что в известный корреляционный измеритель временных сдвигов, содержащий мультиплексор, аналого-цифровой преобразователь, регистр, перемножитель, группу k накапливающих сумматоров, блок поиска экстремума и блок управления, выход мультиплексора подключен к информационному входу аналого-цифрового преобразователя, выход регистра соединен с первым входом перемножителя, выходы k накапливающих сумматоров соединены с соответствующими k информационными входами блока поиска экстремума, выход которого является выходом измерителя, информационными входами измерителя являются соответственно первый и второй информационный входы мультиплексора, адресный вход которого подключен к первому адресному выходу блока управления, первый, второй и третий тактовые выходы блока управления соединены с тактовыми входами аналого-цифрового преобразователя, регистра и накапливающих сумматоров соответственно, входы обнуления накапливающих сумматоров объединены с обнуляющим входом блока поиска экстремума и подключены к обнуляющему выходу блока управления, управляющий выход которого соединен с запускающим входом блока поиска экстремума, входами запуска и обнуления корреляционного измерителя являются соответствующие входы блока управления, согласно изобретению введен дешифратор, информационный вход которого соединен с вторым адресным выходом блока управления, выход аналого-цифрового преобразователя соединен с информационным входом регистра, второй вход перемножителя объединен с информационным входом регистра, выход перемножителя соединен с объединенными информационными входами k накапливающих сумматоров, разрешающие входы которых соединены с соответствующими k выходами дешифратора.

Сущность изобретения поясняется графическим материалом.

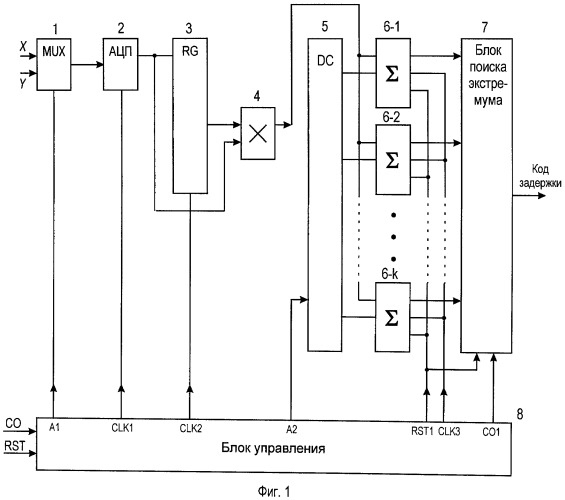

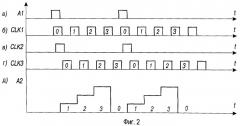

На фиг.1 показана функциональная схема корреляционного измерителя временных сдвигов; на фиг.2 - временные диаграммы, иллюстрирующие работу блока 8 управления.

Функциональная схема корреляционного измерителя (фиг.1) содержит входной аналоговый мультиплексор 1, аналого-цифровой преобразователь (АЦП) 2, регистр 3, перемножитель 4, дешифратор 5, группу 6 k накапливающих сумматоров, блок 7 поиска экстремума и блок 8 управления. Выход мультиплексора 1 подключен к информационному входу АЦП 2, выход которого подключен к информационному входу регистра 3, выход которого соединен с первым входом перемножителя 4, второй вход которого объединен с информационным входом регистра 3, выход перемножителя 4 соединен с объединенными информационными входами k накапливающих сумматоров 6, k выходов дешифратора 5 соединены с разрешающими входами соответствующих накапливающих сумматоров группы 6, выходы которых соединены с соответствующими информационными входами блока 7 поиска экстремума, выход которого является выходом измерителя, входами Х и Y измерителя являются соответственно первый и второй информационный входы мультиплексора 1, адресный вход которого подключен к адресному выходу А1 блока 8 управления, адресный выход А2 которого соединен с информационным входом дешифратора 5, тактовые входы CLK1, CLK2 и CLK3 блока 8 управления соединены с тактовыми входами АЦП 2, регистра 3 и накапливающих сумматоров 6 соответственно, входы обнуления сумматоров группы 6 объединены с обнуляющим входом блока 7 и подключены к выходу RST1 обнуления блока 8 управления, управляющий выход CO1 которого соединен с запускающим входом блока 7 поиска экстремума, входами управления СО и обнуления RST корреляционного измерителя являются соответствующие входы блока 8 управления.

Временные диаграммы по фиг.2 относятся к частному случаю k=3 и содержат адресные импульсы А1 (фиг.2а) на первом адресном выходе блока 8; тактовые импульсы CLK1 (фиг.2б) на первом тактовом выходе блока 8; тактовые импульсы CLK2 (фиг.2в) на втором тактовом выходе блока 8; тактовые импульсы CLK3 (фиг.2г) на третьем тактовом выходе блока 8; текущий адресный код А2 (фиг.2д) на втором адресном выходе блока 8.

Работает корреляционный измеритель следующим образом.

Перед началом запуска блок 8 управления (фиг.1) обнуляют подачей импульса на вход RST, переводя таким образом блок в режим ожидания запускающего импульса. Запуск корреляционного измерителя производится путем подачи на вход СО запускающего импульса, после чего блок 8 управления начинает подачу тактовых импульсов CLK1, CLK2 и CLK3 (фиг.2б, в, г) на тактовые входы АЦП 2, буферного регистра 3 и накапливающих сумматоров 6 соответственно. В первоначальный момент времени ti, например в момент t0, на вход регистра 3 поступает отсчет сигнала x(t), то есть x(t0). Это задается подачей логической единицы на адресный вход мультиплексора 1 (фиг.2а), который коммутирует на вход АЦП 2 сигнал x(t). Для записи указанного отсчета в регистр используется тактовый импульс последовательности CLK2, после чего на входах перемножителя 4 появляется отсчет x(t0), в результате чего временно, в течение одного тактового интервала, на выходе перемножителя 4 имеем квадрат указанной величины - x2(t0). Однако полученное значение в вычислениях не участвует. Далее на адресный вход мультиплексора 1 с блока 8 управления подается команда (низкий логический уровень), переключающая мультиплексор 1 в другой режим коммутации, а именно на вход АЦП 2 коммутируется уже сигнал y(t), а с выхода АЦП 2 сигнал направляется на второй вход перемножителя 4, на первом входе которого уже присутствует отсчет x(t0), хранящийся в регистре 3. При этом запись нового значения в регистр 3 не происходит, так как процесс записи возможен только при наличии тактового импульса CLK2, который в свою очередь формируется только при коммутации отсчета сигнала x(t). Учитывая, что тактирование АЦП 2 происходит с интервалом At, на выходе АЦП 2 имеем выборку y(t0+Δt). Таким образом, моменту времени t0+Δt соответствует появление на выходе перемножителя 4 произведения x(t0)y(t0+Δt), которое направляется на информационный вход накапливающего сумматора 6-1. АЦП 2 оцифровывает значения сигнала y(t) в течение цикла. K раз и, следовательно, на выходе перемножителя 4 в течение цикла формируется K произведений вида

x(t0)y(t0+kΔt), k=1, 2,… K.

Каждое из указанных произведений направляется в соответствующий канальный накапливающий сумматор из группы 6 по правилу: k-e произведение в k-й сумматор. Для коммутации результатов перемножений выборок используется дешифратор 6, управляемый адресным кодом (фиг.2д), поступающим с выхода А2 блока 8 управления. Дешифратор подает разрешающие импульсы на соответствующие сумматоры группы 6 таким образом, что при наличии k-го произведения разрешается работа k-го сумматора. По окончании цикла, после последнего (k+1)-го тактового импульса цикла, на адресном входе мультиплексора 1 вновь устанавливается уровень логической единицы, в результате чего на вход АЦП 2 подается сигнал x(t), а с выхода АЦП 2 очередной отсчет x(ti+1), в нашем примере x(t1), на вход буферного регистра 3, где он хранится в течение всего цикла вычислений. Также, как и в предыдущем цикле, в настоящем цикле происходит формирование отсчетов y(t1+kΔt), в нашем примере y(ti+kΔt), которые после умножения на x(t1) распределяются по сумматорам группы 6, в каждом из которых происходит суммирование с находящимся там ранее полученным результатом.

Блок 7 поиска экстремума осуществляет поиск наибольшей суммы, по которой и выносится решение о положении ординаты взаимокорреляционной функции R(τ) с наибольшим значением, то есть определяющей положение пика функции R(τ). Конечный же результат, искомое время задержки, оценка τ* вычисляется с дискретом Δt по формуле:

τ*(k, Δt)=kΔt,

где k - порядковый номер канального сумматора группы 6, в котором зафиксирована наибольшая сумма.

Показанные на схеме (фиг.1) сигнальные связи в цепи АЦП 2 - регистр 3 - перемножитель 4 - группа сумматоров 6 - блок 7 должны быть реализованы в виде многоразрядных шин (на схеме по фиг.1 связи показаны условно в виде однолинейных цепей без указания разрядности).

Блок 7 поиска экстремума и блок 8 управления идентичны использованным в прототипе [патент РФ №2229157. Опубл. в БИ №14, 2004 г.]. Подчеркнем, что корректное управление измерителем предполагает обнуление перед началом измерений накапливающих сумматоров 6 и блока 7. Сигнал обнуления поступает с выхода RST1 блока 8 управления одновременно с подачей на вход RST блока 8 внешнего импульса обнуления. В простейшем случае это обеспечивается непосредственной связью выхода RST1 блока 8 с его входом RST.

Относительно подключения выходов дешифратора 5 заметим следующее. В связи с особенностями формирования адресного кода (фиг.2д) при использовании дешифратора с традиционной последовательной адресацией необходимо к первому каналу (сумматору 6-1) подключать выход дешифратора, активизируемый по адресу, соответствующему двоичному коду числа «2», ко второму каналу (сумматору 6-2) - выход, соответствующий двоичному коду числа «3» и т.д. по возрастающей, а последний канал, в нашем случае третий, должен соответствовать адресному коду нуля. В итоге перебор каналов с полезной информацией в самом дешифраторе будет начинаться со второго, а заканчиваться нулевым. Адрес, по которому вызывается первый выходной канал дешифратора, не используется, так как согласно последовательности выполнения операций перемножения отсчетов в циклах в этот тактовый интервал (нулевой тактовый интервал) происходит лишь подготовка множителя для вычислений в течение цикла.

Накапливающие сумматоры группы 6 реализуются по известной схеме, содержащей сумматор и регистр, охваченные обратной связью, см., например [Новиков Ю.В. Основы цифровой схемотехники. Базовые элементы и схемы. Методы проектирования. - М.: Мир, 2001, стр.150, рис.4.24]. Разрешающий вход в сумматоре можно организовать при помощи дополнительного элемента 2И, выход которого подключают к тактовому входу регистра накапливающего сумматора, при этом первый вход элемента 2И будет выполнять функции тактового входа накапливающего сумматора, а второй вход - функции разрешающего входа.

В заявленном измерителе, в отличие от прототипа, отсутствуют многоканальные демультиплексоры, предназначенные для коммутации многоразрядных цифровых данных. При этом пересылка многоразрядного цифрового кода с выхода перемножителя 4 на информационные входы накапливающих сумматоров 6 осуществляется по одной информационной шине (фиг.1), к которой подключены все сумматоры (фактически процесс коммутации заменен на процесс выдачи сигналов, разрешающих прием результатов перемножений). Что же касается наличия в схеме дешифратора 5, которого нет в прототипе, то он как цифровое устройство значительно проще многоразрядного демультиплексора, не содержит многоразрядных выходов и предназначен всего лишь для формирования управляющих сигналов на k одноразрядных выходах дешифратора.

Корреляционный измеритель временных сдвигов, содержащий мультиплексор, аналого-цифровой преобразователь, регистр, перемножитель, группу k накапливающих сумматоров, блок поиска экстремума и блок управления, выход мультиплексора подключен к информационному входу аналого-цифрового преобразователя, выход регистра соединен с первым входом перемножителя, выходы k накапливающих сумматоров соединены с соответствующими k информационными входами блока поиска экстремума, выход которого является выходом измерителя, информационными входами измерителя являются соответственно первый и второй информационный входы мультиплексора, адресный вход которого подключен к первому адресному выходу блока управления, первый, второй и третий тактовые выходы блока управления соединены с тактовыми входами аналого-цифрового преобразователя, регистра и накапливающих сумматоров соответственно, входы обнуления накапливающих сумматоров объединены с обнуляющим входом блока поиска экстремума и подключены к обнуляющему выходу блока управления, управляющий выход которого соединен с запускающим входом блока поиска экстремума, входами запуска и обнуления корреляционного измерителя являются соответствующие входы блока управления, отличающийся тем, что в него введен дешифратор, информационный вход которого соединен с вторым адресным выходом блока управления, выход аналого-цифрового преобразователя соединен с информационным входом регистра, второй вход перемножителя объединен с информационным входом регистра, выход перемножителя соединен с объединенными информационными входами k накапливающих сумматоров, разрешающие входы, которых соединены с соответствующими k выходами дешифратора.