Устройство отображения и мобильный терминал

Иллюстрации

Показать всеИзобретение относится к синхросигналу, используемому для операции отображения устройства отображения. Техническим результатом является расширение функциональных возможностей за счет генерации в устройстве отображения синхросигнала общего переменного напряжения. Устройство отображения настоящего изобретения является устройством отображения активного матричного типа и включает в себя драйвер отображения, на который подают данные (DR, DG и DB) изображения, включенные в последовательные данные (SI), посредством последовательной передачи. Последовательные данные (SI) обеспечиваются первым флагом (D1) для задания полярности напряжения (Vcom) общего электрода. Драйвер отображения извлекает первый флаг (D1) из последовательных данных (SI), в соответствии с синхронизацией последовательного тактового сигнала (SCLK), и осуществляет отображение, в соответствии с данными (DR, DG и DB) изображения, при генерировании напряжения (Vcom) общего электрода, напряжение которого имеет полярность, заданную посредством извлеченного первого флага (D1). Благодаря этому реализуется устройство отображения, которое может генерировать синхросигнал для общего переменного напряжения при малых размерах схемы. 2 н. и 13 з.п. ф-лы, 16 ил.

Реферат

Область техники, к которой относится изобретение

Настоящее изобретение относится к синхросигналу, используемому для операции отображения устройства отображения.

Уровень техники

Известно устройство отображения, которое включает в себя схему памяти (далее в настоящем документе называемую памятью пиксела) в каждом пикселе, и хранит данные изображения в памяти пиксела для отображения статического изображения с низким энергопотреблением без непрерывной подачи данных изображения извне. Энергопотребление сокращается посредством, например, (i) количества энергии для загрузки и разгрузки, посредством данных изображения, сигнальных линий данных для подачи данных изображения на пикселы, и (ii) количеству энергии для передачи данных изображения извне панели на драйвер. Количество (i) сокращается по причине того, что однажды записав данные изображения в память пиксела, такая загрузка или разгрузка больше не является необходимой, а количество (ii) сокращается по причине того, что однажды записав данные изображения в память пиксела, такая передача больше не является необходимой.

Были разработаны виды памяти пиксела на основе SRAM и DRAM. Напряжение пиксела устройства отображения, имеющего память пиксела на основе SRAM или DRAM, является цифровым. Поэтому такое устройство отображения почти не вызывает перекрестных помех и имеет превосходное качество отображения.

Фиг.14 показывает конфигурацию устройства отображения, включающего в себя такую память пиксела, описанную в патентной литературе 1.

Устройство отображения включает в себя драйвер 18 линии сканирования адреса X, драйвер 19 цифровых данных и драйвер 20 аналоговых данных, и может раздельно осуществлять режим отображения изображения из цифровых данных и режим отображения изображения из аналоговых данных.

Далее описывается режим отображения изображения из цифровых данных. Выбирается сигнальная линия 4-n (n является положительным целым числом) адреса X, соединенная с пикселом, в который должны быть записаны данные изображения. Затем, из соответствующей ему первой линии 1-n управления отображением, сигнал цифровых данных записывается в цифровой элемент 100 памяти, включающий в себя схему 11 И-НЕ и тактированный инвертирующий элемент 13, посредством первого переключающего элемента 8 пиксела. В это время цифровой элемент 100 памяти активируется по линии 15 управления режимом отображения.

Вход цифрового элемента 100 памяти соединяется со вторым переключающим элементом 9, а выход цифрового элемента 100 памяти соединяется с третьим переключающим элементом 10. Поэтому в зависимости от высокого или низкого уровня сигнала цифровых данных, либо второй переключающий элемент 9, либо третий переключающий элемент 10 становится токопроводящим. Опорное напряжение для отображения белого цвета подается на вторую линию 2-n управления отображением либо на третью линию 3 управления отображением, а опорное напряжение для отображения черного цвета подается на другую одну из второй линии 2-n управления отображением и третьей линии 3 управления отображением. В зависимости от того, какой из переключающих элементов стал токопроводящим, второй переключающий элемент 9 или третий переключающий элемент 10 выбирает напряжение для отображения белого цвета или напряжение для отображения черного цвета, а затем применяет его к жидкокристаллической ячейке 6. Жидкокристаллическая ячейка 6 поддерживает состояние отображения, вызванное посредством сигнала цифровых данных, хранящегося в цифровом элементе 100 памяти, до тех пор, пока первый переключающий элемент 8 снова не станет токопроводящим, а другой сигнал цифровых данных не будет записан в цифровой элемент 100 памяти.

Патентная литература 1

Публикация заявки на патент Японии, Tokukai, №2003-177717A (дата публикации: 27 июня 2003 года).

Патентная литература 2

Публикация заявки на патент Японии, Tokukaisho, №58-23091A (дата публикации: 10 февраля 1983 года).

Патентная литература 3

Публикация заявки на патент Японии, Tokukai, №2007-286237A (дата публикации: 1 ноября 2007 года).

Сущность изобретения

В последнее время все больше и больше интерфейсов для передачи отображаемых данных для использования в жидкокристаллических устройствах отображения, вместо способа параллельной передачи цифрового сигнала RGB (интерфейс RGB) с использованием большого количества сигнальных линий, употребляют способ высокоскоростной последовательной передачи с использованием меньшего количества сигнальных линий. Технология способа последовательной передачи является важной, в частности, для мобильного устройства, такого как мобильный телефон, поскольку мобильное устройство нуждается в сокращении пространства для расположения проводки, и в препятствовании повреждения проводника. Дополнительно, осуществление дифференциальной передачи предоставляет возможность высокоскоростной передачи с низким энергопотреблением. При такой последовательной передаче отображаемые данные и управляющая команда передаются по одной и той же шине.

Например, согласно стандартам MIPI (интерфейса мобильного промышленного процессора), которые предписывают общие спецификации для так называемого интерфейса CPU, который является интерфейсом между прикладным процессором и периферийным устройством мобильного устройства, прикладной процессор функционирует в качестве хоста для управления работой периферийного устройства. Устройство управления отображением, которое использует сигнал управления, как правило, начинает операцию отображения, как определяется посредством управляющей команды. Такое устройство управления отображением начинает отображение на экран в ответ на команду запуска, передаваемую на устройство управления отображением с хоста после активации источника питания.

Фиг.15 - вид, схематически показывающий конфигурацию соединения схем мобильного телефона, включающего в себя секцию жидкокристаллического дисплея, обеспеченную таким интерфейсом CPU.

Мобильный телефон 101 включает в себя секцию 102 жидкокристаллического дисплея, драйвер 103 жидкого кристалла, антенну 104, радиочастотную (RF) схему 105, процессор 106 немодулированной передачи данных и прикладной процессор 107.

Секция 102 жидкокристаллического дисплея имеет пикселы, располагаемые в матрице. Сигналы данных соответствующим образом записываются в пикселы по их соответствующим линиям SL1-SLn шины истока. Сигналы данных подаются на линии SL1-SLn шины истока с драйвера 103 жидкого кристалла. Дополнительно, каждый сканирующий сигнал, выбирающий линию, включающую в себя множество пикселов, подается на линии шины затвора с драйвера 103 жидкого кристалла для записи сигналов данных в пикселы (эта операция не показана).

Драйвер 103 жидкого кристалла является схемой, которая управляет отображением секции 102 жидкокристаллического дисплея, включающей в себя один или более кристаллов. Дополнительно, драйвер 103 жидкого кристалла включает в себя схемные секции, такие как синхрогенератор, драйвер истока, драйвер затвора, схему питания и память, каждый из которых относится к операции отображения. Помимо всего прочего, драйвер 103 жидкого кристалла управляется прикладным процессором 107, служащим в качестве хоста, по последовательной шине I/F BUS, и включает в себя его интерфейс.

Антенна 104 является антенной, которую мобильный телефон 101 использует для передачи и приема. RF схема 105 обрабатывает радиочастотный сигнал при передаче и приеме. Процессор 106 немодулированной передачи данных обрабатывает немодулированный сигнал, демодулированный посредством RF схемы 105, и управляет работой схемы обработки речи (не показана) и схемы обработки передачи данных (не показана). Прикладной процессор 107 управляет драйвером 103 жидкого кристалла и периферийным устройством (не показано), которое обрабатывает движущееся изображение, музыку, видеоигру и/или подобное.

Фиг.16 показывает пример структуры драйвера 103 жидкого кристалла.

Последовательный интерфейс 131 драйвера 103 жидкого кристалла принимает управляющую команду и отображаемые данные, подающиеся с последовательной интерфейсной шины I/F BUS, и управляющая команда записывается в регистр 132. В соответствии с синхронизацией, с которой принимается управляющая команда и отображаемые данные, синхрогенератор 135 генерирует синхросигнал посредством использования тактового генератора, включенного в синхрогенератор 135. В соответствии с синхросигналом отображаемые данные передаются с последовательного интерфейса 131 на сдвиговый регистр 133, а затем на схему 134 управления истоком, в таком порядке, для подачи сигнала данных на линию SL истока.

Для управления каждой частью драйвера и секции жидкокристаллического дисплея, в случае интерфейса RGB, извне подается сигнал вертикальной синхронизации и сигнал горизонтальной синхронизации; однако, в случае, если драйвер жидкого кристалла включает в себя вышеописанный интерфейс CPU, вместо сигнала вертикальной синхронизации или сигнала горизонтальной синхронизации синхрогенератор всё равно генерирует синхросигнал посредством использования генератора свободных колебаний, в соответствии с управляющей командой и отображаемыми данными, которые подаются посредством последовательной передачи. В случае, если пиксел включает в себя вышеописанную память пиксела, то отображение статического изображения осуществляется следующим образом: после записи отображаемых данных в схему памяти подача данных с прикладного процессора останавливается для сокращения энергопотребления. Поэтому генерирование синхросигнала в драйвере жидкого кристалла является важным.

Как было описано выше, чтобы применять общее переменное напряжение, традиционный способ интерфейса CPU должен генерировать сигнал общего переменного напряжения с использованием тактового сигнала, генерируемого посредством синхрогенератора, предпочтительнее, чем с использованием сигнала вертикальной синхронизации или сигнала горизонтальной синхронизации, используемого в интерфейсе RGB. Поэтому чтобы сгенерировать синхросигнал для общего переменного напряжения, даже исключительно для отображения статического изображения, традиционный интерфейс CPU нуждается в тактовом генераторе или в специализированном управляющем терминале для внешнего управления генерированием синхросигнала. Это препятствует сокращению размеров схемы драйвера жидкого кристалла.

Настоящее изобретение было создано ввиду вышеупомянутой проблемы, а цель настоящего изобретения заключается в реализации устройства отображения, которое может генерировать синхросигнал общего переменного напряжения и имеет при этом малые размеры схемы, и мобильного терминала, включающего в себя устройство отображения.

Для достижения цели, устройство отображения настоящего изобретения является устройством отображения активного матричного типа и включает в себя драйвер отображения, на который посредством последовательной передачи подаются данные изображения, включенные в последовательные данные, последовательные данные имеют добавленный в них первый флаг для задания полярности напряжения общего электрода, драйвер отображения извлекает первый флаг из последовательных данных, в соответствии с синхронизацией последовательного тактового сигнала, передаваемого по проводнику, используемому для последовательной передачи, но отличному от проводника для последовательных данных, и драйвер отображения осуществляет отображение, в соответствии с последовательными данными, при подаче напряжения общего электрода, напряжение которого имеет полярность, заданную посредством извлеченного первого флага.

Согласно вышеупомянутому изобретению драйвер отображения извлекает, в соответствии с синхронизацией последовательного тактового сигнала, первый флаг из последовательных данных, подаваемых посредством последовательной передачи, определяет полярность напряжения общего электрода, в соответствии с первым флагом, и осуществляет отображение. Следовательно, драйвер отображения может генерировать синхросигнал для общего переменного напряжения посредством прямого управления последовательной передачей. Это избавляет от необходимости в тактовом генераторе или же в специализированном управляющем терминале для внешнего управления генерированием синхросигнала для общего переменного напряжения, благодаря чему предоставляется возможность сократить размеры схемы драйвера отображения.

Это реализует устройство отображения, которое может генерировать синхросигнал для общего переменного напряжения и имеет при этом малые размеры схемы.

Для достижения цели, в устройстве отображения настоящего изобретения каждый пиксел включает в себя память пиксела для сохранения данных изображения, поданных посредством драйвера отображения; в случае, если память пиксела сохраняет данные изображения, то последовательные данные включают в себя данные изображения, которые должны быть сохранены в памяти пиксела, и последовательные данные, имеющие добавленный в них первый флаг; и в случае, если отображаются данные изображения, сохраненные в памяти пиксела, то последовательные данные включают в себя, вместо данных изображения, которые должны быть сохранены в памяти пиксела, фиктивные данные, которые не должны подаваться на пикселы, и последовательные данные, имеющие добавленный в них первый флаг.

Согласно вышеупомянутому изобретению, в случае, если отображаются данные изображения, сохраненные в памяти пиксела, то первый флаг добавляется, вместо данных изображения, которые должны быть сохранены в памяти пиксела, к фиктивным данным, которые не должны подаваться на пикселы. Этот первый флаг делает возможным генерировать синхросигнал для общего переменного напряжения при отсутствии потребления энергии для подачи данных изображения на каждый из пикселов.

Для достижения цели, в устройстве отображения настоящего изобретения последовательные данные имеют добавленный в них второй флаг, указывающий, включают ли в себя последовательные данные данные изображения, которые должны быть сохранены в памяти пиксела; а драйвер отображения извлекает второй флаг из последовательных данных, в соответствии с синхронизацией последовательного тактового сигнала, и в случае, если второй флаг указывает, что последовательные данные включают в себя данные изображения, которые должны быть сохранены в памяти пиксела, то драйвер отображения извлекает данные изображения из последовательных данных и сохраняет данные изображения в памяти пиксела.

Согласно вышеупомянутому изобретению, из второго флага возможно узнать, что последовательные данные включают в себя данные изображения, которые должны быть сохранены в памяти пиксела. Посредством этого, исключительно в случае, когда последовательные данные включают в себя данные изображения, разрешается потреблять энергию для подачи данных изображения на каждый из пикселов.

Для достижения цели, в устройстве отображения настоящего изобретения последовательные данные имеют добавленный в них третий флаг, отдающий инструкцию, инициировать ли отображение всех пикселов; а драйвер отображения извлекает третий флаг из последовательных данных, в соответствии с синхронизацией последовательного тактового сигнала, и в случае, если инструкция третьего флага предназначена для инициирования отображения всех пикселов, то драйвер отображения инициирует отображение всех пикселов.

Согласно вышеупомянутому изобретению, из третьего флага возможно узнать, что должно быть инициировано отображение всех пикселов. Посредством этого возможно осуществить инициирование без включения в последовательные данные данных изображения для инициирования. Это избавляет от необходимости в индивидуальной подаче данных изображения на пикселы, что приводит к сокращению энергопотребления согласно количеству энергии для индивидуальной подачи данных изображения на пикселы.

Для достижения цели, в устройстве отображения настоящего изобретения первый флаг, добавляемый к последовательным данным, указывает синхронизацию для начала одного кадра.

Вышеупомянутое изобретение делает возможным инвертировать полярность напряжения общего электрода для каждого кадра.

Для достижения цели, в устройстве отображения настоящего изобретения, при последовательной передаче, последовательный сигнал выбора кристалла, указывающий, следует ли осуществлять отображение, то есть следует ли управлять драйвером отображения, передается по проводнику, отличающемуся от проводников для последовательных данных и последовательного тактового сигнала.

Согласно вышеупомянутому изобретению, посредством распознавания, из последовательного сигнала выбора кристалла, периода, в течение которого драйвер отображения не работает, драйвер отображения может прекратить загрузку последовательных данных. Следовательно, предоставляется возможность остановки последовательной передачи в течение этого периода, что приводит к сокращению энергопотребления согласно количеству энергии для последовательной передачи.

Для достижения цели, в устройстве отображения настоящего изобретения каждый пиксел включает в себя аналоговый переключатель, образованный из КМОП-схемы.

Согласно вышеупомянутому изобретению, аналоговый переключатель пиксела образован из КМОП-схемы. Это делает возможным управлять с использованием низкого напряжения даже устройством (например, TFT), имеющим высокое Vth (th - порог), и устанавливать одно и то же напряжение для сигнала управления и сигнала данных. Посредством этого предоставляется возможность сокращения амплитуды напряжения источника питания, используемого в управляющей схеме для дисплея, что сокращает энергопотребление.

Для достижения цели, в устройстве отображения настоящего изобретения драйвер отображения монолитно встроен в панель отображения.

Согласно вышеупомянутому изобретению, драйвер отображения, образованный из КМОП-схемы, монолитно формируется на панели отображения. Это предоставляет возможность сокращения размеров устройства отображения и упрощения процесса.

Для достижения цели, в устройстве отображения настоящего изобретения каждый пиксел включает в себя отображающий элемент, использующий полимерный диспергированный жидкий кристалл.

Согласно вышеупомянутому изобретению, полимерный диспергированный жидкий кристалл используется для отображающего элемента. Благодаря этому предоставляется возможность реализовать жидкокристаллическое устройство отображения с высокой яркостью, пренебрегая поляризационной пластиной и/или подобным, и дополнительно управлять таким жидкокристаллическим устройством отображения с использованием низкого напряжения. Это значительно сокращает энергопотребление, в частности, в устройстве отображения с низким энергопотреблением, включающем в себя память пиксела в пикселе.

Для достижения цели, в устройстве отображения настоящего изобретения каждый пиксел включает в себя отображающий элемент, использующий полимерный сетчатый жидкий кристалл.

Согласно вышеупомянутому изобретению, полимерный сетчатый жидкий кристалл используется для отображающего элемента. Благодаря этому, предоставляется возможность реализовать жидкокристаллическое устройство отображения с высокой яркостью, пренебрегая поляризационной пластиной и/или подобным, и дополнительно управлять таким жидкокристаллическим устройством отображения с использованием низкого напряжения. Это значительно сокращает энергопотребление, в частности, в устройстве отображения с низким энергопотреблением, включающем в себя память пиксела в пикселе.

Для достижения цели, в устройстве отображения настоящего изобретения драйвер отображения включает в себя синхрогенератор для генерирования синхросигнала для отображения, и синхрогенератор включает в себя последовательно-параллельный преобразователь для извлечения данных изображения и первого флага из последовательных данных.

Для достижения цели, в устройстве отображения настоящего изобретения драйвер отображения генерирует тактовый сигнал истока в соответствии с последовательными данными, последовательным тактовым сигналом и последовательным сигналом выбора кристалла, указывающим, следует ли осуществлять отображение, последовательный сигнал выбора кристалла подается посредством последовательной передачи, а драйвер отображения генерирует начальные импульсы истока в соответствии с первым флагом и тактовым сигналом истока, начальные импульсы истока подаются на сдвиговый регистр драйвера сигнальной линии данных.

Для достижения цели, в устройстве отображения настоящего изобретения начальные импульсы истока, генерируемые посредством драйвера отображения в соответствии с первым флагом и тактовым сигналом истока, включают в себя начальный импульс истока для исходного периода горизонтального отображения, а драйвер отображения подает начальный импульс истока в течение исходного периода горизонтального отображения на сдвиговый регистр, и начальные импульсы истока, генерируемые посредством драйвера отображения в соответствии с первым флагом и тактовым сигналом истока, включают в себя начальные импульсы истока для второго периода горизонтального отображения и последующего периода горизонтального отображения, начальные импульсы истока которого генерируются далее в соответствии с выходным сигналом оконечного каскада сдвигового регистра, а драйвер отображения подает начальные импульсы истока для второго периода горизонтального отображения и последующего периода горизонтального отображения на сдвиговый регистр.

Для достижения цели, в устройстве отображения настоящего изобретения последовательные данные имеют добавленный в них второй флаг, указывающий, включают ли в себя последовательные данные данные изображения, которые должны быть сохранены в памяти пиксела, последовательно-параллельный преобразователь извлекает второй флаг из последовательных данных в соответствии с синхронизацией последовательного тактового сигнала, и, в соответствии с первым флагом, вторым флагом, выходным сигналом оконечного каскада сдвигового регистра и последовательным сигналом выбора кристалла, драйвер отображения подает на драйвер сигнальной линии сканирования тактовый сигнал затвора, начальный импульс затвора и сигнал запуска затвора, отдающий инструкцию, сохранять ли в памяти пиксела данные, которые драйвер сигнальной линии данных выводит на сигнальную линию данных.

Для достижения цели, мобильный терминал настоящего изобретения включает в себя устройство отображения, служащее в качестве модуля отображения.

Благодаря вышеупомянутому изобретению предоставляется возможность свободного удовлетворения требований для мобильных терминалов с низким энергопотреблением.

Для более полного понимания сущности и преимуществ изобретения должна быть сделана ссылка на следующее подробное описание, изложенное при содействии сопроводительных чертежей.

Краткое описание чертежей

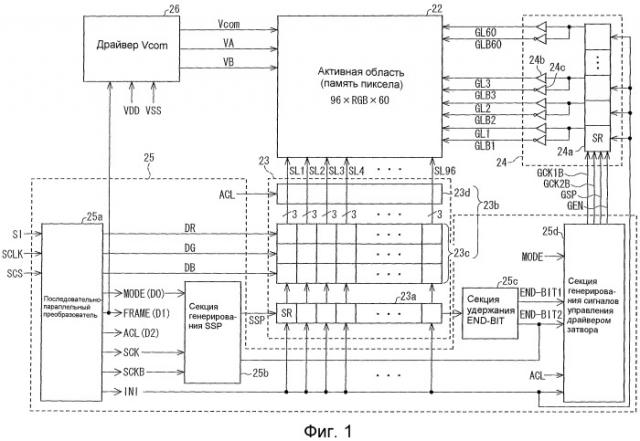

Фиг.1, относящаяся к варианту осуществления настоящего изобретения, является блок-схемой, показывающей, как основные части устройства отображения соединены друг с другом.

Фиг.2 является временной диаграммой, показывающей форму колебаний каждого сигнала для последовательной передачи в режиме обновления данных.

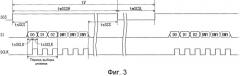

Фиг.3 является временной диаграммой, показывающей форму колебаний каждого сигнала для последовательной передачи в режиме отображения.

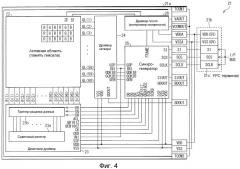

Фиг.4 является блок-схемой, показывающей всю структуру устройства отображения.

Фиг.5 является электрической схемой, показывающей структуру пиксела и памяти пиксела.

Фиг.6 является временной диаграммой, показывающей форму колебаний выходного сигнала драйвера Vcom.

Фиг.7 является принципиальной схемой, показывающей структуру последовательно-параллельного преобразователя.

Фиг.8 является принципиальной схемой, показывающей структуру секции удержания END-BIT (конечного бита).

Фиг.9 является принципиальной схемой, показывающей структуру секции генерирования начальных импульсов истока.

Фиг.10 является принципиальной схемой, показывающей структуру секции генерирования сигналов управления драйвером затвора.

Фиг.11 является принципиальной схемой, показывающей структуру драйвера Vcom.

Фиг.12 является временной диаграммой, показывающей форму колебаний каждого сигнала последовательно-параллельного преобразователя.

Фиг.13 является временной диаграммой, показывающей форму колебаний каждого сигнала секции генерирования сигналов управления драйвером затвора.

Фиг.14 является блок-схемой, показывающей структуру устройства отображения традиционной технологии.

Фиг.15 является блок-схемой, показывающей структуру мобильного телефона традиционной технологии.

Фиг.16 является блок-схемой, показывающей структуру драйвера отображения традиционной технологии.

Перечень ссылочных позиций

21: Жидкокристаллическое устройство отображения (устройство отображения)

23: Двоичный драйвер

23a: Сдвиговый регистр (сдвиговый регистр драйвера сигнальной линии данных)

23b: Триггер-защелка данных

24: Драйвер затвора

24a: Сдвиговый регистр (сдвиговый регистр драйвера сигнальной линии сканирования)

25: Синхрогенератор

26: Драйвер Vcom

30: Память пиксела

D0: Флаг (второй флаг)

Dl: Флаг (первый флаг)

D2: Флаг (третий флаг)

GCKB1 и GCKB2: Тактовые сигналы затвора (синхросигналы, подаваемые на вход сдвигового регистра драйвера сигнальной линии затвора)

GEN: Сигнал запуска затвора (синхросигнал, подаваемый на вход сдвигового регистра драйвера сигнальной линии затвора)

SCK и SCKB: Тактовые сигналы (синхросигналы, подобные тактовым сигналам для оперирования сдвиговым регистром драйвера сигнальной линии данных)

SSP: Начальный импульс истока (синхросигнал для периода горизонтального отображения)

I/F BUS: Последовательная интерфейсная шина

SI: Последовательные данные

SCLK: Последовательный тактовый сигнал

SCS: Сигнал выбора кристалла

SL: Линия истока (сигнальная линия данных)

Vcom: Общий выходной сигнал (напряжение общего электрода)

Описание вариантов осуществления

Далее, со ссылкой на Фиг. 1-13, описывается вариант осуществления настоящего изобретения.

Фиг.4 показывает структуру жидкокристаллического устройства 21 отображения (устройства отображения) настоящего варианта осуществления.

Жидкокристаллическое устройство 21 отображения является модулем отображения, включенным в мобильный терминал, такого как мобильный телефон, и включает в себя панель 21a отображения и гибкую печатную плату 21b (FPC). Панель 21a отображения имеет различные схемы, монолитно заключенные в нее. Гибкая печатная плата 21b принимает последовательные данные SI, последовательный сигнал SCS выбора кристалла и последовательный тактовый сигнал SCLK, подаваемый посредством последовательной передачи при помощи последовательной интерфейсной шины BUS I/F с тремя линиями, которая управляется посредством CPU, такого как прикладной процессор, и подает последовательные данные SI, последовательный сигнал SCS выбора кристалла и последовательный тактовый сигнал SCLK на панели 21a отображения через плату FPC терминала 21c. Последовательной передачей возможно управлять посредством другого управляющего средства, такого как микроконтроллер. Дополнительно, гибкая печатная плата 21b подает 5 вольт источника VDD питания и 0 вольт источника VSS питания, которые подаются извне, на панель 21a отображения через плату FPC терминала 21c.

Панель 21a отображения включает в себя активную область 22, двоичный драйвер 23 (драйвер сигнальной линии передачи данных), драйвер 24 затвора (драйвер сигнальной линии сканирования), синхрогенератор 25 и драйвер 26 Vcom. Двоичный драйвер 23, драйвер 24 затвора, синхрогенератор 25 и драйвер 26 Vcom составляют драйвер отображения.

Активная область 22 является, например, областью, в которой в матрице 96 x RGB х 60 располагаются пикселы RGB, и каждый из пикселов включает в себя память пиксела. Двоичный драйвер 23 является схемой для подачи данных изображения в активную область 22 по линии истока, и включает в себя сдвиговый регистр 23a и триггер-защелку 23b данных. Драйвер 24 затвора из пикселов, находящихся в активной области 22, выбирает по линии затвора пиксел, на который должны подаваться данные изображения. Синхрогенератор 25 генерирует сигнал, который будет подан на двоичный драйвер 23, драйвер 24 затвора и драйвер 26 Vcom, в соответствии с сигналом, подаваемым с гибкой печатной платы 21b.

Фиг.5 показывает структуру каждого пиксела PIX, располагаемого в активной области 22, и подробно показывает схему памяти пиксела.

Пиксел PIX включает в себя емкость CL жидкого кристалла, память 30 пиксела и аналоговые переключатели 31, 33 и 34. Память 30 пиксела дополнительно включает в себя аналоговый переключатель 32 и инверторы 35 и 36.

В данном случае емкость CL жидкого кристалла формируется между полярным выходом OUT и общим выходом Vcom (который является напряжением общего электрода) с использованием жидкого кристалла дисперсионного типа, такого как PDLC (полимерный диспергированный жидкий кристалл) или PNLC (полимерный сетчатый жидкий кристалл). Каждый из аналоговых переключателей 31-34 и инверторов 35 и 36 составлен посредством КМОП-схемы.

Аналоговый переключатель 31 располагается между выходом SL линии истока и памятью 30 пиксела, и включает в себя (i) p-МОП транзистор 31а, затвор которого соединяется с инвертированным выходом GLB линии затвора, и (ii) n-МОП транзистор 31b, затвор которого соединяется с выходом GL линии затвора. Аналоговый переключатель 32 из памяти 30 пиксела располагается между входом инвертора 35 и выходом инвертора 36, и включает в себя (i) p-МОП транзистор 32a, затвор которого соединяется с выходом линии затвора, и (ii) n-МОП транзистор 32b, затвор которого соединяется с инвертированным выходом GLB линии затвора. Вход инвертора 35 соединяется с клеммой аналогового переключателя 31, клемма которого находится на стороне, противоположной по отношению к стороне, на которой соединен выход SL линии истока. Выход инвертора 35 соединяется со входом инвертора 36. Каждый из инверторов 35 и 36 использует источник VDD питания в качестве источника питания с "высоким" уровнем мощности, а источник VSS питания в качестве источника питания с "низким" уровнем мощности.

Аналоговый переключатель 33 располагается между полярным выходом VA для отображения черного цвета и полярным выходом OUT, и включает в себя (i) p-МОП транзистор 33a, затвор которого соединяется с выходом инвертора 35, и (ii) n-МОП транзистор 33b, затвор которого соединяется со входом инвертора 35. Аналоговый переключатель 34 располагается между полярным выходом VB для отображения белого цвета и полярным выходом OUT, и включает в себя (i) p-МОП транзистор 34a, затвор которого соединяется со входом инвертора 35, и (ii) n-МОП транзистор 34b, затвор которого соединяется с выходом инвертора 35.

Фиг.6 показывает соответствующие формы колебаний общего выходного сигнала Vcom, полярного выхода VA для отображения черного цвета, и полярного выхода VB для отображения белого цвета. Эти сигналы генерируются посредством драйвера 26 Vcom. Общий выходной сигнал Vcom образует 5Vp-p импульсную форму колебаний, при которой переключение между положительной полярностью и отрицательной полярностью происходит в каждом кадре. Цикл для переключения полярности может быть установлен по желанию. Например, такое переключение может происходить в каждом предварительно определенном периоде горизонтального отображения. Полярный выход VA для отображения черного цвета имеет 5Vp-p импульсную форму колебаний, находящуюся в противофазе с таковой для общего выходного сигнала Vcom. Полярный выход VB для отображения белого цвета (в случае обычного белого цвета) имеет 5Vp-p импульсную форму колебаний, синфазную с таковой для общего выходного сигнала Vcom.

На Фиг.5, в случае, если высокий уровень (5 В) выдается в качестве выхода SL линии истока из двоичного драйвера 23, то пиксел PIX выбирается посредством высокого уровня (5 В) выхода GL линии затвора и низкого уровня (0 В) инвертированного выхода GLB линии затвора, чтобы аналоговый переключатель 31, который выбирает пиксел PIX, становился токопроводящим. Благодаря этому, аналоговый переключатель 33 становится токопроводящим, а аналоговый переключатель 34 блокируется. Следовательно, полярный выход VA для отображения черного цвета выдается на полярный выход OUT, а на емкость CL жидкого кристалла подается 5 В, которые отличаются по напряжению между полярным выходом VA для отображения черного цвета и общим выходом Vcom. В результате чего пиксел PIX переходит в состояние отображения черного цвета.

Следовательно, когда выход GL линии затвора имеет низкий уровень (0 В), а инвертированный выход GLB линии затвора имеет высокий уровень (5 В), аналоговый переключатель 31 блокируется, а аналоговый переключатель 32 становится токопроводящим. Соответственно, высокий уровень сохраняется в памяти 30 пиксела. Сохраненные данные хранятся до тех пор, пока этот пиксел PIX не будет выбран снова, а аналоговый переключатель 31 не станет токопроводящим.

При этом, на Фиг.5, в случае, если низкий уровень (0 В) выдается в качестве выхода SL линии истока из двоичного драйвера 23, пиксел PIX выбирается посредством высокого уровня (5 В) выхода линии затвора и низкого уровня (0 В) инвертированного выхода GLB линии затвора, чтобы аналоговый переключатель 31 выбранного пиксела PIX становился токопроводящим. Благодаря этому, аналоговый переключатель 33 блокируется, а аналоговый переключатель 34 становится токопроводящим. Соответственно, полярный выход VB для отображения белого цвета выдается на полярный выход OUT, а на емкость CL жидкого кристалла подается 0 В, которые отличаются по напряжению между полярным выходом VB для отображения белого цвета и общим выходом Vcom. В результате чего пиксел PIX переходит в состояние отображения белого цвета.

Следовательно, когда выход GL линии затвора имеет низкий уровень (0 В), а инвертированный выход GLB линии затвора имеет высокий уровень (5 В), аналоговый переключатель 31 блокируется, а аналоговый переключатель 32 становится токопроводящим. Соответственно, низкий уровень сохраняется в памяти 30 пиксела. Сохраненные данные хранятся до тех пор, пока этот пиксел PIX не будет выбран снова, а аналоговый переключатель 31 не станет токопроводящим.

Фиг.1 показывает способ соединения синхрогенератора 25, двоичного драйвера 23, драйвера 24 затвора и драйвера 26 Vcom.

Синхрогенератор 25 включает в себя последовательно-параллельный преобразователь 25a, секцию 25b генерирования начальных импульсов истока, секцию 25с удержания конечного бита END-BIT, и секцию 25d генерирования сигналов управления драйвером затвора. Синхрогенератор 25 генерирует режимный сигнал MODE, кадровый сигнал FRAME, сигнал ACL общей очистки, тактовые сигналы SCK и SCKB истока (синхросигналы, каждый из которых служит в качестве тактового сигнала для оперирования сдвиговым регистром драйвера сигнальной линии передачи данных), начальный импульс SSP истока (синхросигнал для периода горизонтального отображения), тактовые сигналы GCK1B и GCK2B затвора (синхросигналы, каждый из которых подается на сдвиговый регистр драйвера сигнальной линии затвора), начальный импульс GSP затвора, сигнал GEN запуска затвора (синхросигнал, подаваемый на сдвиговый регистр драйвера сигнальной линии затвора) и исходный сигнал INI, в соответствии с последовательными данными SI, последовательным тактовым сигналом SCLK и последовательным сигналом SCS выбора кристалла, которые подаются извне панели. Синхрогенератор 25 подает начальный импульс SSP истока и исходный сигнал INI на двоичный драйвер 23. Синхрогенератор 25 подает тактовые сигналы GCK1B и GCK2B затвора, начальный импульс GSP затвора, сигнал GEN запуска затвора и исходный сигнал INI на драйвер 24 затвора. Синхрогенератор 25 подает кадровый сигнал FRAME на драйвер 26 Vcom. В данном случае тактовые сигналы SCK и SCKB истока используются в синхрогенераторе 25. Однако, как будет описано позже, тактовые сигналы SCK и SCKB истока используются для генерирования начального импульса SSP истока в каждом периоде горизонтального отображения и являю