Генератор биективных криптографических математических функций

Иллюстрации

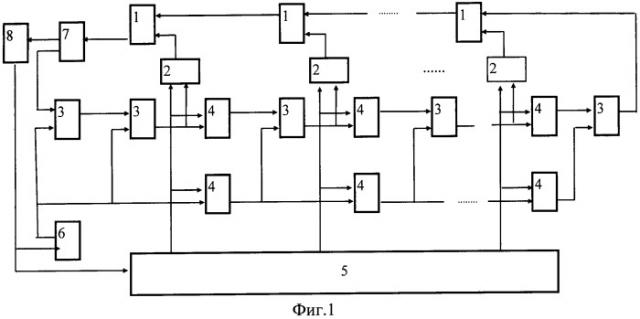

Показать всеИзобретение относится к генераторам биективных криптографических математических функций. Технический результат заключается в повышении защиты информации за счет генерирования биективных функций последовательностями n-ичных двоичных элементов из поля Галуа GF (2n). Генератор содержит (2n) n-разрядных регистров памяти, (2n-2) - схем ИЛИ, (2n-2) - схем И, 2(2n-2) - схем «Запрет», дешифратор, тактовый генератор импульсов, выход которого соединен с первыми входами первого и второго регистров памяти, с первыми входами третьего и т.д. (2n)-го регистра через вторые входы и выходы соответствующих схем «Запрет», выходы дешифратора, соединены с первыми входами соответствующих схем «Запрет», выход первого регистра соединен с вторым входом второго регистра памяти, выход второго регистра соединен через второй вход и выход схемы «Запрет» с вторым входом третьего регистра и через второй вход и выход первой схемы «И» с первым входом первой схемы «ИЛИ», выход которой соединен через первый выход схемы со вторым входом первого регистра, и т.д. выход (2n-1)-го регистра соединен с вторым входом (2n)-го регистра памяти. Генератор также содержит блок проверки на четность, соединенной с выходом первой схемы «ИЛИ», первый выход которого соединен со вторым входом первого регистра, а второй выход соединен с дешифратором через дополнительно введенный блок анализа. 2 ил.

Реферат

Изобретение относится к области защиты информации управления в каналах передачи данных и может применяться в соответствующих схемах при криптографическом преобразовании.

Наиболее близким по технической сущности к заявляемому изобретению является устройство защиты информации (RU 2206120, 7 G06F 12/14 от 15.11.2001), содержащее генератор тактовых импульсов, вход которого является пусковым входом, а выход соединен со счетчиком, выход которого соединен с дешифратором. Дешифратор содержит n-выходов, соединенных с (2n-2)-схем И, 2(2n-2)-схем «Запрет», которые открываются/закрываются при поступлении импульсов. Сдвиг информации, записанной в (2n) n-разрядных регистров памяти осуществляется по схеме Р1-Р2-Р1 при поступлении 1-го импульса, Р1-Р2-Р3-…-Р2n-Р1 при поступлении импульса с номером (2n-2)!. Период работы устройства - (2n-2)!. Недостаток функционирования устройства защиты информации состоит в том, что отсутствует контроль на четность текущей функции устройства, что позволяет нарушителю идентифицировать текущую функцию, увеличивая вероятность ее распознавания.

Задачей изобретения является - создание устройства такой конструкции, которая позволит повысить скрытность информации, а также осуществить дистанционную смену порядка записи элементов поля Галуа GF (2n) в регистрах памяти и проверку их на четность.

Решение данной задачи достигается тем, что в устройство, содержащее (2n) n-разрядных регистров памяти, (2n-2)-схем ИЛИ, (2n-2)-схем И, 2(2n-2)-схем «Запрет», дешифратор, тактовый генератор импульсов, дополнительно введены блок проверки на четность и блок анализа со следующими связями: выход тактового генератора импульсов соединен с первыми входами первого и второго регистров памяти, с первыми входами третьего и т.д. (2n)-го регистра через вторые входы и выходы соответствующих схем «Запрет», выходы дешифратора, соединены с первыми входами соответствующих схем «Запрет», выход первого регистра соединен с вторым входом второго регистра памяти, выход второго регистра соединен через второй вход и выход схемы «Запрет» с вторым входом третьего регистра и через второй вход и выход первой схемы «И» с первым входом первой схемы «ИЛИ», выход которой соединен через первый выход схемы со вторым входом первого регистра, и т.д. выход (2n-1)-го регистра соединен с вторым входом (2n)-го регистра памяти, отличающееся тем, что в устройство дополнительно введен блок проверки на четность, первый выход которого соединен со вторым входом первого регистра, а второй выход соединен с дешифратором через дополнительно введенный блок анализа, выход которого является результатом контроля. Вход тактового генератора импульсов является выходом блока анализа, по которому формируется пусковой вход генератора биективных криптографических математических функций (БКМФ), а выход соединен с первыми входами соответствующих схем «И» и схем «Запрет», второй выход тактового генератора импульсов соединен с первыми входами первого и второго регистров памяти, с первыми входами третьего и т.д. (2n)-го регистра через вторые входы и выходы соответствующих схем «Запрет», выход первого регистра соединен с вторым входом второго регистра памяти, выход второго регистра соединен через второй вход и выход схемы «Запрет» с вторым входом третьего регистра и через второй вход и выход первой схемы «И» с первым входом первой схемы «ИЛИ», выход которой соединен через первый выход схемы проверки на четность с вторым входом первого регистра, и т.д. выход (2n-1)-го регистра соединен с вторым входом (2n)-го регистра памяти, выход которого соединен через соответствующие схемы «ИЛИ» и блок проверки на четность с вторым входом первого регистра, второй выход блока проверки на четность соединен с блоком анализа.

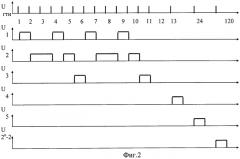

Устройство работает следующим образом: в исходном состоянии в регистры памяти записываются все элементы из поля GF (2n). Импульсы тактового генератора представляют собой две последовательности, сдвинутые друг относительно друга на полпериода. Посредством управляющих импульсов осуществляется формирование на выходе дешифратора сигналов, управляющих схемой сдвига. При этом управление осуществляется по методу последовательного распределения информации по ячейкам регистров памяти таким образом, что на этих ячейках осуществляется генерация всего множества М биективных функций, входящих в группу. Процесс генерации осуществляется по типу рекурсивного процесса воспроизведения функций. Цикличность работы генератора биективных криптографических математических функций определяется периодом 2n!, где n - параметр поля Галуа GF (2n). Первая единица, записанная в счетчик, формирует на выходе дешифратора сигнал, по которому открывается первая схема «И». Этим же сигналом закрывается соответствующие схемы «Запрет». Первый сдвигающий импульс тактового генератора осуществляет сдвиг информации по схеме первый регистр - второй регистр - первый регистр (P1-Р2-Р1). Второй управляющий импульс, поступающий на дешифратор, приводит к закрытию первой схемы «И» и открывает вторую «И», при этом все остальные схемы «И» свое состояние не меняют. Аналогично открываются схемы «Запрет», соединенные с первым выходом дешифратора и закрываются схемы «Запрет», соединенные с его вторым выходом. Второй сдвигающий импульс осуществляет сдвиг информации по схеме P1-Р2-Р3-Р1. Последующий управляющий импульс не приводит к изменению выходов дешифратора, так что третий сдвиг информации осуществляется по схеме второго импульса. Четвертая пара импульсов приводит к схеме сдвига аналогично второй и третьей парам. При поступлении шестого управляющего импульса дешифратор открывает третью схему «И» (все остальные схемы «И» закрыты) и сдвиг информации по 6 импульсу сдвига осуществляется по схеме P1-Р2-Р3-Р4-Р1. При последующих в парах импульсов сдвиг в регистрах P1-Р4 осуществляется аналогичным образом и т.д. до прихода 24 пары импульсов. При получении счетчиком 24 управляющего импульса дешифратор открывает 4 схему «И» и закрывает соответствующую схему «Запрет», при этом остальные схемы «И» закрыты. Начиная с 25-й пары импульсов, процесс сдвига информации осуществляется аналогичным образом пять раз подряд. При получении 120 импульса открывается пятая схема «И» (все остальные схемы «И» закрыты) и сдвиг информации осуществляется по схеме Р1-…-Р6-P1. По аналогичной схеме открывается 6 схема «И» на 720 управляющем импульсе, 7 схема «И» на (720×7) управляющем импульсе и т.д. до импульса с номером (2n-2)!, при котором открывается (2n-2) схема «И» и сдвиг осуществляется по полному циклу Р1-…-Р2n-Р1. После этого работа схемы повторяется вновь по указанному циклу, так что период работы генератора - (2n-2)!

Требуемый технический результат достигается повышением защищенности информации за счет генерирования биективных криптографических математических функций последовательностями n-двоичных элементов из поля Галуа GF (2n), записанных последовательно в регистры памяти с последующей проверкой на четность. Устройство содержит (2n) n-разрядных регистров памяти, (2n-2)-схем ИЛИ, (2n-2)-схем И, 2(2n-2)-схем «Запрет», дешифратор, счетчик, тактовый генератор импульсов, блок проверки на четность и блок анализа.

Сущность изобретения поясняется чертежом, где представлена структурная схема генератора биективных криптографических математических функций (БКМФ):

1 - схемы «ИЛИ»;

2 - схемы «И»;

3 - n-разрядные регистры памяти;

4 - схемы «Запрет»;

5 - дешифратор;

6 - тактовый генератор импульсов;

7 - блок проверки на четность;

8 - блок анализа.

На фиг.2 представлены временные диаграммы работы генератора БКМФ, показывающие изменение напряжения на регистрах сдвига во времени. Совокупность состояний указанных регистров формирует полное множество биективных криптографических математических функций над полем Галуа GF (2n).

Сравнительный анализ с прототипом показал, что новое техническое решение отличается от прототипа наличием новых блоков: блока проверки на четность и блока анализа, что соответствует новизне.

Идентификация нарушителем текущей функции генератора по результатам наблюдений ее значений на i-м шаге наблюдения в силу равновероятности генерации любой биективной функции из М определяется выражением:

Таким образом, требуемая степень скрытности информации в КПД АСУ обеспечивается соответствующим выбором числа компонентов биективных функций. Так, например, при n=5, полное множество биективных функций М=2,63*1035, а вероятность распознавания текущей функции генератора на первом шаге: P1=3,8*10-36.

Генератор биективных криптографических математических функций, содержащий (2n) n-разрядных регистров памяти, (2n-2) - схем ИЛИ, (2n-2) - схем И, 2(2n-2) - схем «Запрет», дешифратор, тактовый генератор импульсов, выход которого соединен с первыми входами первого и второго регистров памяти, с первыми входами третьего и т.д. (2n)-го регистра через вторые входы и выходы соответствующих схем «Запрет», выходы дешифратора соединены с первыми входами соответствующих схем «Запрет», выход первого регистра соединен с вторым входом второго регистра памяти, выход второго регистра соединен через второй вход и выход схемы «Запрет» с вторым входом третьего регистра и через второй вход и выход первой схемы «И» с первым входом первой схемы «ИЛИ», выход которой соединен через первый выход схемы со вторым входом первого регистра, и т.д. выход (2n-1)-го регистра соединен с вторым входом (2n)-го регистра памяти, отличающийся тем, что в устройство дополнительно введен блок проверки на четность, соединенной с выходом первой схемы «ИЛИ», первый выход которого соединен со вторым входом первого регистра, а второй выход соединен с дешифратором через дополнительно введенный блок анализа.