Дифференциальный операционный усилитель с парафазным выходом

Иллюстрации

Показать всеИзобретение относится к области радиотехники и связи и может быть использовано в качестве устройства усиления аналоговых сигналов, в структуре аналоговых микросхем различного функционального назначения (например, мостовых усилителях мощности, фильтрах, компараторах т.п.). Технический результат заключается в создании условий, при которых выходное статическое синфазное напряжение ДУ будет иметь высокую стабильность и близкое к нулю значение. Дифференциальный операционный усилитель с парафазным выходом содержит входной дифференциальный каскад, первое и второе токовые зеркала, первый токостабилизирующий двухполюсник, первый и второй токостабилизирующие двухполюсники нагрузки, дополнительный транзистор, первый и второй резисторы обратной связи, первый и второй дополнительные буферные усилители. 9 ил.

Реферат

Изобретение относится к области радиотехники и связи и может быть использовано в качестве устройства усиления аналоговых сигналов, в структуре аналоговых микросхем различного функционального назначения (например, мостовых усилителях мощности, фильтрах, компараторах и т.п.).

Известны схемы классических двухкаскадных дифференциальных операционных усилителей (ДУ) на основе токовых зеркал с парафазным выходом, которые стали основой многих серийных аналоговых микросхем [1-11]. ДУ данного класса активно применяются и в структуре СВЧ-устройств, реализованных на базе SiGe-технологий. Это связано с возможностью построения на их основе активных RС-фильтров гигагерцового диапазона для современных и перспективных систем телекоммуникаций, драйверов дифференциальных линий связи между СФ-блоками A/d или a/D классов и т.н.

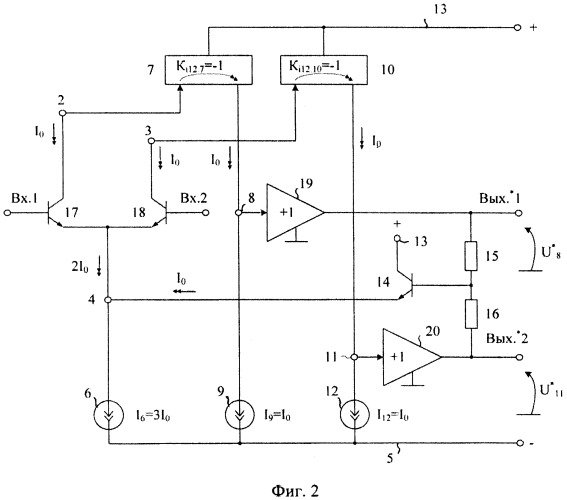

Ближайшим прототипом (фиг.1) заявляемого устройства является дифференциальный усилитель по патентной заявке US 2006/0006910, содержащий входной дифференциальный каскад 1 с первым 2 и вторым 3 токовыми выходами и низкоомным выходом 4 общей эмиттерной цепи, связанным с шиной первого 5 источника питания через первый 6 токостабилизирующий двухполюсник, первое 7 токовое зеркало, вход которого подключен к первому 2 токовому выходу входного дифференциального каскада 1, а выход соединен с первым 8 вспомогательным выходом устройства и через первый 9 токостабилизирующий двухполюсник нагрузки соединен с шиной первого 5 источника питания, второе 10 токовое зеркало, вход которого соединен со вторым 3 токовым выходом входного дифференциального каскада 1, а выход соединен со вторым 11 вспомогательным выходом устройства и через второй 12 токостабилизирующий двухполюсник нагрузки соединен с шиной первого 5 источника питания, причем шина второго 13 источника питания связана с общими эмиттерными выходами первого 7 и второго 10 токовых зеркал.

Существенный недостаток известного ДУ фиг.1 состоит в том, что при низкоомной нагрузке (например, Rн=4 Ом), подключенной к выходам 8 и 12, а также реализации опции rail-to-rail, он имеет нестабильный уровень выходного синфазного напряжения, зависящий от Rн и параметров токостабилизирующих двухполюсников 9, 12, 6. Это значительно затрудняет его согласование с последующими функциональными узлами, не позволяет реализовывать на его основе мостовые усилители мощности ВЧ и СВЧ диапазона.

Основная задача предлагаемого изобретения состоит в создании условий, при которых выходное статическое синфазное напряжение ДУ будет иметь высокую стабильность и близкое к нулю значение при низкоомных нагрузках (1÷4 Ом). В этом случае реализуется также более широкий диапазон изменения выходного сигнала ДУ.

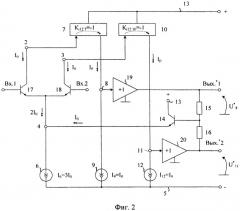

Поставленная задача решается тем, что в дифференциальном операционном усилителе с парафазным выходом фиг.1, содержащем входной дифференциальный каскад (1) с первым (2) и вторым (3) токовыми выходами и низкоомным выходом (4) общей эмиттерной цепи, связанным с шиной первого (5) источника питания через первый (6) токостабилизирующий двухполюсник, первое (7) токовое зеркало, вход которого подключен к первому (2) токовому выходу входного дифференциального каскада (1), а выход соединен с первым (8) вспомогательным выходом устройства и через первый (9) токостабилизирующий двухполюсник нагрузки соединен с шиной первого (5) источника питания, второе (10) токовое зеркало, вход которого соединен со вторым (3) токовым выходом входного дифференциального каскада (1), а выход соединен со вторым (11) вспомогательным выходом устройства и через второй (12) токостабилизирующий двухполюсник нагрузки соединен с шиной первого (5) источника питания, причем шина второго (13) источника питания связана с общими эмиттерными выходами первого (7) и второго (10) токовых зеркал, предусмотрены новые элементы и связи - в схему введен дополнительный транзистор (14), эмиттер которого соединен с низкоомным выходом (4) общей эмиттерной цепи входного дифференциального каскада (1), а коллектор подключен к шине второго (13) источника питания, причем первый (8) вспомогательный выход устройства связан с базой дополнительного транзистора (14) через последовательно соединенные первый (19) дополнительный буферный усилитель и первый (15) резистор обратной связи, а второй (11) вспомогательный выход устройства связан с базой дополнительного транзистора (14) через последовательно соединенные второй (20) дополнительный буферный усилитель и второй (16) резистор обратной связи.

На чертеже фиг.1 показана схема ДУ-прототипа.

На чертеже фиг.2 показана схема заявляемого устройства в соответствии с формулой изобретения.

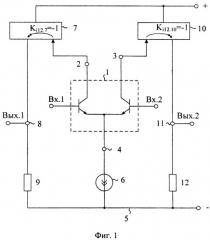

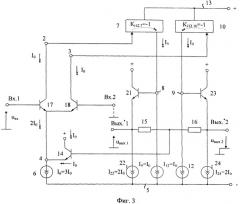

На чертеже фиг.3 показана схема заявляемого ДУ с архитектурой фиг.3, в котором дополнительные буферные усилители 19 и 20 выполнены в частном случае на основе транзистора 21 и двухполюсника 22, а также транзистора 23 и двухполюсника 24.

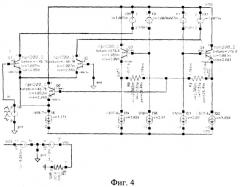

На чертеже фиг.4 показана схема заявляемого ДУ фиг.3 в среде компьютерного моделирования Cadance на моделях SiGe интегральных транзисторов, а на чертеже фиг.5 - зависимость его коэффициента усиления по напряжению от частоты.

На чертеже фиг.6 представлена зависимость выходных напряжений для парафазных и дифференциальных выходов ДУ фиг.4 от входного синусоидального напряжения с амплитудой uвх=1 мВ. Графики фиг.6 показывают, что заявляемый ДУ имеет два противофазных выходных напряжения и нулевой уровень выходного синфазного статического напряжения.

На чертеже фиг.7 приведена схема включения предлагаемого ДУ в структуре драйвера дифференциальной линии связи.

По чертеже фиг.8 приведена конкретная схема драйвера фиг.7 на основе ДУ фиг.4 в среде Cadence на моделях интегральных SiGe транзисторов, а на чертеже фиг.9 - частотная зависимость ее дифференциального коэффициента усиления.

Дифференциальный операционный усилитель с парафазмым выходом фиг.2 содержит входной дифференциальный каскад 1 с первым 2 и вторым 3 токовыми выходами и низкоомным выходом 4 общей эмиттерной цепи, связанным с шиной первого 5 источника питания через первый 6 токостабилизирующий двухполюсник, первое 7 токовое зеркало, вход которого подключен к первому 2 токовому выходу входного дифференциального каскада 1, а выход соединен с первым 8 вспомогательным выходом устройства и через первый 9 токостабилизирующий двухполюсник нагрузки соединен с шиной первого 5 источника питания, второе 10 токовое зеркало, вход которого соединен со вторым 3 токовым выходом входного дифференциального каскада 1, а выход соединен со вторым 11 вспомогательным выходом устройства и через второй 12 токостабилизирующий двухполюсник нагрузки соединен с шиной первого 5 источника питания, причем шина второго 13 источника питания связана с общими эмиттерными выходами первого 7 и второго 10 токовых зеркал. В схему введен дополнительный транзистор (14), эмиттер которого соединен с низкоомным выходом (4) общей эмиттерной цепи входного дифференциального каскада (1), а коллектор подключен к шине второго (13) источника питания, причем первый (8) вспомогательный выход устройства связан с базой дополнительного транзистора (14) через последовательно соединенные первый (19) дополнительный буферный усилитель и первый (15) резистор обратной связи, а второй (11) вспомогательный выход устройства связан с базой дополнительного транзистора (14) через последовательно соединенные второй (20) дополнительный буферный усилитель и второй (16) резистор обратной связи.

На чертеже фиг.3 показана схема заявляемого ДУ с архитектурой фиг.2, в котором дополнительные буферные усилители 19 и 20 выполнены в частном случае на основе транзистора 21 и двухполюсника 22, а также транзистора 23 и двухполюсника 24.

В качестве первого 6 токостабилизирующего двухполюсника авторы рекомендуют использовать классические источники опорного тока на транзисторах или сравнительно высокоомные резисторы.

Первый 9 и второй 12 токостабилизирующие двухполюсники нагрузки реализуются в виде источников опорного тока на транзисторах.

Токовые зеркала 7 и 10 выполняются по классическим схемам.

Рассмотрим работу ДУ фиг.2.

Статический режим по току транзисторов 14, 17 и 18 предлагаемого ДУ устанавливается двухполюсниками 6, 9 и 12. Причем коллекторные и эмиттерные токи транзисторов 17, 18 и 14 определяются по формулам:

где I0 - заданное значение статического тока, например 1 мА.

Статическое напряжение U*8 на выходе Вых.*1 и U*11 на Вых.*2 ДУ при нулевом входном сигнале (uвх=0) можно найти из уравнения:

где Uэб.17=Uэб.18=Uэб.14 - напряжение «эмиттер-база» входных транзисторов 17 и 18 и дополнительного транзистора 14 при токе эмиттера Iэi=I0;

Iб - составляющая тока базы транзистора 14 в резисторе обратной связи 15 (16).

Таким образом, во-первых, при низкоомных нагрузках Rн, подключаемых к выходам Вых*.1 и Вых*.2 (Rн=1÷4 Ом), и типовых значениях тока базы транзистора 14, а также при R15=R16=50÷100 Ом выходное синфазное напряжение ДУ фиг.2 практически равно нулю в широком диапазоне температурных и радиационных воздействий, а также изменений напряжений питания.

Во-вторых, рассматриваемый ДУ обеспечивает предельно возможные (при низкоомных нагрузках Rн=1÷4 Ом, подключаемых к выходам Вых*.1 и Вых*.2) противофазные напряжения на выходах, близкие к соответствующим напряжениям питания Е13 и Е5. При этом численные значения Rн в заявляемой схеме достаточно слабо влияют на нулевой уровень выходного синфазного сигнала ДУ. Данный эффект в ДУ-прототипе не реализуется.

При синфазном изменении напряжений на входах Вх.1 и Вх.2 изменяются синфазно и напряжения на выходах Вых*.1 и Вых.*2. Однако при этом эмиттерный (коллекторный) ток транзистора 14 остается постоянным:

Поэтому коэффициент ослабления входных синфазных напряжений в заявляемом ДУ достаточно высок, так как режим по току транзисторов 17 и 18 не изменяется.

Таким образом, наличие дополнительных буферных усилителей 19 и 20 значительно снижает требования к величине сопротивлений резисторов обратной связи 15 и 16, что позволяет получить на выходах Вых.*1 и Вых.*2 нулевые уровни статических напряжений независимо от статических параметров этих дополнительных буферных усилителей 19 и 20 и сопротивлений низкоомной нагрузки. В схеме фиг.2 в низкоомной нагрузке Rн, включенной между выходами Вых.*1 и Вых.*2, могут быть получены значительно большие мощности, которые определяются свойствами дополнительных буферных усилителей 19 и 20. Кроме этого, в архитектуре рис.2 максимальные амплитуды выходных напряжений положительной отрицательной полярностей близки к сумме напряжений первого 5 (Е5) и второго 13 (Е13) источников питания , что является одной из ее замечательных особенностей.

Таким образом, предлагаемый ДУ имеет существенные преимущества в сравнении с прототипом.

Источники информации:

1. Патентная заявка США №2005/0218983

2. Патентная заявка США №2006/0139098

3. Патентная заявка США №2006/0006910 fig. 1

4. Патент США №6.657.465

5. Патент США №6.831.513 fig. 4

6. Патент США №6.844.781

7. Патентная заявка США №2008/0032656 fig.6

8. Патент США №6.657.465

9. Патент США №6.538.513

10. Патентная заявка США №2003/0132803 fig.4

11. Патент США №6.882.185 fig. 4

Дифференциальный операционный усилитель с парафазным выходом, содержащий входной дифференциальный каскад (1) с первым (2) и вторым (3) токовыми выходами и низкоомным выходом (4) общей эмиттерной цепи, связанным с шиной первого (5) источника питания через первый (6) токостабилизирующий двухполюсник, первое (7) токовое зеркало, вход которого подключен к первому (2) токовому выходу входного дифференциального каскада (1), а выход соединен с первым (8) вспомогательным выходом устройства и через первый (9) токостабилизирующий двухполюсник нагрузки соединен с шиной первого (5) источника питания, второе (10) токовое зеркало, вход которого соединен со вторым (3) токовым выходом входного дифференциального каскада (1), а выход соединен со вторым (11) вспомогательным выходом устройства и через второй (12) токостабилизирующий двухполюсник нагрузки соединен с шиной первого (5) источника питания, причем шина второго (13) источника питания связана с общими эмиттерными выходами первого (7) и второго (10) токовых зеркал, отличающийся тем, что в схему введен дополнительный транзистор (14), эмиттер которого соединен с низкоомным выходом (4) общей эмиттерной цепи входного дифференциального каскада (1), а коллектор подключен к шине второго (13) источника питания, причем первый (8) вспомогательный выход устройства связан с базой дополнительного транзистора (14) через последовательно соединенные первый (19) дополнительный буферный усилитель и первый (15) резистор обратной связи, а второй (11) вспомогательный выход устройства связан с базой дополнительного транзистора (14) через последовательно соединенные второй (20) дополнительный буферный усилитель и второй (16) резистор обратной связи.